Werbung

In der vergangenen Woche gewährte Intel erste Einblicke in die nächste Prozessoren-Generation Alder Lake und die ambitionierten Pläne im Bereich einer dedizierten GPU auf Basis von Xe-HPG, die als Intel Arc Anfang 2022 auf den Markt kommen sollen.

Doch auf dem Architecture Day 2021 sprach Intel auch über die nächste Xeon-Generation Sapphire Rapids sowie die Ambitionen im HPC-Bereich, den Xe-HPC bzw. den Ponte-Vecchio-Beschleuniger mit einem riesigen Tile-Design und einem aufwändigen Packaging. Zusätzliche Informationen gab es auf der Hot-Chips-Konferenz und so wollen wir das, was zu Ponte Vecchio und Sapphire Rapids bekannt ist, einmal zusammenfassen.

Nächste Xeon-Generation Sapphire Rapids

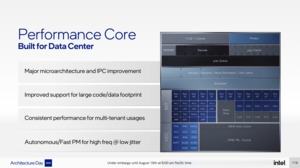

Bisher ließ Intel die wenigen Informationen zu Sapphire Rapids eher langsam herauströpfeln. Doch zum Architecture Day gab es einen ganzen Schwung an Informationen. So setzt die nächste Xeon-Generation auf die von Alder Lake bekannten Performance-Cores auf Basis der Golden-Cove-Architektur. Der Vollausbau dieser Kerne bietet alle für den Serverbereich wichtigen Erweiterungen wie AVX-512, AMX (Advanced Matrix Extensions) und FP16.

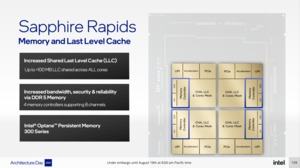

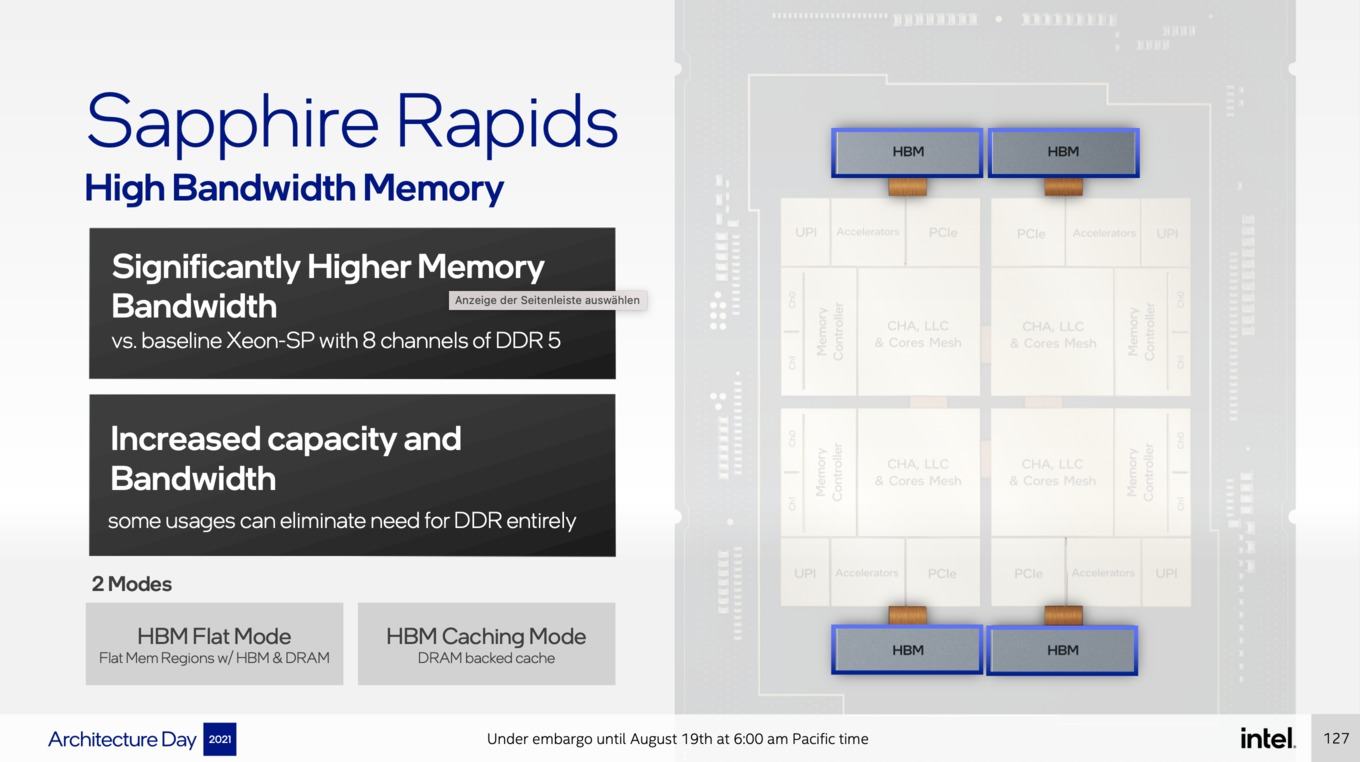

Hinzu kommt ein großer LLC von bis zu 100 MB, der über alle Kerne verfügbar ist. CXL 1.1, DDR5, PCI-Express 5.0 und die optionale Anbindung von HBM sollen Sapphire Rapids an die Spitze des Serverbereichs führen. Intel nennt noch keine konkreten Produkte, spricht dafür aber über das "wie" – also vor allem den Aufbau und die Fertigung.

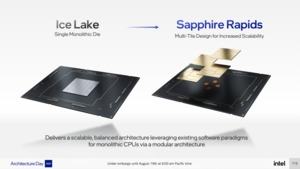

So besteht ein Xeon auf Basis von Sapphire Rapids aus vier Tiles. Jeder dieser Tiles verfügt über die CPU-Kerne, den LCC, einen Speichercontroller für jeweils zwei Speicherkanäle sowie die I/O-Komponenten. Aus vier Tiles zu jeweils zwei Speicherkanälen ergeben sich die insgesamt acht DDR5-Speicherkanäle, die durch Sapphire Rapids unterstützt werden. Nur wenn alle vier Tiles vorhanden und aktiv sind, kann Intel acht Speicherkanäle anbieten. Wie viele Kerne pro Tile aktiv sind, bestimmt, um welches Modell des Xeon-Prozessors es sich handelt.

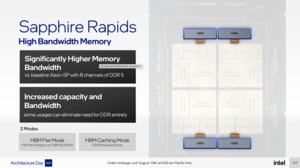

Einige Modelle will Intel mit HBM ausstatten. Dies hat man bereits vor einigen Wochen offiziell bestätigt. Vier Speicherstacks plant Intel einzusetzen, über deren Kapazität oder Bandbreite spricht der Hersteller aber noch nicht. Immerhin bestätigte man nun, dass der HBM in zwei Modi betrieben werden kann: Im HBM Flat Mode ist kein Arbeitsspeicher notwendig. Alle Daten werden im HBM vorgehalten. Im HBM Caching Mode fungiert der HBM als Zwischenspeicher zum DDR5-Speicher.

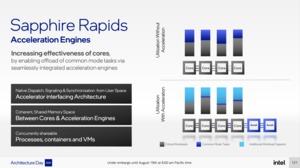

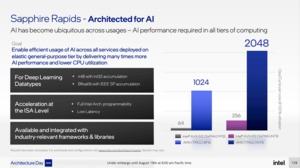

Zusammen mit den AVX-512- und AMX-Funktionseinheiten soll der schnelle HBM dafür sorgen, dass die Xeon-Prozessoren in AI-Anwendungen deutlich schneller werden. Aber auch den konventionellen Anwendungsbereich will man deutlich beschleunigt haben. Um bis zu 69 % soll Sapphire Rapids schneller sein als Cascade Lake.

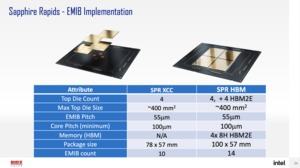

Gefertigt werden die Xeon-Prozessoren auf Basis von Sapphire Rapids in Intel 7, was vormals als 10nm Enhanced SuperFin bezeichnet wurde. Ein XCC (Extreme Core Count) Chip kommt auf eine Fläche von 400 mm². Von diesen sind wie gesagt vier auf einem Package unterbracht, was den riesigen Chip auf 1.600 mm² bringt. Zehn EMIB-Verbindungen (Embedded Multi-die Interconnect Bridge) verbinden die vier Tiles miteinander. Es gibt hier also eine ungleiche Anbindung zwischen den Tiles: 2x2 und 2x3 Verbindungen unserer Recherche nach.

Kommen die vier HBM-Speicherchips dazu, verwendet Intel 14 EMIB-Verbindung – jeweils eine zusätzlich für jeweils einen HBM-Stack. Intel macht unterschiedliche Angaben zur Package-Größe, den bisherigen Informationen nach aber sollen beide Varianten den gleichen Sockel verwenden und sozusagen austauschbar einsetzbar sein.

Im ersten Quartal 2022 sollen die Sapphire-Rapids-Prozessoren auf den Markt kommen. Zur gegebenen Zeit wird Intel dann auch weitere Details zu den Modellen nennen, die erscheinen werden.

HPC-Beschleuniger Ponte Vecchio

Der HPC-Beschleuniger Ponte Vecchio ist Intels aktuelles Prestige-Projekt. Auch hier gab es schon vereinzelt Informationen, aber noch kein Gesamtbild. Zumindest teilweise lüftete Intel nun den Vorhang – vor allem zum Aufbau des Beschleunigers.

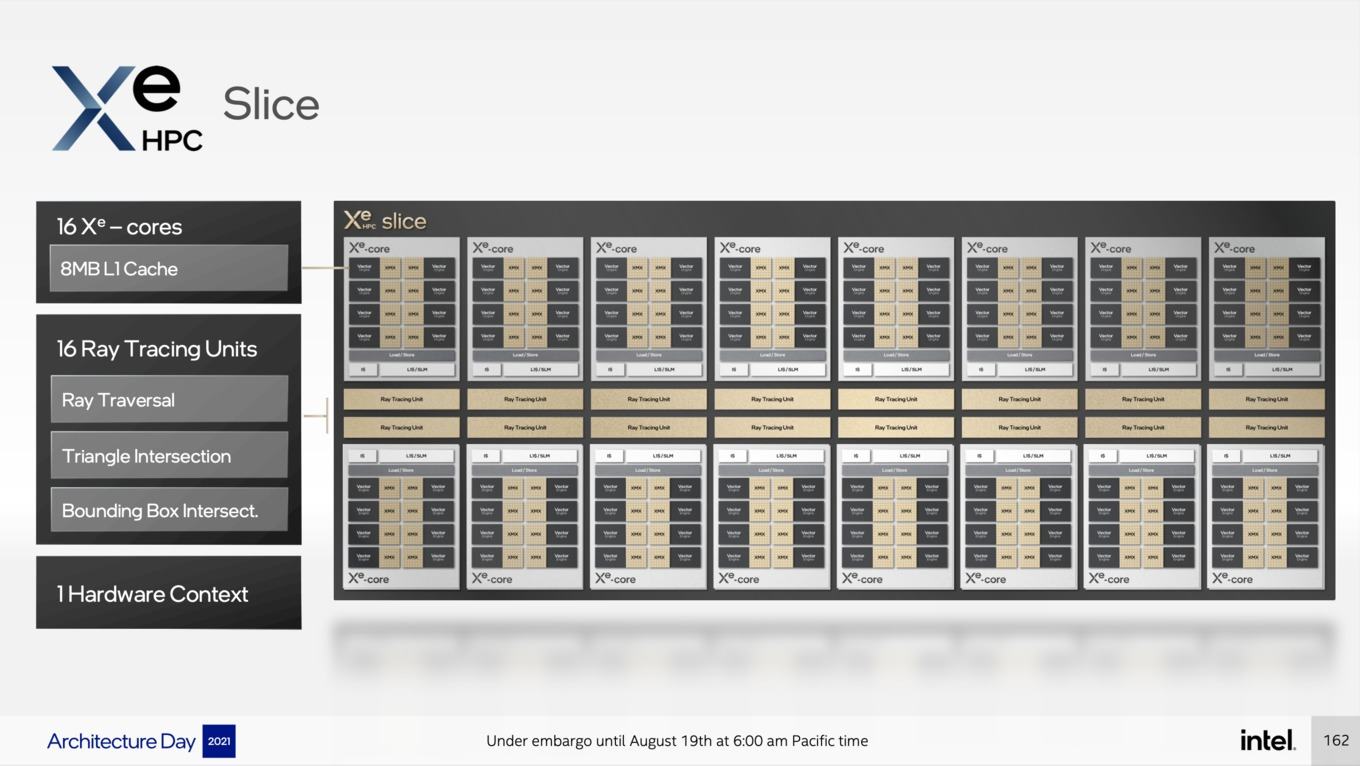

Dieser verwendet als untersten Block die Xe-Cores. Dabei handelt es sich um eine für HPC-Anwendungen angepasste Variante der Xe-Architektur (Xe-HPC). Pro Xe-Core vorhanden sind acht Vektor-Einheiten (512 Bit breit) und acht Matrix-Engines (4.096 Bit). Der L1-Cache pro Xe-Core bemisst 512 kB. Je nach Eingabegröße können die Vektor-Einheiten 256 oder 512 Operationen pro Takt ausführen (256 FFP32 und FP64 oder 512 FP16). Bei den Matrix-Engines sind es 2.048 (TF32), 4.096 (FP16 und BF16) oder 8.192 (INT8).

In einer darüberliegenden Ebene sind die Xe-Cores in Slices aufgeteilt. 16 Xe-Cores ergeben einen Slice, der dann auch die Raytracing-Einheiten beihaltet, die für die Xe-HPG-GPU interessant sind. Ein Stack besteht wiederum aus vier Slices. Der Stack umfasst auch den L2-Cache sowie im Falle von Xe-HPC auch vier HBM2E-Speichercontroller und acht Xe-Links, um mehrere Stacks miteinander zu verbinden. Derzeit plant Intel zwei Stacks direkt zusammenzubringen. Eine Variante mit vier Stacks ist zwar theoretisch denkbar, konkret umgesetzt wird Ponte Vecchio aber mit zwei Stacks.

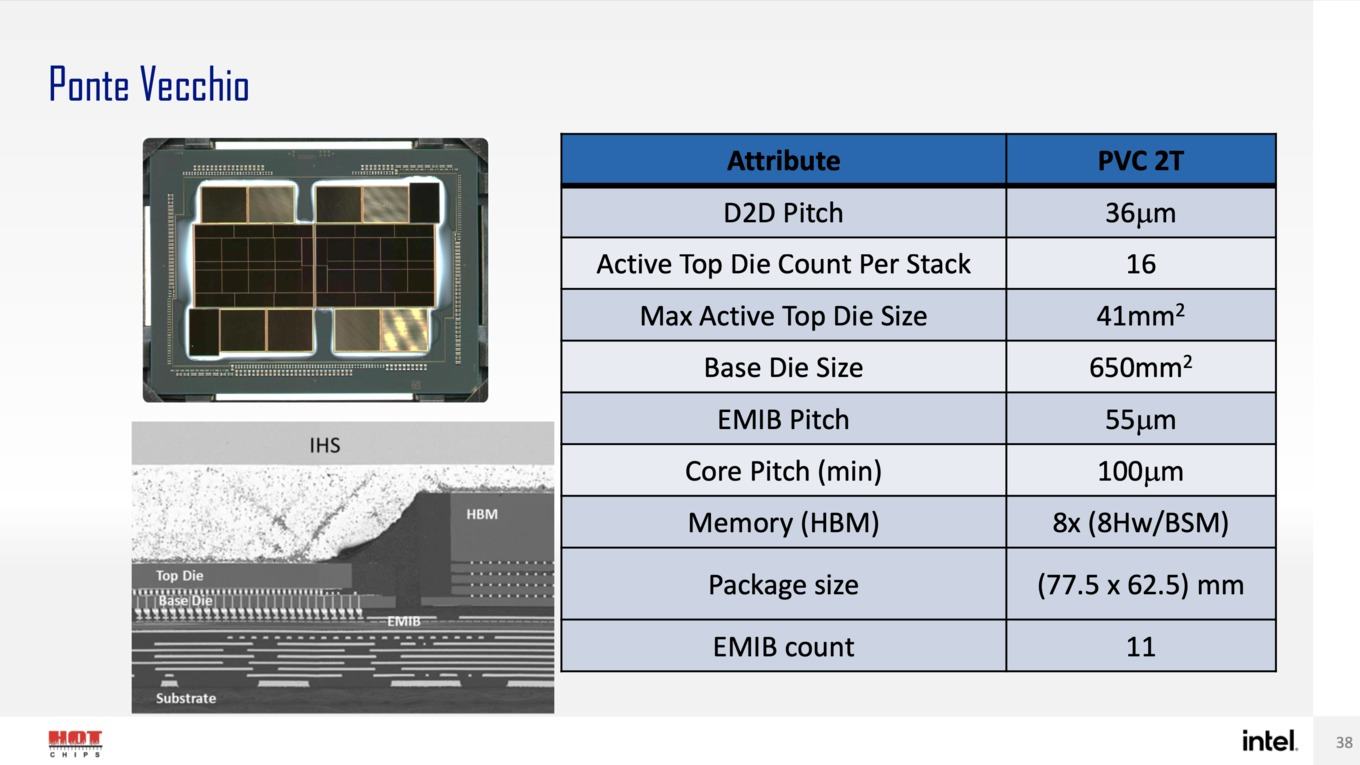

Der Aufbau des Packages ist als komplex zu bezeichnen. So haben wir die Compute Tiles mit den Slices und einen Rambo-Cache, der zwischen den Slices eingesetzt und mittels Foveros angebunden wird. Dies alles sitzt wiederum auf einem Base Tile.

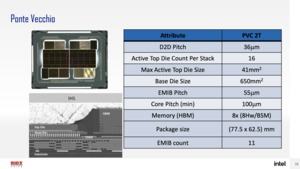

Weitere Tiles sind die eben erwähnten Xe-Links sowie der HBM. EMIB-Verbindungen stellen hier die notwendige Kommunikationsebene her. All das muss auf dem Multi Tile Package untergebracht werden. Insgesamt sprechen wir von 47 aktiven Tiles, die in fünf unterschiedlichen Prozessen hergestellt werden.

Konkret nennt Intel die Compute Tiles, die in 5 nm bei TSMC hergestellt werden. Der Base Tile wird von Intel in Intel 7 (10nm Enhanced SuperFin) gefertigt. Der Xe Link Tile kommt wiederum von TSMC, dieses mal aber in 7 nm. Noch nicht geäußert hat sich Intel zum Rambo Cache und wie dieser gefertigt wird. Bisher geht man auch hier von Intel 7 an. Hinzu kommt der HBM2E, der von Samsung oder SK Hynix kommt und hier ebenfalls in einer bestimmten Fertigungsgröße hergestellt wird.

Bezüglich des Packaging sprach Intel im Rahmen der Hot Chips über die Anzahl der EMIB- und Foveros-Verbindungen. Die 2-Stack-Variante kommt auf 11 EMIB-Verbindungen (fünf pro Stack, 4x HBM + 1x Xe Link) und eine zwischen den beiden Stacks. Aufgrund der Anbindung des Slices auf einem Stack kommen gleich 16 Foveros-Verbindungen pro Stack zum Einsatz.

Genau wie zu Sapphire Rapids fehlt es noch an Details zu Ponte Vecchio. Der Architecture Day ist für Intel die Plattform die grundlegende Architektur und den Aufbau zu erläutern. Sobald die Prozessoren und HPC-Beschleuniger "erhältlich" sind, wird es sicherlich noch weitere Angaben dazu geben.