News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Hot Chips

-

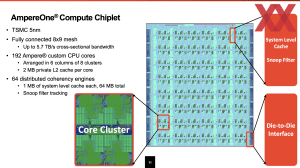

5 nm, HBM3E und aufwändiges Packaging: Hersteller protzen mit High-End-Chips

Nicht kleckern, sondern klotzen – so könnte das Motto der diesjährigen Hot-Chips-Konferenz lauten. Die Hersteller überbieten sich mit immer größeren und letztendlich auch schnelleren Chips, doch der Aufwand der betrieben wird ist ebenfalls enorm. Über NVIDIAs Blackwell-GPU haben wir ebenfalls bereits berichtet wie über den Telum II von IBM, der mit gigantischen Caches aufwarten kann. Auch Intels Xeon 6 SoC alias Granite Rapids-D ist mit zwei... [mehr]

Nicht kleckern, sondern klotzen – so könnte das Motto der diesjährigen Hot-Chips-Konferenz lauten. Die Hersteller überbieten sich mit immer größeren und letztendlich auch schnelleren Chips, doch der Aufwand der betrieben wird ist ebenfalls enorm. Über NVIDIAs Blackwell-GPU haben wir ebenfalls bereits berichtet wie über den Telum II von IBM, der mit gigantischen Caches aufwarten kann. Auch Intels Xeon 6 SoC alias Granite Rapids-D ist mit zwei... [mehr] -

NVIDIA Blackwell: Neue Datenformate sorgen für mehr Leistung in den Tensor-Kernen

Im Vorfeld der Hot Chips 2024 sprach NVIDIA bereits über die Blackwell-Infrastruktur in Form des NVLink-Interconnects und der dazugehörigen Switches. Auf der Konferenz selbst verriet NVIDIA etwas mehr zur Blackwell-Architektur bzw. der darin verbauten Tensor-Kerne. Diese können zwar weiterhin auch große Matrizen in einem Durchlauf berechnen, mit Hilfe neuer Datenformate wird der Durchsatz aber deutlich erhöht. Durch ein neues... [mehr]

Im Vorfeld der Hot Chips 2024 sprach NVIDIA bereits über die Blackwell-Infrastruktur in Form des NVLink-Interconnects und der dazugehörigen Switches. Auf der Konferenz selbst verriet NVIDIA etwas mehr zur Blackwell-Architektur bzw. der darin verbauten Tensor-Kerne. Diese können zwar weiterhin auch große Matrizen in einem Durchlauf berechnen, mit Hilfe neuer Datenformate wird der Durchsatz aber deutlich erhöht. Durch ein neues... [mehr] -

Granite Rapids-D: Intel spricht über den Xeon-6-SoC

Bereits im Februar dieses Jahres nannte Intel erstmals eine Network- und Edge-Variante der Xeon-6-Prozessoren. Granite Ridge-D verwendet dabei Performance-Kerne und kombiniert diese mit einer schnellen Ethernet-Anbindung, PCIe/CXL-Lanes und den bekannten Beschleunigern. Es wird der dritte und letzte Schritt in der Xeon-6-Strategie sein, die im zweiten Quartal mit der Xeon-6700E-Serie (Xeon 6E, Siera Forrest-SP), bzw. den kleinsten... [mehr]

Bereits im Februar dieses Jahres nannte Intel erstmals eine Network- und Edge-Variante der Xeon-6-Prozessoren. Granite Ridge-D verwendet dabei Performance-Kerne und kombiniert diese mit einer schnellen Ethernet-Anbindung, PCIe/CXL-Lanes und den bekannten Beschleunigern. Es wird der dritte und letzte Schritt in der Xeon-6-Strategie sein, die im zweiten Quartal mit der Xeon-6700E-Serie (Xeon 6E, Siera Forrest-SP), bzw. den kleinsten... [mehr] -

Hot Chips 33: Esperanto ET-SoC-1 ist der Inferencing-Effizienz-König

Machine-Learning, bzw. AI-Anwendungen lassen sich in zwei Bereiche aufteilen. Im Training werden verschiedenste Eingabewerte so verarbeitet, dass sie über das Inferencing schnell wieder ausgewertet werden können. Für das autonome Fahren werden Videodaten ausgewertet und ein Netzwerk trainiert, damit die Erkennung der verschiedenen Situationen verbessert wird. Im Inferencing wird das Erlernte dann über die lokalen Systeme in den Fahrzeugen nur... [mehr]

Machine-Learning, bzw. AI-Anwendungen lassen sich in zwei Bereiche aufteilen. Im Training werden verschiedenste Eingabewerte so verarbeitet, dass sie über das Inferencing schnell wieder ausgewertet werden können. Für das autonome Fahren werden Videodaten ausgewertet und ein Netzwerk trainiert, damit die Erkennung der verschiedenen Situationen verbessert wird. Im Inferencing wird das Erlernte dann über die lokalen Systeme in den Fahrzeugen nur... [mehr] -

Hot Chips 33: Wie die GC200 Colossus Mk2 IPU zusammengesetzt ist

Im Sommer des vergangenen Jahres stellte Graphcore die Colossus Mk2 GC200 IPU vor. Der Name ist hier Programm, denn mit 59,4 Milliarden Transistoren auf 823 mm² kann man wirklich von einem Chip-Koloss sprechen. Die letzen Leistungsdaten von MLPerf sahen Graphcore auch auf gutem Wege, wenngleich man hier sagen muss, dass bei weitem nicht alle Versprechungen eingehalten werden konnten. Uns interessierte der Vortrag auf der Hot-Chips-Konferenz... [mehr]

Im Sommer des vergangenen Jahres stellte Graphcore die Colossus Mk2 GC200 IPU vor. Der Name ist hier Programm, denn mit 59,4 Milliarden Transistoren auf 823 mm² kann man wirklich von einem Chip-Koloss sprechen. Die letzen Leistungsdaten von MLPerf sahen Graphcore auch auf gutem Wege, wenngleich man hier sagen muss, dass bei weitem nicht alle Versprechungen eingehalten werden konnten. Uns interessierte der Vortrag auf der Hot-Chips-Konferenz... [mehr] -

Hot Chips 33: Samsung Aquabolt-XL - HBM2 mit integrierter Rechenkapazität

Anfang des Jahres stellte Samsung den HBM-PIM, den ersten HBM-Speicher mit eingebauter AI-Engine, vor. Einige Details kennen wir also bereits, auf der Hot-Chips-Konferenz sprach Samsung aber etwas genauer über die Motivation und die Ziele hinter einem solchen Speichertyp. Auch hat man bereits erste Produkte mit diesem Speicher ausgestattet und testet diese zusammen mit seinen potenziellen Kunden. Beim Aquabolt-XL handelt es sich um... [mehr]

Anfang des Jahres stellte Samsung den HBM-PIM, den ersten HBM-Speicher mit eingebauter AI-Engine, vor. Einige Details kennen wir also bereits, auf der Hot-Chips-Konferenz sprach Samsung aber etwas genauer über die Motivation und die Ziele hinter einem solchen Speichertyp. Auch hat man bereits erste Produkte mit diesem Speicher ausgestattet und testet diese zusammen mit seinen potenziellen Kunden. Beim Aquabolt-XL handelt es sich um... [mehr] -

Hot Chips 33: Intel verrät mehr Details zum Thread Director für Alder Lake

Die ersten tieferen Einblicke in das Hybrid-Design der Alder-Lake-Prozessoren nannten auch erste Details zum neuen Thread Director, der die Aufgabenverteilung der Prozesse auf die Performance- und Effizienz-Kerne optimieren soll. Im Rahmen einer Präsentation auf der Hot Chips 33 gab Intel nun weitere Details zum Thread Director preis, denn für ein hybrides Design steht und fällt alles mit der richtigen Aufteilung der Threads, denn sonst... [mehr]

Die ersten tieferen Einblicke in das Hybrid-Design der Alder-Lake-Prozessoren nannten auch erste Details zum neuen Thread Director, der die Aufgabenverteilung der Prozesse auf die Performance- und Effizienz-Kerne optimieren soll. Im Rahmen einer Präsentation auf der Hot Chips 33 gab Intel nun weitere Details zum Thread Director preis, denn für ein hybrides Design steht und fällt alles mit der richtigen Aufteilung der Threads, denn sonst... [mehr] -

Hot Chips 33: Synopsys will komplette Chipentwicklung per AI anbieten

Moderne Chipdesigns sind unglaublich komplex. Mehr als 50 Milliarden Transistoren kann ein moderner Chip umfassen. Eine Architektur und einzelne IP-Blöcke sind in der Theorie vergleichsweise schnell entwickelt, diese dann aber fertigen zu können, ist eine ganz andere Aufgabe und kann zu großen Problemen führen. Anbieter sogenannter EDA-Werkzeuge (Electronic Design Automation) haben sich darauf spezialisiert, den Prozess eines Designs in die... [mehr]

Moderne Chipdesigns sind unglaublich komplex. Mehr als 50 Milliarden Transistoren kann ein moderner Chip umfassen. Eine Architektur und einzelne IP-Blöcke sind in der Theorie vergleichsweise schnell entwickelt, diese dann aber fertigen zu können, ist eine ganz andere Aufgabe und kann zu großen Problemen führen. Anbieter sogenannter EDA-Werkzeuge (Electronic Design Automation) haben sich darauf spezialisiert, den Prozess eines Designs in die... [mehr] -

Hot Chips 33: Intel über Xe-HPC Ponte Vecchio und Sapphire Rapids

In der vergangenen Woche gewährte Intel erste Einblicke in die nächste Prozessoren-Generation Alder Lake und die ambitionierten Pläne im Bereich einer dedizierten GPU auf Basis von Xe-HPG, die als Intel Arc Anfang 2022 auf den Markt kommen sollen. Doch auf dem Architecture Day 2021 sprach Intel auch über die nächste Xeon-Generation Sapphire Rapids sowie die Ambitionen im HPC-Bereich, den Xe-HPC bzw. den Ponte-Vecchio-Beschleuniger mit einem... [mehr]

In der vergangenen Woche gewährte Intel erste Einblicke in die nächste Prozessoren-Generation Alder Lake und die ambitionierten Pläne im Bereich einer dedizierten GPU auf Basis von Xe-HPG, die als Intel Arc Anfang 2022 auf den Markt kommen sollen. Doch auf dem Architecture Day 2021 sprach Intel auch über die nächste Xeon-Generation Sapphire Rapids sowie die Ambitionen im HPC-Bereich, den Xe-HPC bzw. den Ponte-Vecchio-Beschleuniger mit einem... [mehr] -

Hot Chips 33: AMD nennt weitere Details zum 3D V-Cache

Zur Computex AnfangJuni nannte AMD die ersten Details zum 3D V-Cache, der den L3-Cache der Prozessoren um ein vielfaches vergrößern können soll. In einem ersten Schritt kann AMD damit den L3-Cache pro CCD um den Faktor drei erhöhen. Mit weiteren Stapeln wären aber noch deutlich größere Steigerungen möglich. Der 3D V-Cache ist AMDs Lösung für den Bedarf nach immer größerem und schnellem Speicher möglichst nahe an den CPU-Kernen. AMD fertigt... [mehr]

Zur Computex AnfangJuni nannte AMD die ersten Details zum 3D V-Cache, der den L3-Cache der Prozessoren um ein vielfaches vergrößern können soll. In einem ersten Schritt kann AMD damit den L3-Cache pro CCD um den Faktor drei erhöhen. Mit weiteren Stapeln wären aber noch deutlich größere Steigerungen möglich. Der 3D V-Cache ist AMDs Lösung für den Bedarf nach immer größerem und schnellem Speicher möglichst nahe an den CPU-Kernen. AMD fertigt... [mehr] -

Hot Chips 33: Samsung stapelt dünne DDR5-Lagen für 512-GB-Module

Der Einsatz von DDR5 soll die zur Verfügung stehende Bandbreite und Kapazitäten deutlich erhöhen. Dazu sollen die Module eine Einzelkapazität von bis zu 512 GB erreichen. Damit ließe sich die Lücke schließen, die moderne Serversysteme hinsichtlich der Kapazität offenbaren, denn zwar unterstützen die Prozessoren von AMD und Intel bis zu 4 TB DDR-Speicher pro Sockel, DDR4-Module mit 256 GB gibt es aber quasi nicht. Intel hat dies... [mehr]

Der Einsatz von DDR5 soll die zur Verfügung stehende Bandbreite und Kapazitäten deutlich erhöhen. Dazu sollen die Module eine Einzelkapazität von bis zu 512 GB erreichen. Damit ließe sich die Lücke schließen, die moderne Serversysteme hinsichtlich der Kapazität offenbaren, denn zwar unterstützen die Prozessoren von AMD und Intel bis zu 4 TB DDR-Speicher pro Sockel, DDR4-Module mit 256 GB gibt es aber quasi nicht. Intel hat dies... [mehr] -

AMD provoziert Gerüchte rund um Raven Ridge in 7 nm (Update)

In der Öffentlichkeit geht das jährlich stattfindene Symposium Hot Chips oftmals unter. Dabei gewähren Unternehmen dabei oftmals sehr tiefe Einblicke in ihre Technologien - so wie beispielsweise AMD auf der diesjährigen Veranstaltung. Dabei ging es im Wesentlichen um die Unterschiede zwischen Zen und Zen+. Allerdings hat das Unternehmen damit Spekulationen rund um die Raven-Ridge-APUs ausgelöst. Während des Vortrags, den... [mehr]

In der Öffentlichkeit geht das jährlich stattfindene Symposium Hot Chips oftmals unter. Dabei gewähren Unternehmen dabei oftmals sehr tiefe Einblicke in ihre Technologien - so wie beispielsweise AMD auf der diesjährigen Veranstaltung. Dabei ging es im Wesentlichen um die Unterschiede zwischen Zen und Zen+. Allerdings hat das Unternehmen damit Spekulationen rund um die Raven-Ridge-APUs ausgelöst. Während des Vortrags, den... [mehr]