Werbung

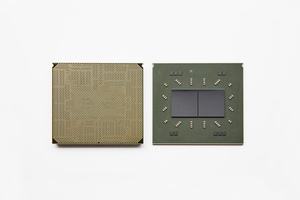

IBM hat mit dem Telum die nächste Generation seiner Z-Chipserie vorgestellt. Allerdings schlägt IBM hier einen anderen Weg ein: Schlanker, dafür aber deutlich flexibler soll die neue Generation sein. Im Herbst 2019 wurde der z15 vorgestellt. 12 Kerne erreichten einen Takt von 5,2 GHz. Der L2-Cache ist hier 4 MB groß, der L3-Cache wurde im Vergleich zum Vorgänger auf 256 MB verdoppelt.

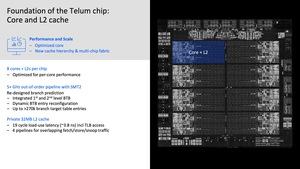

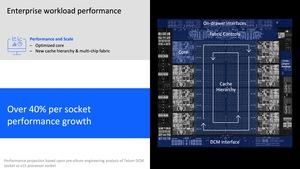

Mit dem Telum stellt IBM einen Prozessor vor, der acht Out-of-Order-Kerne besitzt, die per SMT2 jeweils zwei Threads ausführen können. Das gesamte Design ist auf schnelle Echtzeitanwendungen ausgelegt – entsprechend liegt der Fokus auf der Single-Threaded-Leistung. Dazu sieht IBM auch einen 32 MB großen L2-Cache vor, der zunächst exklusiv jedem CPU-Kern zur Verfügung steht. Auch die Zugriffe auf den L2-Cache sollen dank vier Pipelines und nur 19 Taktzyklen (3,8 ns) für ein komplettes Schreiben des Caches besonders schnell sein.

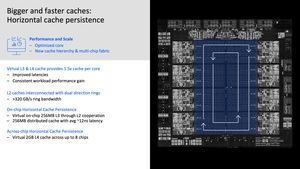

Bei acht Kernen mit jeweils 32 MB an L2-Cache ergibt sich eine Gesamtkapazität von 256 MB, die als kohärenter bzw. virtueller L3-Cache allen Kernen zur Verfügung steht. Ein Ring-Interconnect kommt auf eine Bandbreite von 320 GB/s für Zugriffe auf den L2-Cache eines anderen Kerns. Auf die virtuellen 256 MB an L3-Cache können die Kerne mit einer Latenz von gerade einmal 12 ns zugreifen.

Kommen acht der Telum-Chips in einem Rack zum Einsatz, sind diese ebenfalls miteinander verbunden und können einen virtuellen L4-Cache mit einer Kapazität von bis zu 2 GB bilden.

Als letzte Speicherebene stehen DDR-Speichercontroller zur Verfügung, die acht Speicherkanäle ansprechen. Auch hier sollen die Latenzen möglichst kurz gehalten werden können.

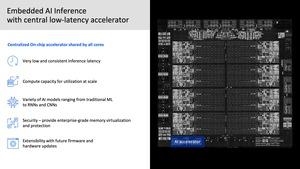

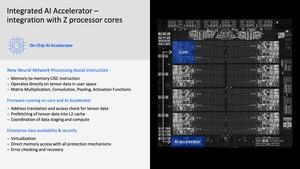

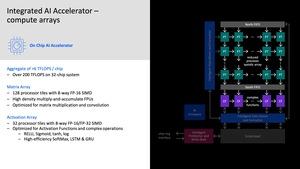

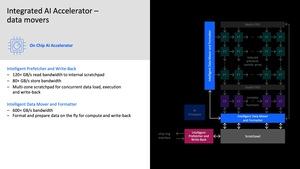

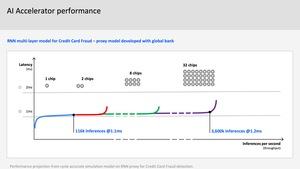

Ebenfalls mit auf dem Telum findet sich ein AI-Beschleuniger, der eine Leistung von 6 TFLOPS für FP16-Berechnungen erreicht. Der AI-Beschleuniger hat direkten Zugriff auf den L2-Cache des Prozessors, so dass Daten mit bis zu 120 GB/s gelesen und mit 80 GB/s geschrieben werden können. Die Daten können aber auch schon vorverarbeitet werden und liegen dann im AI-Beschleuniger selbst vor, was die Bandbreite auf 600 GB/s steigert. Hier steht dann aber nicht mehr die volle Kapazität der 8x 32 MB zur Verfügung.

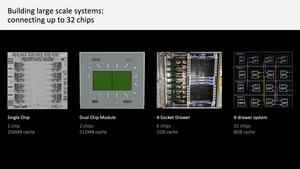

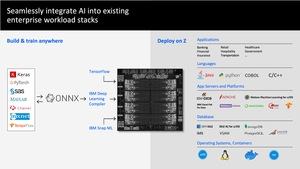

Der IBM Z Telum soll für die verschiedensten Anwendungsbereiche interessant sein. Echtzeitanwendungen aus den unterschiedlichsten Bereichen (Finanzen, Versicherungen, Infrastruktur, ...) stehen hier im Fokus. Skalieren sollen Systeme von einem Chip, über eine angebotene Dual-Die-Variante über Racks mit acht bis 32 Chips.

Gefertigt wird der IBM Z Telum in 7 nm bei Samsung. Bei 22,5 Milliarden Transistoren kommt er auf eine Fläche von 530 mm². Der Prozessor besteht aus 17 Schichten. Der Basis-Takt soll bei etwas mehr als 5 GHz liegen. Genauere Angaben macht IBM nicht.

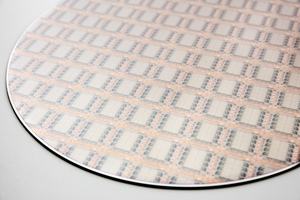

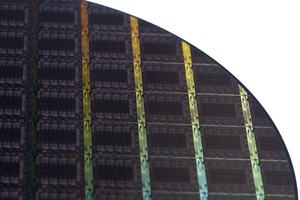

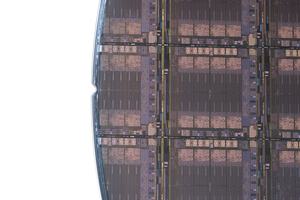

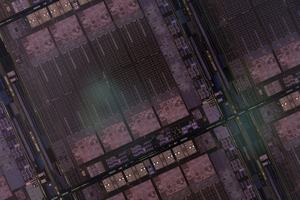

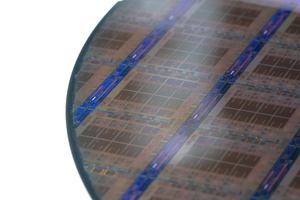

Zum Abschluss noch ein paar schicke Wafer- und Chip-Shots des IBM Z Telum: