Werbung

Im Sommer des vergangenen Jahres stellte Graphcore die Colossus Mk2 GC200 IPU vor. Der Name ist hier Programm, denn mit 59,4 Milliarden Transistoren auf 823 mm² kann man wirklich von einem Chip-Koloss sprechen. Die letzen Leistungsdaten von MLPerf sahen Graphcore auch auf gutem Wege, wenngleich man hier sagen muss, dass bei weitem nicht alle Versprechungen eingehalten werden konnten.

Uns interessierte der Vortrag auf der Hot-Chips-Konferenz vor allem, weil Graphcore über die Fertigung und Auslegung eines solchen Chips sprach. Doch zunächst einmal noch etwas Kontext zum Prozessor:

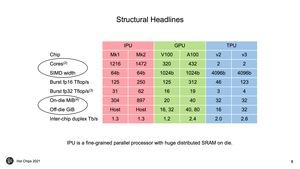

2018 stellte mann die GC2 Colossus Mk1 IPU vor. Diese verfügte über 1.216 Tiles mit den Recheneinheiten und jeweils 256 KB an SRAM. Insgesamt waren 304 MB an SRAM vorhanden, die zusammengenommen auf eine Bandbreite von 62 TB/s kommen. 7,8 TB/s waren zwischen den Tiles möglich, 320 GB/s nach außen hin zu weiteren Chips. Genau 23.647.173.309 aktive Transistoren sollen sich im Chip befunden haben, der in 16 nm bei TSMC gefertigt wurde.

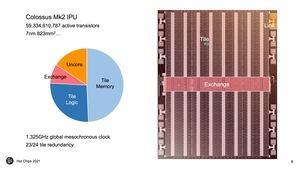

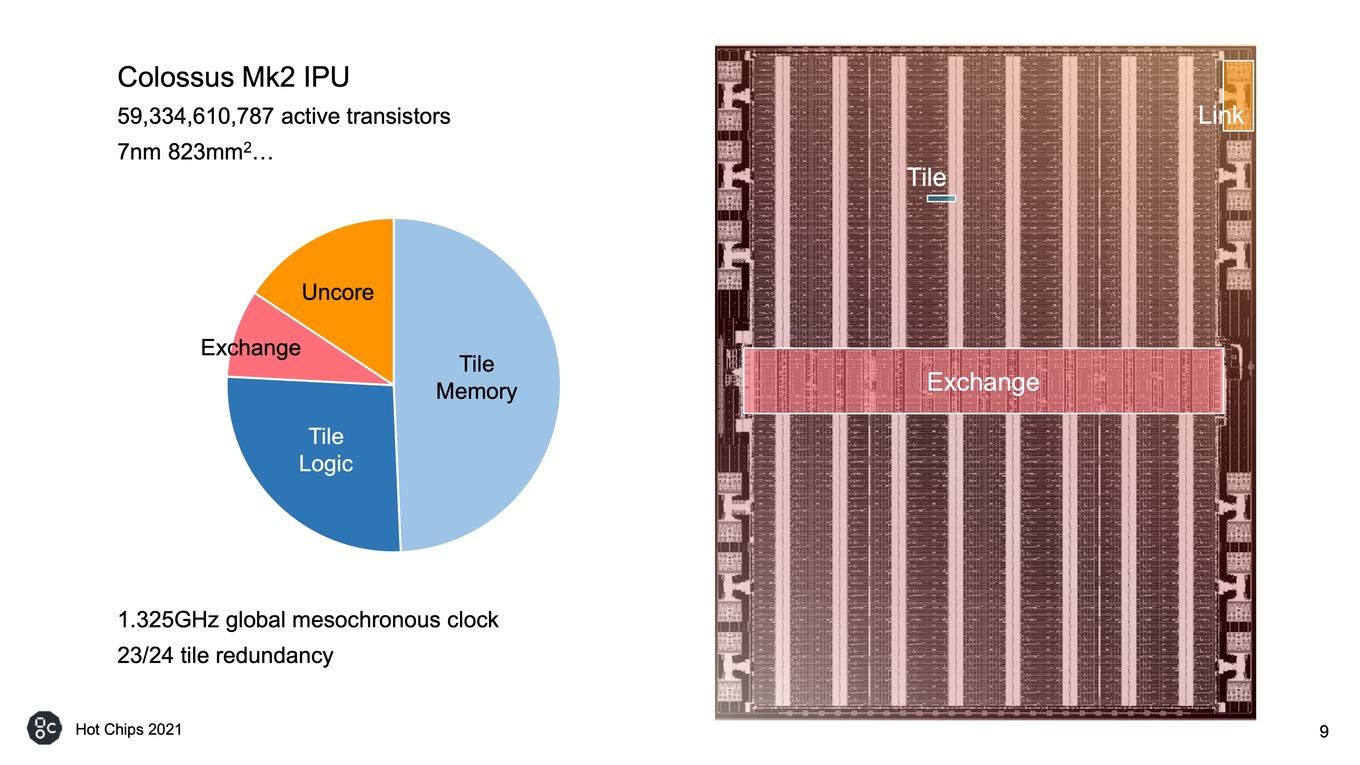

Die zweite Generation alias GC200 Colossus Mk2 kommt auf 1.472 Tiles mit den Recheneinheiten und jeweils 624 KB an SRAM. Die Rechenleistung verdoppelt sich auf 250 TFLOPS. Insgesamt sind 896 MB an SRAM vorhanden. An den Bandbreiten in der Kommunikation hat sich nichts getan. Der viele Speicher blähte den Chip aber auf genau 59.334.610.787 aktive Transistoren auf, die in 7 nm auf eine Chipgröße von 823 mm² kommen.

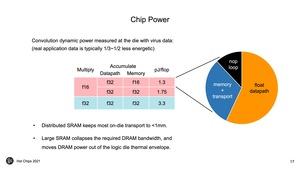

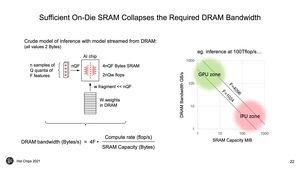

Wo es aber interessant wird, ist der Anteil der Funktionseineiten an der Chipfläche. So entfallen fast 50 % auf den SRAM. Nur etwa 25 % sind für die eigentlichen Recheneinheiten vorgesehen. Die restlichen 25 % teilen sich auf den Uncore-Bereich (externe Links, PHYs) und den Exchange-Bereich auf. Das nur 25 % der Chipfläche von den Recheneinheiten belegt werden, dürfte den ein oder anderen überraschen. Mit der zunehmenden Größe der Caches sind solche Verhältnisse inzwischen aber gar nicht mehr so unüblich.

Um einen solch komplexen Chip fertigen zu können, sind gewisse Redundanzen vorgesehen, denn komplett fehlerfrei sind 59 Milliarden Transistoren auf 823 mm² nicht zu realisieren. Die Redundanz des GC200 Colossus Mk2 liegt laut Graphcore bei 23/24. Demnach sind nur 1.472 von 1.536 Recheneinheiten und damit 95,83 % des Chips aktiv.

Bei den AI-Beschleunigern ist noch nicht zwangsläufig zu erkennen, dass Tile- bzw. Chiplet-Designs in den kommenden Jahren in den Fokus rücken werden. Die Hot Cips 33 zeigt, dass es meist noch große monolithische Chips sind, die hier entwickelt werden. Diese sollen dann zu mehreren Dutzend oder gar mehreren Tausend zusammenarbeiten. Zumindest für die Fertigung in 7 nm ist hier inzwischen ein Limit erreicht, was technisch umsetzbar ist. Mit dem Wechsel auf eine Fertigung in 5 nm wird es spannend zu beobachten sein, welche Größe und Komplexität die Chips erreichen können.