Werbung

Mitte des vergangenen Jahres vermeldete AMD sein eigens gestecktes Ziel um den Faktor 25 effizientere Mobilprozessoren anbieten zu wollen, erfolgreich erreicht zu haben. Mit dem Ryzen 7 4800H hat man das Ziel sogar mit dem Faktor von 31,74 übertroffen.

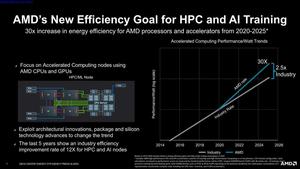

Auch im Serverbereich hat sich AMD nun ein entsprechendes Ziel gesteckt. Bis 2025 sollen Systeme um den Faktor 30 energieeffizienter sein. Schlüsselfaktor für eine um den Faktor 30 höhere Leistung bei gleicher Leistungsaufnahme (darauf sollen sich die Ambitionen aber nicht zwangsläufig zusammenfassen lassen) zu erreichen, sollen spezielle Nodes aus AMD-CPUs und GPU-Beschleunigern sein.

Um das Ziel im Jahre 2025 zu erreichen, muss die Hardware deutlicher schneller als der aktuelle Faktor 2,5 pro Jahr werden. Dies entspricht in etwa dem Durchschnitt der Entwicklung in den vergangenen fünf Jahren. Limitierungen gibt es aufgrund der immer höheren Kosten durch die Fertigung und das Packaging, Limits in der Fertigung immer größerer Dies für CPUs und GPUs sowie durch den Verbrauch der Systeme.

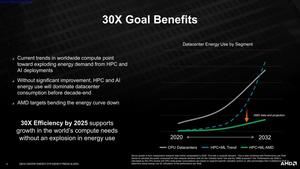

AMD will den Energieverbrauch der Systeme reduzieren und nicht nur bei gleicher Leistungsaufnahme die Performance deutlich steigern. Eine deutliche Steigerung der Leistung im Zusammenspiel mit einer geringen Steigerung der Leistungsaufnahme soll am Ende dazu führen, dass das 30x-Effizienzziel erreicht wird.

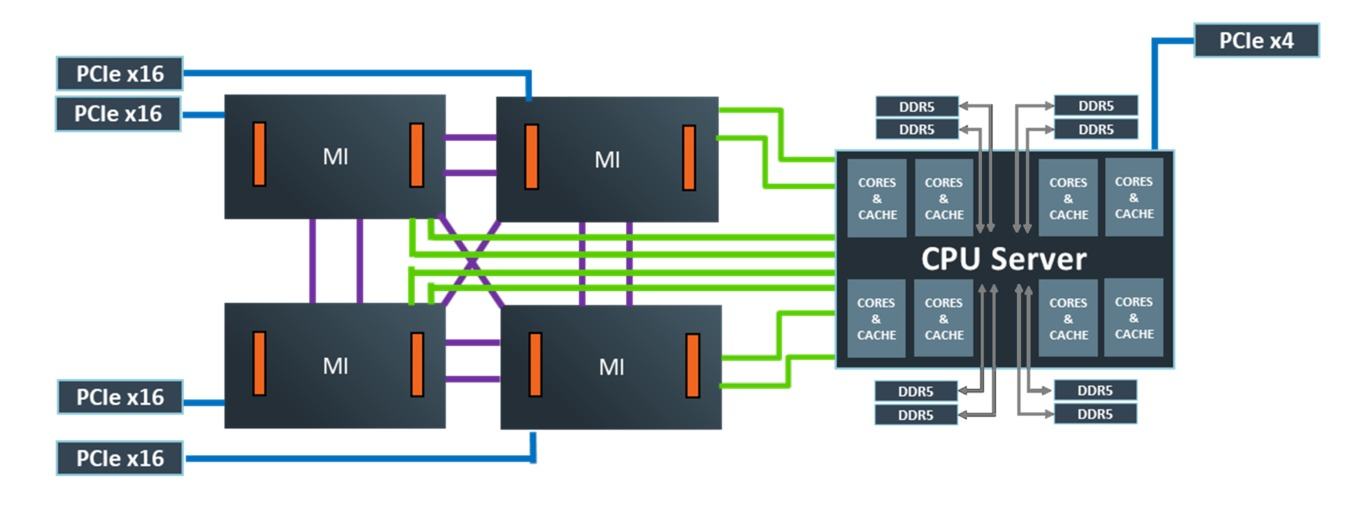

In einer schematischen Darstellung zeigt AMD auch den Aufbau eines Nodes bestehend aus EPYC-Prozessoren und Radeon-Instinct-Beschleuniger. Bereits heute gibt es solche Nodes und die schnellsten Systeme setzen aufgrund der Anbindung über PCI-Express 4.0 auch auf EPYC-Prozessoren. Kommen Radeon-Instinct-Beschleuniger zum Einsatz, sind dieser per Infinity Fabric miteinander verbunden.

In einem nächsten Schritt wird AMD EPYC-Prozessoren vorstellen, welche die GPU-Beschleuniger per Infinity Architecture in der dritten Generation anbinden. Damit sollen die Datenraten einer PCIe-Anbindung deutlich übertroffen werden. Untereinander werden die GPUs sich weiterhin per Infinity Fabric verknüpfen. Die dargestellten PCI-Express-Lanes dienen der Anbindung des Netzwerk-Interface. Da HPE die meisten der zukünftigen AMD-Supercomputer aufbauen wird, werden die Lanes für den Slingshot-Interconnect verwendet werden.

Der dargestellte CPU-Server wird hinsichtlich seiner EPYC-Generation nicht näher beschrieben. Da hier die Rede von DDR5 ist, könnte es sich um die nächste Generation namens Genoa handeln. In den Folien ist die gleiche schematische Darstellung mit DDR4 zu finden. Frontier wird als eines der ersten Exascale-Systeme auf Custom-EPYC-Prozessoren setzen. Diese basieren noch auf dem Milan-Design mit Zen-3-Kernen, DDR4 und PCI-Express 4.0. Eben diese könnten hier abgebildet sein. Frontier soll eine Rechenleistung von 1,5 Exaflops erreichen. El Capitan soll etwas später sogar auf auf mehr als 2 Exaflops kommen und setzt auf eben erwähnte EPYC-Prozessoren auf Basis des Genoa-Designs (Zen 4, DDR5, PCI-Express 5.0). Auf was sich AMD in der Darstellung genau bezieht, bleibt unbekannt.

2025 werden wir dann sehen, ob AMD sein selbst gestecktes Ziel auch erreicht hat. Dafür maßgeblich werden die Ergebnisse der zukünftigen EPYC- und Radeon-Instinct-Generationen sein.

Update:

AMD hat uns kontaktiert und darüber informiert, dass die Nennung von DDR5 in einer der Infografiken ein Fehler war, der in den Folien bereits korrigiert wurde, nicht aber im Blog-Post. Man sollte also nicht allzu viel in das Aufführen von DDR5 hineininterpretieren.