Werbung

Tröpfchenweise lässt Intel Informationen zur nächsten Xeon-Generation an die Öffentlichkeit. Zur Supercomputing 2021 wird nun unter anderem enthüllt, wie groß der optionale HBM-Cache ist, der einigen Modellen spendiert wird. Bereits bekannt war, dass Intel bis zu vier HBM-Speicherchips neben die vier Tiles eines Sapphire-Rapids-Prozessors packen wird. Wie groß die Kapazität dieser Speicherhips sein wird, wusste man noch nicht.

Von bis zu 64 GB HBM2e spricht Intel nun. Jeder der vier Tiles bekommt demnach maximal einen HBM2e zugeteilt. Der HBM2e kann entweder als Zwischenspeicher zum DDR5 betrieben werden (HBM Caching Mode) oder fungiert im HBM Flat Mode als einziger Speicher exklusive der Caches, auf den die Golden-Cove-Kerne zurückgreifen können. Dann ist gar kein DDR5 als Arbeitsspeicher notwendig und alle notwendigen Daten werden im HBM2e vorgehalten.

Das Intel hier nun von "bis zu 64 GB" spricht bedeutet aber auch, dass es Xeon-Prozessoren mit weniger als diesen 64 GB geben wird. Micron und SK Hynix als die einzigen beiden Hersteller für HBM2e bieten diesen mit Kapazitäten von 16 und 8 GB pro Chip an. Demnach dürfte es auch Xeon-Prozessoren mit 32 GB geben oder aber Intel verbaut nicht immer vier Tiles – auch dies wäre eine Möglichkeit.

Aber Intel spricht auch zum aktuellen Zeitpunkt noch nicht über konkrete Modelle, Anzahl der Kerne und die weiteren technischen Daten. Die Architektur der Golden-Cove-Kerne kennen wir aber schon ganz gut. Einen Unterschied zur Desktop-Abwandlung in den Alder-Lake-Prozessoren (siehe unseren Test dazu) gibt es für den L2-Cache, der mit 2 MB etwas größer ausfallen wird und bei Alder Lake nur 1,25 MB pro Kern bemisst. Um die Anzahl der Kerne pro Tile nicht zu verraten, spricht Intel weiterhin von mehr als 100 MB an LLC (Last Level Cache) bzw. L3-Cache.

Für etwas Aufsehen sorgte die Tatsache, dass auch bei Alder Lake die AVX-512-Einheiten funktionieren, wenn man die E-Cores deaktiviert. Laut Intel sollte dies nicht der Fall sein, aber offenbar ist man sich in der finalen Phase der Produktentwicklung nicht ganz einig gewesen, ob AVX-512 auch auf dem Desktop aktiv bleiben soll oder nicht. Für die Xeon-Prozessoren sind die Beschleunigten AVX-512-Berechnungen aber natürlich wichtig.

Die I/O-Funktionen wie CXL 1.1, PCI-Express 5.0 und UPI 2.0 zur Socket-Socket-Kommunikation waren bereits bekannt. Außerdem wird natürlich DDR5 unterstützt, genau wie bei den Alder-Lake-Prozessoren. Aus vier Tiles zu jeweils zwei Speicherkanälen ergeben sich die insgesamt acht DDR5-Speicherkanäle, die durch Sapphire Rapids angesprochen werden können. Nur wenn alle vier Tiles vorhanden und aktiv sind, kann Intel acht Speicherkanäle anbieten.

Gefertigt werden die Xeon-Prozessoren auf Basis von Sapphire Rapids in Intel 7, was vormals als 10nm Enhanced SuperFin bezeichnet wurde. Ein XCC (Extreme Core Count) Chip kommt auf eine Fläche von 400 mm² - dies hatte man auf der HotChips 33 verraten. Bei vier Tiles in einem Package sprechen wir von insgesamt 1.600 mm² an Chipfläche, ohne die HBM2e-Chips mit einzubeziehen. Zehn EMIB-Verbindungen (Embedded Multi-die Interconnect Bridge) verbinden die vier Tiles miteinander. Es gibt hier also eine ungleiche Anbindung zwischen den Tiles: 2x2 und 2x3 Verbindungen unserer Recherche nach. Kommen die vier HBM-Speicherchips dazu, verwendet Intel 14 EMIB-Verbindung – jeweils eine zusätzlich für jeweils einen HBM-Stack. Nach außen hin stellt sich das System wie ein monolithischer Prozessor dar.

Xeon mit HBM2e als Konter zu EPYC mit 3D V-Cache

Immer größere Speicher näher an die Rechenkerne zu bringen, ist eine der Maßnahmen die Rechenleistung der Prozessoren zu erhöhen. AMD stellte in der vergangenen Woche die EPYC-Prozessoren mit 3D V-Cache alias Milan-X vor. Diese bieten einen bis zu 768 MB großen L3-Cache – verteilt auf acht CCDs. Die Zen-3-Kerne können mit 650 GB/s für das Schreiben und knapp 1.000 GB/s für das Lesen von Daten auf den eigenen (CCD intern) L3-Cache Schreiben bzw. davon lesen.

Ein HBM2e-Speicher kommt auf eine Speicherbandbreite von bis zu 460 GB/s. Bei vier Speicherchips kämen die Sapphire-Rapids-Prozessoren auf 1.840 GB/s über alle vier Tiles hinweg. In Kapazität und Bandbreite scheint Intel mit den Sapphire-Rapids-Prozessoren mit HBM2e also der Konkurrenz durchaus etwas entgegenzusetzen zu haben. Ob dies auch im Hinblick auf die Anzahl der Kerne und der Gesamtleistung gilt, wird sich aber noch zeigen müssen.

Sapphire Rapids + Ponte Vecchio

Die Xeon-Prozessoren auf Basis von Sapphire Rapids sind einer von zwei Bausteinen in Intels HPC-Strategie. Der zweite sind die Ponte-Vecchio-Beschleuniger, zu denen es aber keinerlei neue Informationen gibt. Wir verweisen daher auf die bisherige Berichterstattung.

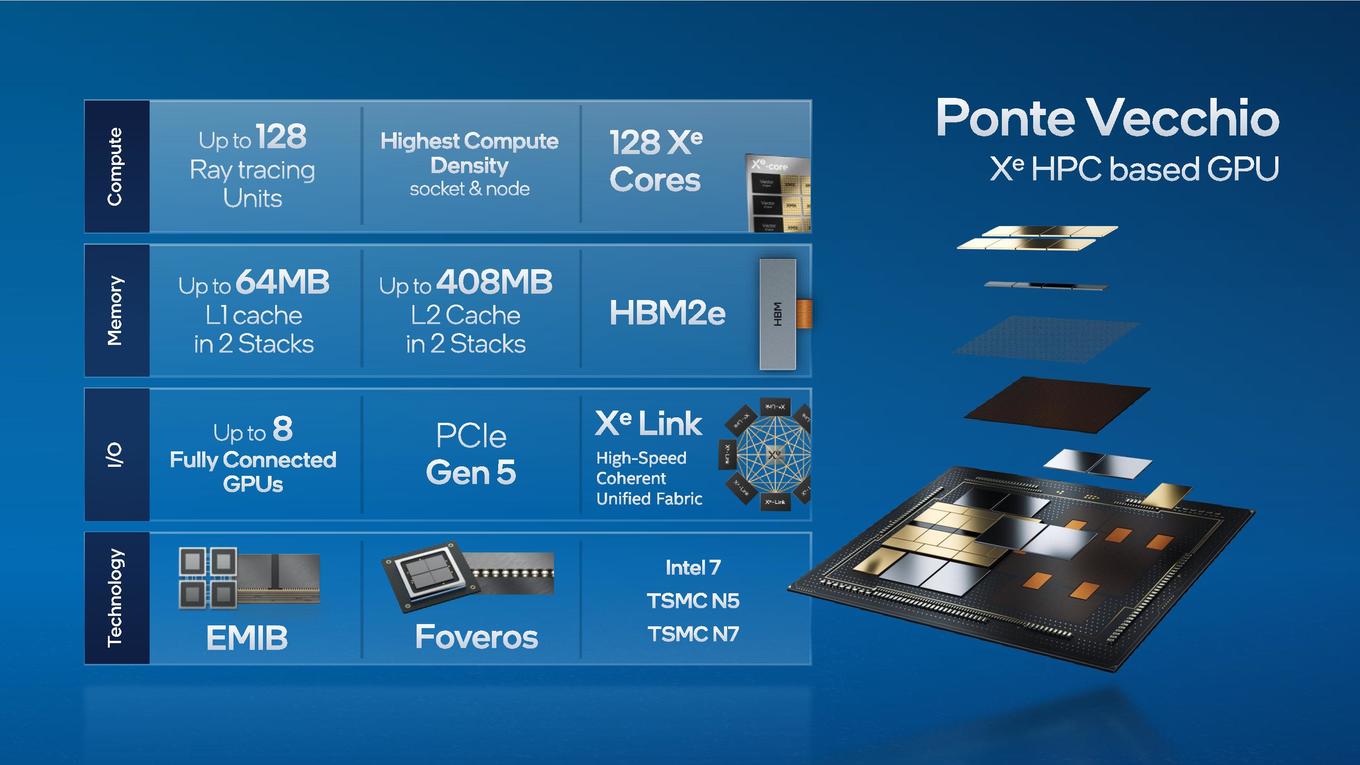

Ponte Vecchio ist Intels aktuelle Flaggschiff-Umsetzung im Bereich das Packaging. Die 2-Stack-Variante kommt auf 11 EMIB-Verbindungen (fünf pro Stack, 4x HBM + 1x Xe Link) und eine zwischen den beiden Stacks. Aufgrund der Anbindung des Slices auf einem Stack kommen gleich 16 Foveros-Verbindungen pro Stack zum Einsatz.

Die verschiedenen Tiles basieren auf unterschiedlichen Fertigungsgrößen und werde teilweise extern gefertigt. Die Compute Tiles werden in 5 nm bei TSMC hergestellt. Der Base Tile wird von Intel in Intel 7 (10nm Enhanced SuperFin) gefertigt. Der Xe Link Tile kommt wiederum von TSMC, dieses mal aber in 7 nm. Noch nicht geäußert hat sich Intel zum Rambo Cache und wie dieser gefertigt wird. Bisher geht man auch hier von Intel 7 aus. Hinzu kommt der HBM2E, der von Micron oder SK Hynix kommt.

Zur Supercomputing 2021 nennt Intel nun die Größen der Caches. Die 64 MB an L1-Cache ergaben sich aber bereits aus den 512 kB pro Xe-Core bzw. 8 MB pro Xe-Slice. Überraschend sind die 408 MB an L2-Cache, die Intel hier angibt, denn eigentlich sollten pro Base Tile nur 144 MB vorhanden sein. Uns ist daher noch nicht ganz klar, wie man hier auf 408 MB kommt.

Der Aurora-Supercomputer wird mindestens 18.000 Sapphire-Rapids-Prozessoren und mehr als 54.000 Ponte-Vecchio-Beschleuniger verwenden. Pro Compute-Node sollen zwei Xeon-Prozessoren und sechs GPU-Beschleuniger verwendet werden. Die Rechenleistung soll einen Wert von 2 ExaFLOPS im Peak erreichen können.

Neben dem Aurora-Supercomputer werden die Ponte-Vecchio-Beschleuniger von Atos, Dell, HPE, Inspur, Lenovo und QCT in deren OEM- und ODM-Servern angeboten werden.