Werbung

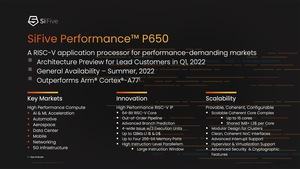

Nach mehreren Vorab-Ankündigungen und noch vor dem RISC-V Summit in wenigen Tagen hat SiFive den Performane-Core P650 vorgestellt. Mit diesem will sich SiFive auf das Leistungsniveau eines Cortex-A77 von Arm herangearbeitet haben.

Laut SiFive gibt es im General-Purpose-Umfeld aktuell keinen schnelleren RISC-V-Kern. Je nach Ausbaustufe des Clusters hat jeder Kern 256 KB an L1-Cache (je 128 kB für Daten und Instruktionen).

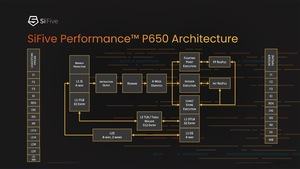

Anstatt bis zu vier P550-Kerne können beim P650 bis zu 16 in einem Cluster zusammengefasst werden. Dementsprechend wird der gemeinsame L3-Cache auf bis zu 16 MB vergrößert. Der für die einzelnen Kerne exklusive L2-Cache kann nun bis zu 2 MB groß werden. Am eigentlichen Aufbau der Kerne, bzw. der verwendeten Recheneinheiten und der Tatsache, dass es sich um eine 13-Stufen tiefe Pipeline mit Triple Issue im Out-of-Order-Design handelt, tut sich offenbar wenig.

| P550 | Next-Gen P-Series | |

| L1-Instruction-Cache | 32 kB | 64 bis 128 kB |

| L1-Data-Cache | 32 kB | 64 bis 128 kB |

| L2-Cache | 256 kB | bis zu 2 MB |

| L3-Cache | 1 - 4 MB | 1 - 16 MB |

| Core Complex | bis zu 4 Kerne | bis zu 16 |

| Memory Ports | 1x 128 oder 256 Bit | 4x 128 oder 256 Bit |

Die ISC-V Foundation hat 15 neue Spezifikationen verfasst, die beim P650 schon zur Anwendung kommen sollen. Insgesamt gibt es 40 neue Befehlssatzerweiterungen der RISC-V-ISA, die im Vergleich noch immer recht schlank bleibt. Solche für Hypervisor und die Virtualisierung könnten ein entscheidendes Merkmal für den P650 werden, der diese erstmals unterstützt. Aber auch im Bereich der Vektorerweiterungen und Kryptografie gibt es ein paar Neuerungen.

Der P650 bringt RISC-V somit in einen Bereich, in dem diese Prozessorkerne selbst für die Endkunden immer interessanter werden. Dass die Leistung (ISO-Frequency, also bei gleichem Takt) nun schon bei einem Cortex-A77 angelangt ist, zeigt die rasante Entwicklung. Einsatzfeld können IoT-Geräte bis hin zu Servern sein – zumindest theoretisch. Die erste Vorschau auf das P650-Design wird SiFive ausgewählten Kunden ab dem ersten Quartal 2022 ermöglichen. Im Sommer soll das Design dann allen zugänglich gemacht werden.

Über die Möglichkeit, mehrere dieser Cluster miteinander zu verbinden, kann ein Design mit 128 Kernen und mehr realisiert werden. Neben den CPU-Clustern können Sicherheitskomponenten, ein großer Last Level Cache und eine Translation Engine mittels Network on Chip (NOC) miteinander verbunden werden. Daraus werden durchaus komplexe Chips mit mehreren (LP)DDR-Speicherkanälen, zahlreichen PCIe-Controllern und Lanes sowie per SiFive Chip2Chip-Link auch einer externen CXL-Anbindung.

An dieser Stelle wollen wir noch auf unseren Test des SiFive HiFive Unmatched verweisen. Dabei handelt es sich um eine Entwicklerplattform für RISC-V.