Werbung

Wir hatten die Gelegenheit mit Adi Yoaz, Intels Chef-Architekten des Performance Core und Fellow, ein Interview zu führen. Eigentlich hätten wir dies vor Ort, in Haifa in Israel machen sollen, aber aufgrund der Reisebeschränkungen musste dieser Besuch abgesagt werden. Wir haben das Interview daher per Videokonferenz durchgeführt.

Natürlich sind die Performance-Cores bzw. die Golden-Cove-Architektur der Fokus des Interviews gewesen, uns hat aber auch interessiert, wie solche Entwicklungsprozesse ablaufen, welche Abwägungen gemacht werden müssen und vieles mehr.

Da wir das Interview in Englisch geführt haben, haben wir die Fragen und Antworten ins Deutsche übersetzt. Unter dem deutschen Interview findet ihr auch noch das englische Originaltranskript.

Da im Rahmen des Interviews einige technische Bezeichnungen verwendet werden, die vielleicht nicht jedem bekannt sind, zunächst einmal ein paar Hinweise dazu: Die Alder-Lake-Prozessoren sind ein Hybrid-Performance-Design. Das heißt, es kommen hier zwei unterschiedliche Kerne zum Einsatz: Performance Cores (die Adi Yoaz entwickelt hat) und Efficiency Cores. Die Efficiency Cores kommen auch bei den Atom-Prozessoren zum Einsatz, während die Performance Cores zudem noch die Basis der Xeon-Prozessoren Sapphire Rapids bilden werden. Die Microarchitektur der Performance Cores hört auf den Namen Golden Cove.

- Modelle, P- und E-Kerne, DDR5-Infos: Alles zum Start von Alder Lake-S

- Core i9-12900K und Core i5-12600K: Hybrid-Desktop-CPUs Alder Lake im Test

- K wie Mittelklasse: Intel Core i7-12700K im Test

- Test: Effizienz von Alder Lake in Spielen im Vergleich

Das Interview

Andreas Schilling: Vielleicht können Sie sich selbst vorstellen und uns einen Überblick über einige der Projekte geben, an denen Sie bei Intel gearbeitet haben?

Adi Yoaz: Ich bin vor etwa 25 Jahren zu Intel gekommen und wurde im Jahr 2000 an einen Intel-Standort in Austin geschickt, um dort das Team aufzubauen, das sich jetzt um den Efficiency Core kümmert. Ich verbrachte vier Jahre in Austin, um diesen Standort aufzubauen und kam dann im Jahr 2003 zurück nach Israel. Seitdem war ich sozusagen der leitende Core Architekt für alle Generationen, die in Haifa entworfen wurden.

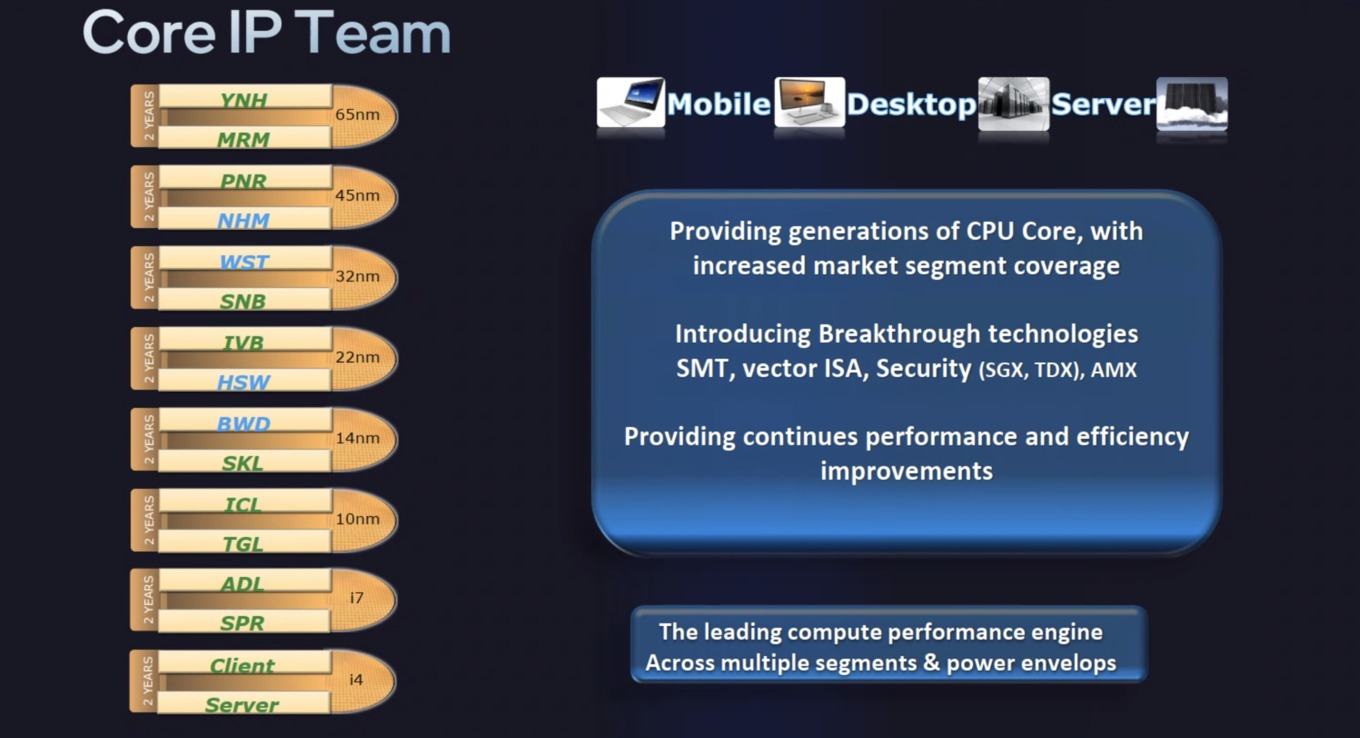

Redaktionelle Informationen: Adi zeigte diese Folie, auf der alle Designs, die in Haifa (Israel) entwickelt wurden und werden, grün dargestellt sind. Dazu gehören Yonah, Merom und Penryn. Nehalem und Westmere wurden in Oregon, USA, (blau) entworfen, Sandy Bridge und Ivy Bridge wieder in Israel. Dies sollte der berühmten Tick-Tock-Designphilosophie folgen, bei der ein Tock ein Wechsel zu einer neuen Microarchitektur und ein Tick eine neue Prozesstechnologie darstellt - mehr dazu später.

Nach Haswell und Broadwell wurden alle darauffolgenden Designs in Haifa entwickelt. Adi war der leitende Architekt für Skylake, Ice Lake, Tiger Lake und jetzt Alder Lake sowie Sapphire Rapids.

Kehren wir also zum Interview zurück: Wie funktioniert die Entwicklung neuer Mikroarchitekturen an zwei Standorten gleichzeitig, in Oregon und Haifa? Kann ich mir das als eine Art Wettlauf zwischen den Entwicklungsteams vorstellen?

Adi Yoaz: Lassen Sie mich erklären, wie es zwischen Israel und Oregon funktioniert, aber nur um sicherzugehen: Das Team in Austin ist ein separates Team, das am Efficiency Core (Anmerkung der Redaktion: Atom) arbeitet, es gibt also ein drittes Team. Zwischen dem israelischen Team und dem Team in Portland gab es einen Mechanismus, der "Ping Pong" genannt wird. Seit dem Design von Skylake wurde die Entwicklung des Core-Architekturen nur in Israel durchgeführt, wie Sie sehen können. Das "Ping Pong" fand nur für wenige Generationen statt. Es funktioniert so, dass jedes Team für einen großen Tock verantwortlich war. Und dann für den folgenden Tick, der einen Schritt in der Fertigungstechnik darstellt. Dann geht es wieder an das Team in Israel, im nächsten Schritt zum Team in Oregon.

Die Idee ist, eine Art Wettbewerb zu schaffen. Einerseits werden wir also ermutigt, miteinander zu konkurrieren. Und dann versuchen wir, die bestmöglichen Technologien und Ideen zu entwickeln. Andererseits weiß jedes Team, dass es die Arbeit des vorherigen Teams fortsetzen muss. Es gibt also eine Menge Zusammenarbeit und Interaktion zwischen den Teams. Ich weiß zum Beispiel, dass ich Westmere aus Oregon bekomme und hier in Israel dann Sandy Bridge daraus weiterentwickelt wird, was die Arbeit des Portland-Teams fortsetzt, und ähnlich verhält es sich mit Ivy Bridge und dann mit Haswell. In Oregon wurde mit Haswell also die Arbeit fortgesetzt, die ich bei Sandy Bridge und Ivy Bridge geleistet habe.

Es gibt also eine Menge Zusammenarbeit, aber auch eine Art Wettbewerb, um die besten Ideen mit den besten Technologien zu entwickeln. Jeder will schneller werden und zeigen, dass er es besser kann, was gut für das Unternehmen ist. Es ist auch gut für die Ingenieure. Es sorgt für mehr Begeisterung im Team. Es ist also immer gut, ein paralleles Team zu haben, das mit einem im Wettbewerbsmodus arbeitet.

Andreas Schilling: Und diesen Wettbewerb gibt es immer noch, denn im Moment sieht es so aus, als ob das Team in Israel die beste Arbeit leistet?

Adi Yoaz: Im Moment ist es Israel, aber wir sind dabei, die Fähigkeiten in Oregon wieder aufzubauen und wir wollen auch in Zukunft in den „Ping Pong“-Modus zurückkehren. Ich glaube, das ist gesünder für das Team - man fordert sich selbst heraus. Man kommt auf bessere Ideen, wenn man weiß, dass, wenn man etwas nicht tut, jemand anderes diese Ideen haben wird.

Andreas Schilling: War es auch eines ihrer Teams, das Cypress Cove auf 14 nm portiert hat?

Adi Yoaz: In Haifa ist ein großes Designzentrum und wir haben auch externe Teams in Indien und an anderen Standorten. Das Architekturteam, das ich leite, befindet sich vollständig in Israel, aber die Implementierungsteams, die zum Beispiel die Portierung einer bestimmten Architektur auf einen bestimmten Prozess vornehmen, können sich an verschiedenen Standorten befinden. Die Portierung von Cypress Cove selbst wurde in Indien durchgeführt.

Andreas Schilling: Das Performance Core Design "Golden Cove" ist für Core-Prozessoren und auch für Sapphire Rapids ausgelegt. Gibt es, abgesehen von unterschiedlichen Cache-Größen oder ähnlichem, irgendwelche Kompromisse, die man eingehen muss, um ein Core-Design für Client und Server zu entwickeln?

Adi Yoaz: Wir haben innovative Wege gefunden, um diese unterschiedlichen Anforderungen zu überbrücken. So wollten wir zum Beispiel eine neue Engine für maschinelles Lernen in Sapphire Rapid in das Serverdesign integrieren, was eine Anforderung für diesen Markt war, aber weniger für den Clientmarkt. Also haben wir uns neue Wege ausgedacht, um den neuen Coprozessor - nennen wir ihn mal so - nebenbei zu entwickeln, ihn dann abzuschneiden, wenn wir den Kern als Client-Design liefern. So hat das Server-Design den Vorteil, aber das Client-Design zahlt nicht den Preis dafür (Anmerkung der Redaktion: in Form von Nachteilen). Und wir sind ständig dabei, unsere Möglichkeiten zu verbessern, wie wir bestimmte Vorteile für bestimmte Marktsegmente bereitstellen können. Ohne die anderen Marktsegmente mit Technologien oder Funktionen zu belasten, die für diese Segmente weniger sinnvoll sind.

Andreas Schilling: Ich habe mir Ihre Präsentation des Performance Core auf dem Architecture Day noch einmal angesehen. Sie sagten, dass der Branch Target Buffer dynamisch ist und kleiner sein kann, um Strom zu sparen, aber auch zusätzliche Kapazität haben kann, wenn diese zur Verbesserung der Leistung benötigt wird. Was ist damit gemeint? Kann er größer als 12k sein?

Adi Yoaz: Nein, er ist nicht größer als 12k. Viele Leute verstehen nicht, dass auch der Performance Core auf Energieeffizienz ausgerichtet sein muss. Die Tatsache, dass wir ihn Performance Core nennen, bedeutet also nicht, dass wir es mit der Leistung übertreiben. Wir denken bei jeder Funktion darüber nach, wie wir den Stromverbrauch optimieren können und wie wir bewusst mit dem Stromverbrauch umgehen können, ohne es zu übertreiben. Die auf Effizienz getrimmte Funktion (Anmerkung der Redaktion: der dynamische Branch Target Buffer) ist nur ein Beispiel dafür, wie wir den Stromverbrauch im Auge behalten.

Andreas Schilling: Wie finden Sie die richtige Cache-Hierarchie und die richtige Kapazität für Caches? Ist das etwas, das man simuliert und sieht, was Software in fünf Jahren nutzen kann und was dann gebraucht wird. Wie fällt man diese Entscheidung, wie groß muss der Cache sein, um für die nächste Architektur die richtige zu sein?

Adi Yoaz: Da gibt es zwei wichtige Dinge zu beachten. Das eine ist die Tatsache, dass wir mit jeder Generation eine Balance aufbauen wollen. Und für jede Änderung, die wir am Ende vornehmen, muss die Maschine (Anmerkung der Redaktion: das Design) im Sinne einer Versorgung mit Mikrooperationen zum ausführenden Teil des Designs ausbalanciert werden. Zuführung der Rechenaufgaben und deren Bearbeitung müssen in einem Gleichgewicht sein. Das ist eine wichtige Überlegung. Und mit jeder Generation müssen wir die Maschine neu ausbalancieren und sie richtig bauen.

Der zweite Punkt ist die Entwicklung der Workloads. Wir führen also für jede Generation eine umfassende Analyse der Workloads durch und sehen, wie sich die Workloads zwischen den Generationen verhalten und welche Trends es bei den Anwendungen selbst gibt. Wir sehen zum Beispiel, dass viele native Anwendungen jetzt auf den Browser verlagert werden, was eine größere Codebasis und einen größeren Code-Fußabdruck bedeutet. Und auch die Datensätze werden immer größer. Wir verfolgen also diese Trends in der Entwicklung der Workloads. Und das ist ein weiterer Faktor dafür, wie wir die Kapazität der Caches, der TLBs, der Sprungvorhersagen und der verschiedenen Mikroarchitekturmerkmale abstimmen. Wir verfügen über ein sehr genaues Leistungsmodell, mit dem wir unsere Mikroarchitektur untersuchen, mit projizierten Workloads, um zu sehen, wie sie sich auf der neuen Mikroarchitektur verhalten, um dann die Entscheidungen zu treffen.

Wundern Sie sich also nicht, wenn Sie in der nächsten Generation eine andere Cache-Hierarchie und andere Kapazitäten sehen. So entwickelt sich das Ganze weiter. Bei den Workloads ist es wie mit dem Huhn und dem Ei. KI-Workloads entwickeln sich aus bestimmten Gründen weiter. Die Mikroarchitektur entwickelt sich weiter, und das eine nährt das andere, und am Ende sieht man den Fortschritt in der Technologie. Und dann ist da noch die Bedeutung einiger spezifischer Workloads. Je nachdem, ob man für Spiele oder für KI optimieren will. Wenn wir aufkommende Workloads sehen, die von großem Interesse sind, dann schauen wir wie sie sich verhalten.

Andreas Schilling: Und das ist auch der Grund, warum Sie zum Beispiel HBM2E bei Sapphire Rapids hinzufügen, weil es Workloads gibt, die schneller laufen können, wenn der Speicher so nah ist?

Adi Yoaz: Es ist ein bisschen mehr als das. Beim maschinellen Lernen sehen wir, dass die Datensätze wirklich riesig sind. Um sie verarbeiten zu können, braucht man eine hohe Bandbreite und einen schnelleren Zugriff auf den Speicher. Und bei Sapphire Rapids haben wir viele Ausführungsressourcen hinzugefügt, um die Matrixmultiplikation durchführen zu können. Es ist die erste CPU, die die Fähigkeit zur Matrixmultiplikation in den CPU-Kern integriert hat. Man kann sie wie normalen x86-Code programmieren und alle Tools verwenden. Sie ist also für Anwender geeignet, die Algorithmen des maschinellen Lernens ausführen wollen. Und da es bei diesen Algorithmen um große Datensätze mit vielen Daten geht, ist ein schneller Zugriff auf den Speicher erforderlich. HBM bietet diese Bandbreite. Das ist der Grund, warum es so wichtig war, denn auch diese Workloads neigen dazu, auf große Datenmengen zuzugreifen. Um sie zu unterstützen, brauchten wir also den HBM.

Andreas Schilling: Ich denke, AMX ist eine der wichtigsten Funktionen für Sapphire Rapids. In der Präsentation sagten Sie, dass die TMULL-Engine mit dem P-Kern als Host gekoppelt ist. Aber es ist auch möglich, einen weiteren Coprozessor hinzuzufügen, um die Ausführung zu beschleunigen. Ist der Beschleuniger ein externer Teil, wie ein GPU-Beschleuniger? Oder was meinen Sie mit einem weiteren Coprozessor?

Adi Yoaz: Er ist wirklich eng gekoppelt. Die Idee war, eine Matrixmultiplikationsfunktion einzubauen, als ob es sich um einen Addierer oder Multiplikator handeln würde. Stellen Sie sich vor, Sie haben heute CPU-Kerne, in denen Sie natürlich entweder Additions- oder Teiler-Funktion haben. Jetzt haben wir eine Möglichkeit eingeführt, die Matrixmultiplikation so durchzuführen, als ob sie Teil des Hauptflusses wären. Man geht nicht wirklich aus dem Kern heraus, um die Matrixmultiplikation durchzuführen. Sie ist eng gekoppelt. Stellen Sie es sich als eine weitere ALU vor, die eine ADD-Operation durchführen kann, aber jetzt können Sie auch eine Matrixmultiplikation darauf durchführen.

Wir haben ihn so konzipiert, dass er modular ist - falls wir in Zukunft weitere Funktionen finden. Da wir also immer noch über eine General-Purpose-CPU sprechen, wollen wir Funktionen finden, die allgemein genug sind. Nach Additionen, Multiplikationen und Divisionen ist die nächste gängige Funktion die Matrixmultiplikation, insbesondere bei KI. Wenn sie in Zukunft eine andere mathematische Funktion finden, die interessant und gebräuchlich genug ist, dann haben wir dafür gesorgt, dass die Architektur gleich bleibt und die neue Funktion eingeführt werden kann.

Wir wollten also die Architektur so gestalten, dass neue Ausführungsmöglichkeiten leicht hinzugefügt werden können. Heute haben wir die Matrixmultiplikation, in Zukunft werden wir vielleicht andere Funktionen haben, und dann werden die Software und die Architektur selbst einfach und zugänglich sein. Man darf nicht vergessen, dass wir auch neue Tiles definieren. Das ist so, wie man heute ein eindimensionales Register hat. Der Tile ist ein neues zweidimensionales Register, und wenn in der Zukunft jemand eine neue mathematische Funktion erfindet, kann sie sowohl mit den zweidimensionalen Registern als auch mit den regulären Registern auf einfache Weise programmiert werden.

Andreas Schilling: Als leitender Architekt ist es Ihre Aufgabe, das richtige Gleichgewicht zwischen Leistung und Effizienz zu finden und das gesamte Design zu entwickeln. Aber einige Teile davon hängen zum Beispiel von der verfügbaren Prozesstechnologie ab. Inwieweit hängt das Endprodukt also von den derzeit verfügbaren Technologien ab?

Adi Yoaz: Wissen Sie, wir wollen den Mehrwert des Produkts maximieren, und die Architektur geht Hand in Hand mit den Prozessfortschritten. Aber das ist nicht unbedingt miteinander verbunden. Wir wollen immer den besten verfügbaren Prozess nutzen, aber wie Sie am "Tick Tock"-Modell gesehen haben, nutzt die nächste Architekturgeneration manchmal nicht den neuesten Fertigungsschritt. Wenn man eine neue Architektur mit einem neuen Prozessknoten kombiniert, kann man natürlich den Mehrwert maximieren. Aber man kann sich das als zwei parallele Spuren vorstellen, und dann trifft das Team die Entscheidung, welche Prozesstechnik verwendet werden soll. Ja, natürlich wollen wir den Mehrwert maximieren und mit der nächsten Prozesstechnik die große Veränderung der Mikroarchitektur erreichen. Sie müssen aber nicht übereinstimmen.

Andreas Schilling: Aber Sie müssen doch erleichtert sein, dass Intel jetzt, wo die Fertigung in 10 nm funktioniert und die Roadmaps für zukünftige Prozesstechniken vielversprechend aussieht?

Adi Yoaz: Es ist keine Frage der Erleichterung, es ist eine Frage des Zeitpunkts, an dem wir alle Vektoren, die wir nutzen können, maximieren wollen - die Architektur, den Prozess, alles, was uns zur Verfügung steht. Wir wollen es an die Spitze dessen bringen, was es da draußen gibt.

Andreas Schilling: Sind Sie zufrieden damit, wie sich Golden Cove in Alder Lake und Sapphire Rapids entwickelt? Denken Sie schon darüber nach, was man besser machen könnte? Und wann hat das angefangen?

Adi Yoaz: Zunächst einmal bin ich sehr zufrieden, weil wir viele gute Rückmeldungen von der Fachpresse und auch von allen technischen Websites und Vergleichen, die dort gemacht werden, erhalten. Für uns ist es eine großartige Bestätigung, dass wir in Alder Lake einen großen Schritt nach vorn gemacht haben, und das wird sich bald auch in Sapphire Rapids zeigen. Wir haben bahnbrechende Technologien eingeführt, sowohl auf dem Client als auch auf dem Server. Wir sehen also, dass wir aufregende Technologien einführen, dass der Markt sie mag und dass wir von allen ein großartiges Feedback erhalten, was uns ermutigt, weiterzumachen. Die Zukunft bringt einen weiteren Schritt in Richtung neuer Funktionen und neue Technologien. Ja, es ist wirklich aufregend. Ich erhalte eine Menge großartiger Rückmeldungen, und das spornt uns an, den Schwung beizubehalten und mit dem Erfolg von Alder Lake und Sapphire Rapids und der nächsten Generation, die wir ebenfalls in Haifa entwickeln, weiterzumachen.

Andreas Schilling: Danke Adi!

Adi Yoaz: Danke!

Englisches Transskript:

Andreas Schilling: Maybe you can introduce yourself and could give us an overview of some of the projects you’ve worked on at Intel?

Adi Yoaz: I joined Intel about 25 years ago and in the year 2000 I was sent to a location in Austin to build over there the team that is doing now the efficient core. I spent four years in Austin, Texas, to build that site. And then I came back to Israel after four years in the year 2003. And since then I was kind of the lead architect for all core generations that were designed in Haifa.

Editorial Information: Adi showed this slide, where all the designs that were designed in Haifa (Israel) are in green. That includes Yonah, Merom and Penryn. Nehalem and Westmere were developed in Oregon (blue), Sandy Bridge and Ivy Bridge in Israel again. This was supposed to follow the famous Tick-Tock design philosophy, where a Tock is a shift to a new architecture design and a Tick a new process technology – more on this later.

After Haswell and Broadwell all the designs that followed this were developed in Haifa. Adi was the lead architect for Skylake, Ice Lake, Tiger Lake and now Alder Lake as well as Sapphire Rapids.

So let’s go back to the interview, where we did asked how the development of new microarchitectures work in two locations at once, Oregon and Haifa? Can I think of it as a kind of race between the design teams?

Adi Yoaz: So so let me explain how it works between Israel and Oregon, but just to make sure it's clear that the Austin team is a separate team working on the efficient core, so, it's a third team. Between the Israel team and the Portland team we used to have a mechanism which is called the „ping pong“. And since the design of Skylake the development of the core was done only in Israel as you can see. And the the „ping pong“ happened only in a few generations. It works in a way that every team was responsible on a major Tock. And then on the following Tick, which goes to the next process node. Then it moves to the Israel team and then it moves to the Oregon team.

The idea is to have some sort of competition. So on one hand, we are kind of encouraged to compete between us. And then to try and come up with the best possible technologies and ideas. But then every team knows that it needs to continue the work of the previous team. So there is a lot of collaboration and interactions between the teams. I know for example that I'm taking Westmere and I produce Sandy Bridge, which continues what the Portland team is doing and similarly when I did Ivy Bridge and then came Haswell. So Haswell continues they work that I did in Sandy Bridge and Ivy Bridge.

So there is a lot of collaboration, but there is also some sort of competition to try and come up with the best ideas with the best technologies. Everybody wants to accelerate, to show that they can do way better, which is good for the company. It's good also for the engineers. It gets more excitement there to the team. So it's always good to have a parallel team working with you in competition mode.

Andreas Schilling: And this competition is still in place, because it looks like right now it's just Israel is doing the best job?

Adi Yoaz: Right now it's Israel, but we are kind of rebuilding the capabilities in Oregon and in the future we do want to maintain such a mode of what we call „ping pong“. I think it's healthier for the team – you challenge yourself, you come up with better ideas when you know that if you don't do that, someone else will do the better ideas.

Andreas Schilling: Were you also on the teams that ported Cypress Cove to 14 nm?

Adi Yoaz: Israel is a big design center and we actually also have like satellite teams in India and other places. The architectural team that I lead is fully in Israel, but the implementation teams, that for example are doing the porting of a particular architecture to particular process, can be in different locations. The porting itself of Cypress Cove was done in India.

Andreas Schilling: The Performance Core design Golden Core is designed for Core processors and also for Sapphire Rapids. What are, if any, besides different cache sizes or something like that – are there any compromises that have to be made for designing a Core design for client and server?

Adi Yoaz: We are coming with innovative ways how to bridge those different requirements. So, for example, we wanted to put a new a machine learning engine in Sapphire Rapid, into the server design, which was a requirement for that market, and was less a requirement for the client market. So we have come up with new ways to design the new coprocessor – Let's call it, on the side. And then chop it off when we deliver the core to the client. So the server will get the benefit, but the client will not pay the price. And we are all the time improving our ways of how to deliver specific goodness to specific market segment. Without burdening the other market segments with technologies or features that are less valuable for those segments.

Andreas Schilling: I did rewatch your Architecture Day presentation of the Performance Core. You said that the branch Target Buffer is dynamic and can be smaller to save power, but also can have extra capacity when it's needed to improve the performance. What does that mean? Can it be larger than 12k?

Adi Yoaz: No, it's not larger than 12k. So many people don't understand that even the Performance Core needs to focus on power efficiency. So the fact that the call it Performance Core doesn't mean that we go wild on power. So still with every feature we think about how to optimize the power and how to be conscious of the power and not go wild. So tuned for efficiency, it (e.i. the dynamic Target Buffer) is just an example how to keep power in mind.

Andreas Schilling: How do you find the right cache hierarchy and the right capacity for caches? Is that something you simulate and see what can software use in five years and that is what we need. How is this development on how big has the cache to be to define for the next architecture?

Adi Yoaz: So two major things to keep in mind. One is the fact that with every generation, we want to build the balance machine. And for every change, that we do at the end, the machine needs to be balanced in the sense of a micro operation supply into the execution out of order engine. And then that supply, it all needs to be a balance. This is one major consideration. And with every generation, you need to rebalance the machine and build it correctly. For all the features together. This is one thing.

Second thing is the evolution of the workloads. So we do extensive work of workload analysis for every generation, and we see how workloads behave between generations and what are the trends in the applications themselves. So for example, we see that many, many native applications are now moving to the browser, which implies a larger code sizes and a larger code footprint. And also data sets are getting larger. So, we kind of a track these trends in the evolution of the workloads. And this is another factor of how we tune the capacity of the cache sizes, the TLBs, the branch predictors and the different micro architectural features. We are having a very accurate performance model, which we are examining our proposed microarchitecture, use the new predict workloads to see how they behave on the new proposed microarchitecture and make the choices.

Now, don't be surprised if in the next generation, you see different cache hierarchy, different sizes. This is how it evolves. Workloads, it's a chicken and a egg. AI workloads are evolving because of certain things. Microarchitecture is evolving and this is like one is feeding the other and in the end you see progress with the technology. And then also the importance of some specific workloads. Depending if you want to optimize for games or for AI. If we see emerging workloads that are becoming of high interest and how they behave - so, this is how we do it.

Andreas Schilling: So and this is also why you for example add HBM2E to Sapphire Rapids because there’re workloads that can run faster of the memory is that close?

Adi Yoaz: It's a little bit more more than that. So for machine learning, we see that the data sets are really massively. In order to be able to crunch them, you need to have high bandwidth and the faster access to to memory. And to keep in mind that for Sapphire Rapids we added a lot of execution capability resources to be able to do matrix multiplication. It’s the first CPU that has integrated the matrix multiplication capabilities on the CPU core. You can program it if it's regular x86 code, use all the tools. So it's friendly for people who wants to run a machine learning type of algorithms. And these algorithms, since we're talking about large datasets that involves a lot of data, it requires a good access to memory and HBM is providing such bandwidth. So this is why it was important because again, these workloads are tend to access large quantities of data. So in order to support it, we needed the HBM capability.

Andreas Schilling: I think AMX is one of the biggest features for Sapphire Rapids. In the presentation, you said that the TMULL engine is coupled to the P core as a host. And but it's also possible to add another coprocessor to accelerate the the execution. Is the accelerator an external part, like a GPU accelerator? Or what do you mean as another core processor?

Adi Yoaz: It's really tightly coupled. The idea here was to put a matrix multiplication capability as if this is like an adder or multiplier. Think of it that today you have CPU cores, in which you have of course either multiplier and divider capabilities. Now we introduced a way to do matrix multiplication as if it's part of the main flow. You don't really go out of the core to do matrix multiplication. It’s tightly coupled. Think of it as another ALU that can do an ADD operation, but now you can do a matrix multiplication operation.

Now, we architected it in a way that it will be modular – if in the future, we will find other functions. So, since we are still general purpose, we want to find functions that are common enough. So, after you do additions, multiplications and divisions, the next most common thing is the matrix multiplication especially with AI. Now, if in the future, you find some other mathematical function that is interesting and common enough, then we made it easy for the architecture to stay the same and then to introduce the new functionality. So we wanted to build the architecture in a way that it will be friendly to put new types of execution capabilities. Today we have matrix multiplication, maybe in the future we'll have other functions and then from a software point and architecture itself will be will be easy and friendly. Because keep in mind that we also define new tiles. That is like today you have one dimensional layer register. The tile is a new two dimensional register and if in the future someone comes up with a new mathematical function it can continue to work with the two dimensional registers as well as the regular registers in an easy to program way.

Andreas Schilling: As a lead architect your job is to find the right balance between performance, frequency power and build up the whole design. But some pieces of this do rely on for example, the available process tech. So, to what extent is the final product depending on what is currently available?

Adi Yoaz: You know, we want to maximize the value of he product and the architecture goes hand in hand with the process advancements. But it's not necessarily connected. So, every time we want to be on the best available process, but you saw on the „Tick Tock“ model sometimes the next generation architecture is not using the latest process node. If you have the combination of new architecture and a new process node, of course, you will maximize the value. But you can think of it as two parallel tracks and then the product makes the decision on which process node to do the intercept. So yes, of course we want to maximize the value and come up with the big micro architectural shift with the next process node. They don't have to align.

Andreas Schilling: But you must be relieved that Intel seem to be back on track on future process now that 10 nanometers are working and the roadmaps looking promising for future process nodes?

Adi Yoaz: It's not a question of relief, it's a question of when we want to maximize all the vectors that we can use – the architecture, the process, everything in our disposal. We want to bring it to the leading edge of what is out there.

Andreas Schilling: You are happy how Golden Cove s playing out in Alder Lake and Sapphire Rapids? Are you already thinking about what could be done better? And when did that start?

Adi Yoaz: First of all, I'm very happy because we see a lot of good feedbacks from the technical press and also from all the technical websites and comparisons being made out there. So yes, for us, it's a great confirmation that we made the major step in Alder Lake and soon it will be seen in Sapphire Rapids. We have introduced breakthrough technologies, both in the client and the server. So we see we bring exciting technologies, the market likes it and we get great feedback from everybody, which encouraged us to continue. The future gives another step functioning and new technologies. Yes, it's really exciting. I get a lot of great feedback and it just energizes us to to keep the momentum and continue with the success of Alder Lake and Sapphire Rapids and into the the next generation that we're also designing in Haifa.

Andreas Schilling: Thanks Adi!

Adi Yoaz: Thank you!