Werbung

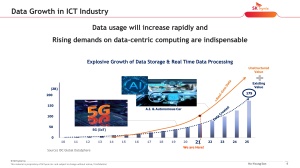

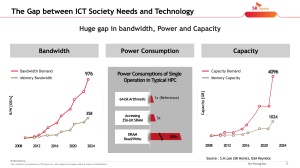

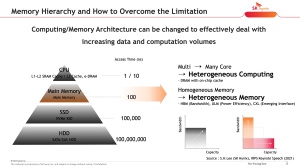

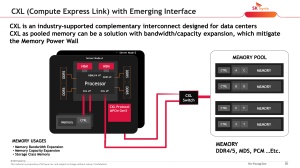

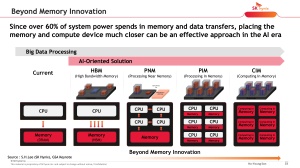

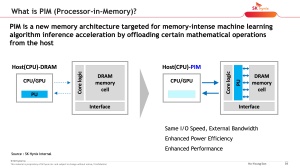

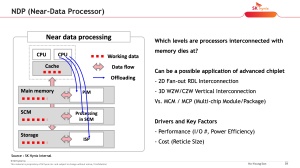

Bereits häufiger haben wir über die Weiterentwicklung in der Speichertechnik berichtet, in der ein Processing-in-Memory (PIM) stattfindet. Die Kommunikation zwischen den eigentlichen Recheneinheiten und dem Speicherort der Daten wird zunehmend zu einem Flaschenhals. Geringe Latenzen und hohe Bandbreiten sind für AI-Anwendungen besonders wichtig – entsprechend breit und schnell werden die Speicherinterfaces.

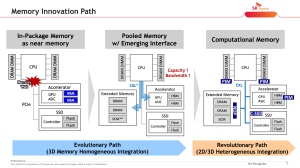

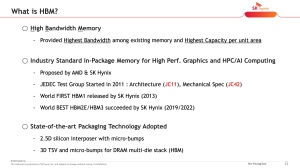

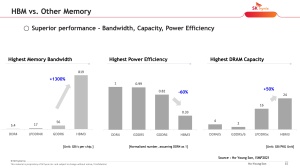

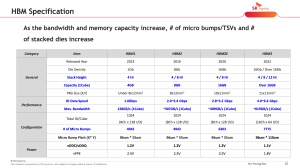

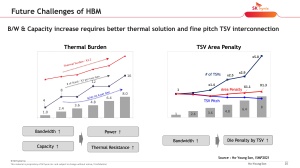

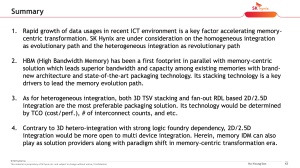

Auf dem VLSI Symposium hat SK hynix über die aktuelle Entwicklung in diesem Bereich gesprochen und führt dabei die eben erwähnten Punkte an: Immer größere Speicherkapazitäten werden immer näher und mit einer immer schnelleren Anbindung an die Recheneinheiten gebracht. GPUs im Datacenter verwenden nicht ohne Grund HBM2E oder gar schon HBM3. Intel wird die nächsten Xeon-Prozessoren Sapphire Rapids mit HBM2E auf dem Package der CPU-Kerne anbieten. All diese Maßnahmen haben das gleiche Ziel.

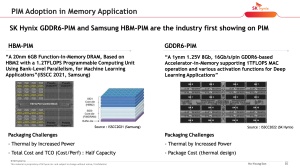

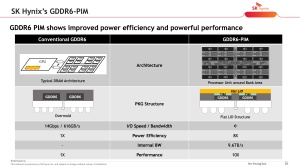

SK hynix kündigte im vergangenen Jahr die Entwicklung von GDDR6 (AiM - Accelerator in Memory) mit integrierten Recheneinheiten an. Samsung arbeitet an HBM, zuletzt an HBM2 alias Aquabolt-XL, mit Processing-in-Memory (PIM) Architektur. Dies wird laut beider Hersteller der Weg der Zukunft sein. Als Speicherhersteller hat man natürlich ein Interesse daran, die eigenen Produkte hervorzuheben.

Die Vorbereitung, bzw. die Verarbeitung von Daten im Speicher hat natürlich gewisse Herausforderungen. Die Effizienz kommt hauptsächlich über den geringen Overhead im Datenverkehr zu Stande.

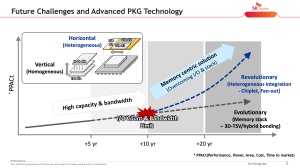

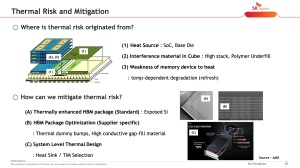

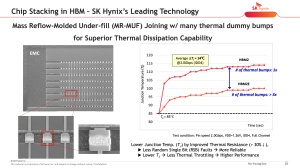

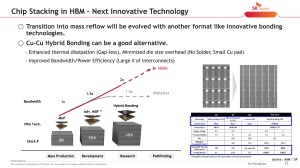

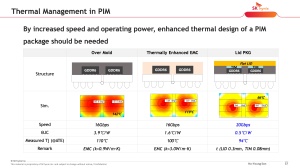

Die Kühlung ist einer der wichtigsten Faktoren, an denen aktuell gearbeitet wird. Ein GDDR6-Speicher würde in einem Standard-Package ohne zusätzliche Maßnahmen über 140 °C erreichen. Ein thermisch verbessertes Packaging könnte dies auf 120 °C reduzieren, aber noch immer wäre dies deutlich zu warm, um den Speicher in der Praxis dauerhaft betreiben zu können. Erst der Einsatz eines thermischen Interface (TIM) und eines dünnen Heatspreaders ermöglicht einen Betrieb von unter 100 °C.

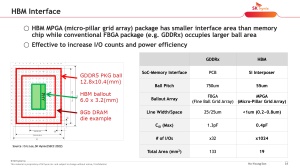

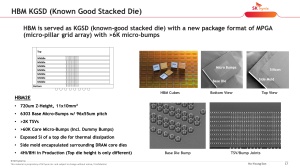

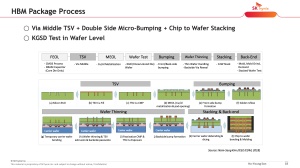

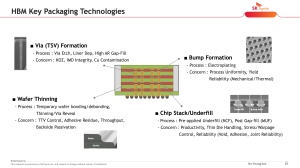

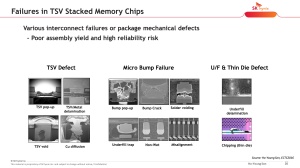

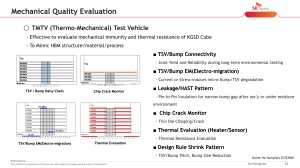

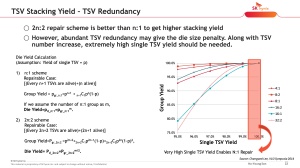

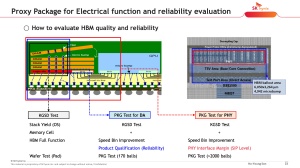

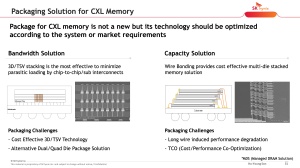

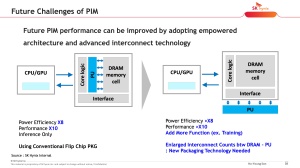

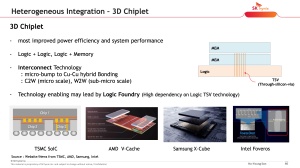

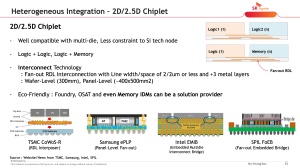

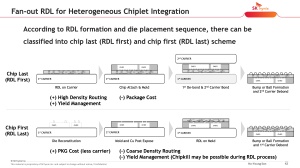

Das Packaging ist ein weiterer Faktor, denn der Speicher wird bis auf weiteres nicht gänzlich auf die Unterstützung dedizierter Compute-Chips verzichten können. Für die Fertigung des HBMs, bzw. GDDR6 setzen die Hersteller zudem ebenfalls auf Techniken wie TSV und Cu-Cu-Bonding.

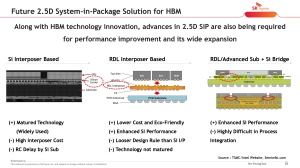

Für die Anbindung zwischen HBM und den Compute-Chips haben alle namhaften Hersteller bereits Lösungen: TSMC CoWoS-R, Samsung ePLP, Intel EMIB, SPIL FoEB sind hier die wichtigsten Anbieter und ihre Prozesse.

Geht es nach den Herstellern wie Samsung oder SK hynix, ist es nur noch eine Frage von Monaten, bis ein solcher Speicher zum Einsatz kommt. Bisher aber scheinen sich die Hersteller der Rechenhardware noch auf eine Trennung zwischen Speicher und den Recheneinheiten zu konzentrieren.