Werbung

Desintegrierte Designs werden für zukünftige Prozessoren, GPUs und andere Chips immer wichtiger werden. AMD setzt bei den Ryzen-Prozessoren bereits auf diese Chiplet-Strategie, Intel wird es mit Meteor Lake und Sapphire Rapids tun und über kurz oder lang werden auch die GPUs von AMD und NVIDIA aus mehreren Chips bestehen.

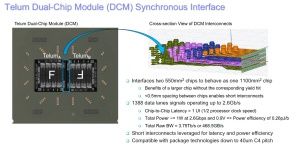

Im vergangenen Jahr stellte IBM auf der Hotchips 33 den z16 Telum vor. Der Prozessor besteht eigentlich aus zwei Chips mit jeweils acht Kernen, 32 MB an L2-Cache sowie einem gemeinsamen L3- und L4-Cache mit einer Kapazität von 256 MB bzw. virtuellen 2 GB über acht Prozessoren. Gefertigt werden sie in 7 nm bei TSMC und kommen bei 22,5 Milliarden Transistoren auf einer Fläche von 530 mm². Auf dem Package arbeiten zwei dieser Chips, die miteinander verbunden sind.

Eben in dieser Verbindung liegt die eigentliche Herausforderung für das Design, damit die beiden Chiplets sich nach Außen hin wie ein Prozessor vorhalten. IBM hat hier ein Dual-Chip-Module (DCM) Synchronous Interface entwickelt, welches sich natürlich auch gegen die Lösungen der Konkurrenz vergleichen lässt. Twitterer und Analyst Dylan Patel hat dazu einige Informationen ausgegraben.

Verglichen wird hier das Chip-Interface von IBM gegen Intels MDFIO, wie es bei den kommenden Xeon-Prozessoren Sapphire Rapids zum Einsatz kommen wird. Auch der ebenfalls von Intel entwickelte Advanced Interface Bus (AIB) sowie BoW-64 (Bunch of Wires) und OpenHBI werden miteinander verglichen.

Das Module-Interface von IBM verwendet beispielsweise SDR (Single Data Rate) anstatt DDR (Double Data Rate). Es wird also pro Taktyklus nur ein Bit übertragen anstatt zwei. Die Datenrate ist damit pro Pin natürlich nur halb so hoch. Herausragend aber ist die Effizienz in der Übertragen. IBM kommt auf nur 0,26 pJ/Bit, während MDFIO mit 0,5 pJ/Bit doppelt so viel Energie pro Übertragung eines Bits benötigt. Der Interconnect kommt also auf eine Leistungsaufnahme von 1 W bei 2,6 GBit/s. Die Rohbandbreite liegt bei 468,5 GB/s.

Zweiter überraschender Fakt ist die Latenz die IBM zwischen den Chips erreicht. 0,37 ns sollen es hier sein, während Intel auf 2,4 ns kommt. Dies hat vor allem Auswirkungen auf den Verhalten und den Austausch von Daten im Hinblick auf die Tatsache, dass die zwei Chips als ein Prozessor fungieren sollen.

Insgesamt kommen 1.388 Datenverbindungen zwischen den Chips zum Einsatz. Deren Anzahl wäre mit Nutzung von DDR für die Signalübertragung etwas geringer, aber IBM hat sich für diesen Weg entschieden. Ein Grund dürfte der Umstand sein, IBM für diese Art der Verbindung keinerlei Bridges oder Interposer-Materialen benötigt – sich der Aufwand in der Fertigung also in Grenzen halten sollte. Alles in Allem ein interessanter Einblick in die Technik und die Umsetzung durch IBM.