Werbung

Heute ist es so weit. Die vierte Xeon-Generation alias Sapphire Rapids geht offiziell an den Start. Ursprünglich im Mai 2019 angekündigt und für 2021 vorgesehen, feiert die neue Xeon-Generation keinen "harten" Start, sondern wird fließend in den kommenden Wochen und Monaten ihren Weg in den Markt finden. Ihre Basis bilden Golden-Cove-Kerne, die in Intel 7 gefertigt werden und vielen Neuerungen bieten. Wir werden alles Wissenswerte gesammelt aufführen.

Sapphire Rapids gehört sicherlich nicht zu den Vorzeigeobjekten, wenn es um die Ausführung und Einführung einer neuen CPU-Generation bei Intel geht. Die zahlreichen Versschiebungen und Meldungen rund um eine schlechte Ausbeute in der Intel-7-Fertigung haben das Image des Chipriesen sicherlich nicht verbessern können. Zugleich hat AMD den Druck mit technologisch überlegenen und innovativen CPU-Generationen immer weiter erhöht. Die Marktmacht Intels hat dem Unternehmen viel retten können, was andernfalls unwiederbringlich verloren gegangen wäre – und damit ist nicht nur der Markanteil gemeint.

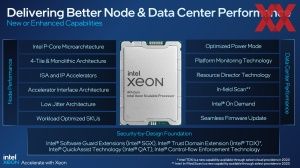

Grundsätzlich kann man die vierte Xeon-Scalable-Generation in drei Produktgruppen aufteilen: Die Standard-Xeons mit bis zu 56 Kernen, die Multi-Socket und Hyperscaler-Varianten für bis zu 8S-Systeme und mit bis zu 60 Kernen pro Sockel und die Varianten mit HBM2E-Speicher.

Neben den bis zu 60 Kernen pro Sockel und den Sondermodellen mit HBM2E-Speicher bietet die Sapphire-Rapids-Generation auch noch die Unterstützung von bis zu 80 PCI-Express-5.0-Lanes und acht Speicherkanälen für DDR5-4800 bei einem und DDR5-4400 bei zwei Modulen pro Speicherkanal. Daneben gibt es noch eine Handvoll Beschleuniger, die nun Bestandteil der Kerne selbst oder die Teil des Package sind.

Auch CXL 1.1 ist Bestandteil der Funktionen von Sapphire Rapids. Unterstützt werden bis zu vier CXL-Geräte pro Prozessor, aber es noch nicht alle Typen von CXL. Intel nennt Type 1 (CXL.io und CXl.cache) für SmartNICs sowie Type 2 (CXL.io, CXL.cache und CXL.mem) so wie es für GPUs, ASICs und FPGAs angedacht ist.

Sapphire Rapids: Vier Chips (+ 4x HBM2E) in einem Package

Grundsätzlich werden die Chips für Sapphire Rapids in Intel 7, also einer 10-nm-Fertigungsklasse, gefertigt. Inzwischen hat Intel intern sicherlich dutzende Verbesserungen dieser 10-nm-Fertigung vorgenommen und man kann sagen, dass man nun auf einem wettbewerbsfähigen Level hinsichtlich der Ausbeute ist. Für die kleineren Desktop-Chips ist dies wohl schon etwas länger der Fall, für größere Chips (in diesem Fall etwa 400 mm²) fällt die Ausbeute aber immer etwas niedriger aus.

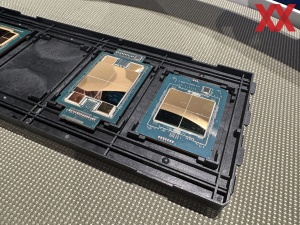

Intel unterscheidet nicht direkt über die Chips, sondern über das Package, welches dann in einem LGA4677 seinen Platz findet. Es gibt ein XCC-Package (Extreme Core Count), welches aus vier Tiles besteht. Hier kann Intel mehr Kerne anbieten, das I/O-Angebot ist größer und diese sind auch für Multi-Socket-Systeme vorgesehen. Dann gibt es noch das MCC-Package (Medium Core Count). Hier setzt Intel auf nur einen monolithische Chip, was höhere Taktraten und geringere Latenzen ermöglicht. Die Xeon-Max-Prozessoren mit HBM2E basieren auf dem XCC-Package und sind hinsichtlich des Sockels vollständig zu den anderen Varianten kompatibel.

In der Fertigung laufen vier Chips vom Band, die dann in den verschiedenen Packages zum Einsatz kommen. Für die XCC-Variante benötigt Intel für das Layout zwei Chips, um diese in einer 2x2-Anordnung auf dem Package unterzubringen. Zehn EMIB-Verbindungen (Embedded Multi-die Interconnect Bridge) verbinden die vier Tiles miteinander. Es gibt hier also eine asymmetrische Anbindung zwischen den Tiles.

Kommen die vier HBM-Speicherchips hinzu, verwendet Intel 14 EMIB-Verbindungen – jeweils eine zusätzlich für jeden HBM-Stack. Dies verlangt auch nach einem anderen Layout des Chips selbst, so dass wir hier die dritte Variante von Sapphire Rapids bzw. des XCC-Dies sehen.

Die vierte ist der MCC-Die, der natürlich alleine schon aufgrund der Anzahl der Kerne pro Chip sowie dessen Aufbau eine vierte Chip-Variante darstellt.

| Kerne | UPIs | PCIe | Speicherkanäle | Chipgröße | EMIB-Verbindungen | |

| XCC-Package | 60 | 4 | 5x 16 Lanes | 8x DDR5 | 4x 400 mm² | 10 |

| MCC-Package | 32 | 3 | 5x 16 Lanes | 8x DDR5 | ? | keine |

| XCC-HBM-Package | 56 | 4 | 5x 16 Lanes | 8x DDR5 + 4x HBM2e | 4x 400 mm² | 14 |

Das XCC-Package bietet maximal 60 Kerne und vier mögliche UPI-Links, um mehrere Sockel miteinander zu verbinden. Insgesamt sind 80 PCI-Express-5.0-Lanes vorhanden. Beim MCC-Package sind es maximal 32 Kerne – der Chip ist also deutlich größer als jeder einzelne XCC-Chip. Für das gesamte Package zur Verfügung stehen drei UPI-Links und ebenfalls 80 PCI-Express-5.0-Lanes. Beim Speicherinterface müssen keinerlei Einschränkungen gemacht werden, denn auch beim MCC-Package werden acht Speicherkanäle angeboten.

Laut Intel kommt der MDFIO auf 0,5 pJ/B. Per dynamischer Frequnzanpassung kann der Fabric IO sich aber auch der Last anpassen und arbeitet mit einem Dynamic Voltage Frequency Scaling (DVFS) mit einem Takt zwischen 800 MHz und 2,5 GHz. Die kumulierte Bandbreite des Fabric liegt bei 10 TB/s (20 Crossings mit je 500 GB/s). Die Round-Trip-Latenz im MDFIO/EMIB soll bei weniger als 10 ns liegen.

Um die Unterscheidung zwischen den zwei XCC-Dies für die Standard-Varianten der vierten Generation der Xeon-Scalable-Prozessoren sowie zwischen den MCC-Dies und dem XCC-HBM-Die machen zu können, haben wir eine weitere Tabelle aufgelegt.

| Kerne | Aufbau | MCs | ACs | |

| XCC | 15 | 6x4 Mesh | 1 | 1x XCC AC |

| MCC | 32 | 9x7 Mesh | 4 | 1x MCC AC |

| XCC HBM | 56 | 6x4 Mesh | 1 + 1 | 1x XCC AC |

Organisiert sind die Kerne im Mesh in einem 6x4 bzw. 9x7-Layout. Bein XCC-Die gibt es nur einen Speichercontroller für zwei Speicherkanäle. Als Package mit vier Dies kommt man dann hier auf die acht DDR5-Speicherkanäle. Für den MCC-Die muss Intel daher gleich vier Speichercontroller mit jeweils zwei Speicherkanälen umsetzen. In jedem Chip gibt es zudem einen Accelerator Complex (AC). Der XCC AC besteht aus jeweils einem QAT, DLB, DSA und IAA. Was diese einzelnen Beschleuniger machen, dazu kommen wir noch. Der MCC AC besitzt jeweils zwei QAT und DLB sowie jeweils einen DSA und IAA.

Aber auch wenn die für Sapphire Rapids verwendeten Chips mit 400 mm² vergleichsweise klein sind, so hat Intel sich wohl aufgrund der bisherigen Erfahrungen mit der Fertigung in 10 nm dazu entschlossen, viele Maßnahmen zu ergreifen, um eventuelle Defekte ausgleichen zu können. Diese gehen über das hinaus, was Intel bisher an Reparatur- und Wiederherstellungsmethoden angewendet hat und betrifft die Bereiche Core (die eigentlichen Performance-Kerne) ebenso wie die Caches, Uncore und I/O-Blöcke.

Redundante Schaltkreise in gefährdeten Bereichen sind eine Maßnahme, um bei einem eventuellen Defekt auszugleichen. Für den MDFIO können einzelne Verbindungen wiederhergestellt werden, um Fehler vor und nach der Montage des gesamten Packages zu beheben.

Ungenutzte PCIe-Blöcke im "südlichen" Bereich des Chips ermöglichen die Wiederherstellung einiger I/O-Blöcke durch eine Umwidmung. Insgesamt sind laut Intel 74 % des Chips wiederherstellbar. Ein aus vier Chip zusammengesetzter Prozessor lässt sich in seinen einzelnen Funktionen und Verbindungen aber gar nicht mehr so einfach testen. Intel musste sich auch hier Mittel und Wege einfallen lassen, um beispielsweise direkt an der EMIB-Verbindung Tests durchführen zu können oder sieht GPIO-Pins und sieht auch die Verwendung von JTAG vor.

Die Basis für x86: Golden Cove

Intel stellt das Front End bei Golden Cove extrem breit auf. In dieser Form kam es in Alder Lake für die Performance-Kerne zum Einsatz, allerdings mit weniger L2-Cache und L3-Cache pro Kern. Mit Golden Cove gibt es wieder einen Micro-op-Cache mit deutlich mehr Einträgen, der zudem auch noch mehr Einträge abarbeiten kann. Eine 6-Wide-Allocation, eine clevere Branche Prediction und größere TLBs sorgen dafür, dass mehr Instruktionen aufgenommen und weitergegeben werden können.

Über 12 Execution Ports wird das Front End gefüttert. Im Vergleich zu Sunny Cove gibt es einen zusätzlichen Integer Port, der anders als die restlichen nicht mit Spezialaufgaben betraut ist, sondern exklusiv die Standard-Befehlssätze entgegennehmen soll. Die dazugehörigen Vektor-Einheiten beherrschen grundsätzlich den aktuellen AVX-512-Umfang und können neben FP16-Berechnungen auch per AMX die entsprechenden Matrixberechnungen beschleunigen. AMX ist aber von einer Unterstützung der Software abhängig, was dann aber auch zu einer Beschleunigung in der Berechnung um den Faktor acht sorgen soll – unter idealen Bedingungen.

Die IPC-Leistung soll gegenüber dem Vorgänger um 15 % steigen. Für AVX-512 gibt es neue Erweiterungen, wie zum Beispiel vRAN, was im Edge-Bereich für Mobilfunkanwendungen interessant ist. Zudem gibt es tief integrierte Sicherheitsfunktionen wie CET, SGX und TDX.

Bis zu acht Prozessoren in einem Server

Während man bei den EPYC-Prozessoren weiterhin auf maximal zwei Prozessoren in einem 2S-System beschränkt ist, geht Intel mit Sapphire Rapids weiterhin den Weg auch 4S- und 8S-Systeme anbieten zu können. Natürlich muss man dabei auch sehen, dass AMD bei den aktuellen Genoa-Prozessoren bis zu 96 Kerne pro Sockel anzubieten hat, während es bei Intel derer 60 sind. Mit Bergamo sollen es bei AMD dann in Kürze sogar 128 sein. Auf zwei Sockel verteilt, kommt AMD also auf 192 bzw. 256 Kerne.

Intel propagiert für Sapphire Rapids eine besonders hohe Leistungsdichte der 4S- und 8S-Systeme. Bis zu 480 Kerne kann man so anbieten und bis zu 32 TB an Speicher.

Dazu gibt es auch eine leistungsorientierte Topologie namens 8S-4L, bei der einige I/O-Lanes wegfallen, dafür aber die Prozessoren untereinander möglichst schnell angebunden sind.

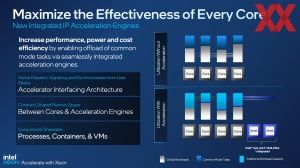

Viele Beschleuniger sollen die Kerne entlasten

Ein Fokus der vierten Xeon-Scalable-Generation sind Beschleuniger, die nun teilweise komplett neu sind oder nicht mehr Bestandteil des Chipsatzes, sondern ein Teil des Uncore-Bereichs im Prozessor. Folgende Beschleuniger stehen zur Verfügung:

- QAT (QuickAssist Technology): Ist nun Teil des Kerns und für Verschlüsselung und Kompression von Datenstreams vorgesehen. Network Secure Gateways und Content Delivery Networks sind zwei der denkbaren Anwendungen für QAT.

- DLB (Dynamic Load Balancer): Der DLB sorgt für ein besseres Load Balancing und eine bessere Auslastung der Kerne auch für wenig anspruchsvolle Workloads. Als eine QoS können bestimmte Pakete in der Pipeline auch priorisiert werden.

- DSA (Data Streaming Accelerator): Speicherzugriffe laufen nicht mehr über die Kerne, sondern teilweise ausgelagert werden. Dies kann für eine Datenanalyse und Distributive-Storage-Dienste sinnvoll sein.

- IAA (In-Memory Advanced Analytics Accelerator): Daten werden aus dem Speicher gelesen und in diesen geschrieben, die Dekompression und Kompression erfolgen im IAA und werden von dort in den LLC übertragen. In-Memory Datenbanken, Datenanalyse oder Datenbanken allgemein sind Anwendungsfelder von den IAA.

Daneben gibt es noch die Advanced Matrix Extensions (AMX). In jedem Prozessor-Kern hat Intel einen AMX-Beschleuniger verbaut.

In der Tabelle der Varianten von Sapphire Rapids (SKUs), auf die wir später einen Blick werfen, wird ersichtlich, welches Modell welche Beschleuniger und in welcher Anzahl enthält. An dieser Stelle kommt Intel On-Demand ins Spiel. Dabei handelt es sich um einen Dienst, bei dem für einige SKUs On-Demand-Funktionen hinzugebucht werden können, wenn das jeweilige Modell nicht schon die maximale Anzahl an Beschleunigern bietet.

Ein ein auf XCC-Dies basierender Prozessor bietet maximal:

- 4x DSA

- 4x QAT

- 4x DLB

- 4x IAA

Die Prozessoren auf Basis eines MCC-Dies kommen auf:

- 1x DSA

- 2x QAT

- 2x DLB

- 1x IAA

Das Hinzubuchen über den On-Demand-Dienst wird über die OEMs oder SIs angeboten. Intel stellt nur die Schnittstelle bereit. Verkauft der Anbieter seinem Kunden einen Server mit einem Prozessor-Modell, welches keine oder zu wenige Beschleuniger anzubieten hat, können dieser per On-Demand nachgebucht werden.

Die On-Demand-Dienste in dieser Form sind hoch umstritten. Die Hardware hat die Fähigkeiten bereits und wird künstlich beschnitten, nur um die Funktionen dann später zu aktivieren. Es ist nicht Intels erster Anlauf in dieser Hinsicht. Ob er dieses Mal Früchte tragen wird, wird sich zeigen müssen.

Während AMX und die AVX-Erweiterungen ein Bestandteil der CPU-Kerne sind, waren und sind die Beschleuniger ausgelagert – nur eben nicht mehr als Teil des Chipsatzes, sondern des SoCs selbst. Die Beschleuniger sind weiterhin als externe Hardware (ähnlich wie eine per PCIe oder CXL angebundene Hardware) verfügbar, auf die dann per Software zugegriffen wird. Der Accelerator Complex des XCC- und MCC-Dies ist mit an das Mesh angebunden.

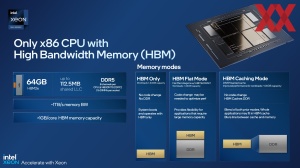

Max Series für HPC kommt mit HBM2e

Fünf Prozessoren der mehrere Dutzend umfassenden Produktpalette, sieht Intel speziell für das HPC-Segment vor. Diese Prozessoren zeichnen sich durch ein besonderes Ausstattungsmerkmal aus: Im Package integrierter HBM2e-Speicher. Die für HPC-Anwendungen optimierten Prozessoren bieten maximal 56 Kerne und reichen damit nicht an die bis zu 60 Kerne im Vollausbau heran, die Intel ohnehin nur für ein einziges Modell, den Xeon Platinum 8490H vorsieht.

Betrieben werden können die Xeon-Prozessoren mit dem zusätzlichen Speicher in drei Betriebsmodi: Im "HBM only"-Mode bootet der Server nur mit dem HBM2e-Speicher, ein zusätzlicher DDR5-Speicher ist nicht notwenig. Die Anwendungen und das Betriebssystem müssen nicht wissen, ob der HBM2e oder DDR5 verwendet wird. Auch die Software muss sich dessen nicht bewusst sein. Durch den "HBM only"-Mode ist es theoretisch denkbar, Hardware bzw. Server zu entwickeln, die gänzlich auf DDR-DIMMs verzichten und damit besonders kompakt sind.

Im "HBM Flat Mode" ist der HBM2e eine weitere Ebene in der Cache-Hierarchie. Sind die dort abgelegten Daten größer als 64 GB, werden sie in den Arbeitsspeicher ausgelagert. Eventuell sind hier Anpassungen im Code notwendig, damit es bei Datenmengen von mehr als 64 GB nicht zu einer geringeren Leistung kommt, als im reinen DDR5-Betrieb.

Der "HBM Caching Mode" ist ein automatischer Betrieb mit dem HBM2e als Cache für den Arbeitsspeicher. Es handelt sich dabei um eine Art Hybrid-Modus aus den beiden eben genannten Modi. Eine Anpassung der Software ist nicht notwendig.

Allesamt sind die Xeon-Prozessoren der Max-Serie mit 64 MB an HBM2e ausgestattet. Die Speicherbandbreite der vier Stacks liegt bei mehr als 256 GB/s pro Stack und dementsprechend bei mehr als 1 TB/s. Bei acht DDR4-Speicherkanälen kamen wir bisher auf 204,8 GB/s – nur um die Anbindung des HBM2e in ein Verhältnis setzen zu können.

Auch AMD bietet mit den EPYC-Prozessoren mit 3D V-Cache (Milan-X) Modelle mit größerem Cache an. Beim Leistung-pro-Watt-Verhältnis sieht sich Intel mit Sapphire Rapids dennoch deutlich besser aufgestellt – sowohl mit DDR5-Speicher als auch im "HBM only"-Mode. Dies betrifft Benchmarks wie HPL, HPCG und Stream Triad und gegenüber den eigenen Vorgänger Ice Lake-SP.

Die Xeon-Max-CPUs sollen die Kunden in die Lage versetzen, anstatt eines großen Servers mit vier Sockeln, 64 RAM-DIMMs und einer Leistungsaufnahme von 1.640 W gegen ein solches Modell mit nur zwei Xeon-Prozessoren mit HBM2e, ohne die Anschaffungskosten für DDR5-Speicher und mit einer Leistungsaufnahme von nur noch 700 W auszutauschen.

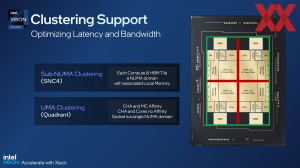

Für Server-Prozessoren auf Basis mehrere Chiplets zunehmend wichtig, werden die Latenzen und Bandbreiten zwischen den einzelnen Chips. Per Clustering können einzelne Knoten voneinander getrennt werden, sodass die Speicherzugriffe nicht über andere Chiplets laufen müssen, was die Latenzen erhöht.

Für Sapphire Rapids macht Intel ein Sub-NUMA Clustering zugänglich, welches als SNC4 bereits bekannt ist. Hier werden die vier Chiplets mit ihrem HBM und den dazugehörigen Speichercontrollern als einzelne Knoten betrachtet. Je nach Anwendung kann dies Sinn machen.

Mit dem UMA Clustering bietet Intel nun aber auch eine Möglichkeit, die CPU-Chiplets samt des dazugehörigen HBM als NUMA-Node festzulegen. Die Caching Agents und Speichercontroller wurden so optimiert, dass es keinerlei Nachteile hinsichtlich der Latenz geben sollte.

Soft- und Hardware gehen Hand in Hand

Sicherheit ist und bleibt ein Thema

In Cloud-Umgebungen und im Server-Segment allgemein spielt das Thema Sicherheit natürlich immer eine gewisse Rolle. Kein Kunde möchte, dass der ebenfalls auf dem gleichen Server ausgeführte zweite Kunde Zugriff auf die eigenen Daten hat. Per TDX (Trust Domain Extensions) können einzelne VMs isoliert werden. Der Cloud-Stack, das BIOS und die Firmware sowie das Host-OS und der Hypervisor sind außen vor.

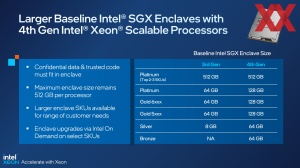

Die SGX (Software Guard Extensions) gehen dabei noch einen Schritt weiter. Dabei können Daten in einer Secure Enclave abgelegt werden, die aber auch schon von Sicherheitslücken betroffen und per Angriff geöffnet wurden. Die Kapazität der Secure Enclave wird mit der vierten Xeon-Scalable-Generation über die Serien etwas vergrößert. Noch immer sind 512 GB das Maximum. Vor allem aber in den kleineren und mittleren Serien wächst die Kapazität der Secure Enclave. Per On-Demand kann auch die Secure Enclave auf ein Maximum von 512 GB vergrößert werden.

OneAPI führt alles zusammen

Die OneAPI ist Intels sogenannte Full-Stack-Lösung, die mehrere Architekturen, Plattformen und Frameworks zusammenführt. Es gibt mehrere Toolkits (Base Toolkit, HPC Toolkit, AI Analytics Toolkit, Rendering Toolkit, IoT Toolkit), welche die Anwendungsbereiche etwas aufgliedern, aber das finale Ziel der OneAPI ist es eine zentrale Basis für alle Entwicklungen zu sein – ähnlich wie dies NVIDIA mit CUDA gelungen ist.

Somit soll es dem Anwender letztendlich egal sein, auf welcher Hardware er seine Software ausführt bzw. die OneAPI sorgt dafür, dass die Anwendungen möglichst effizient dort laufen, wie sie am schnellsten sind. PyTorch, TensorFlow sind nur einige wenige, wenngleich wichtige Programmbibliotheken, die unterstützt werden.

Zudem gibt es auch Übersetzungsschichten. So kann auf CUDA ausgelegter Code ausgeführt werden und soll dabei nur wenig Overhead mitbringen, wenn er per SYCL in die OneAPI überführt wird.

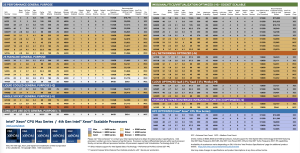

Übersicht aller CPU-Modelle

Insgesamt umfasst die vierte Xeon-Scalable-Generation 52 Modelle. Wie üblich sind diese in die Kategorien Platinum (8000er Serie), Gold (5000er und 6000er Serie), Silver (4000er Serie) und Bronze (3000er Serie) aufgeteilt. Hinzu kommen die HPC-Varianten mit HBM2e, die außerhalb dieser vier Serien laufen.

Darüber hinaus bietet Intel innerhalb dieser Serien auf bestimmte Anwendungen optimierte Modelle bzw. komplette Serien:

- Cloud: P-, V-, M-Serie

- Netzwerk: N-Serie

- Storage: S-Serie

- 1-Socket: U-Serie

- Long-Life Use: T-Serie

- IMDB, Analytics, VM optimiert: H-Serie

- Wassergekühlt: Q-Serie

Die obige Tabelle enthält alle SKUs, die Intel heute offiziell vorstellt. Die maximale Anzahl an Kernen beläuft sich auf 60, wird aber nur bei einem Modell (Xeon Platinum 8490H) angeboten. Innerhalb der Serien ist meist bei 52 bis 56 Kernen Schluss. Dies ist sicherlich auch ein Hinweis darauf, wie gut es um die Ausbeute bei Intel bestellt ist, wenn derart wenige Chips mit vollen 15 Kernen zu vier Chips zusammengepackt werden können. Die TDP dieser Modelle mit 52 oder mehr Kernen liegt bei 300 bis 350 W.

Hinsichtlich der Taktraten gibt es die gewohnte Abwägung: Je mehr Kerne für eine bestimmte TDP-Klasse, desto geringer sind die All-Core-Turbo-Taktraten und der Basis-Takt. Einige Modelle legt Intel auf einen hohen Boost-Takt auf einzelnen Kernen aus. Viele der Modelle bieten zudem die Unterstützung der Intel Speed-Select-Technologie (Intel SST) und darin die Funktionen wie Intel SST Base Frequency (SST-BF), Intel SST Core Power (SST-CP) und Intel SST Turbo Frequency (SST-TF). Hier können dann einzelne Kerne priorisiert behandelt werden und erreichen höhere Taktraten.

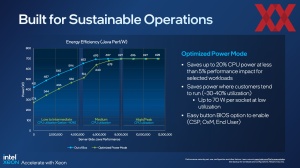

Intel bietet mit den Sapphire-Rapids-Prozessoren auch einen sogenannten Optimized Power Mode, bei dem die Leistungsaufnahme um 20 % reduziert wird, dabei sollen aber nur 5 % an Leistung verloren gehen.

Die kleinsten Modelle haben acht Kerne. Die TDP liegt hier je nach Serie bei 125 bis 150 W. Teilweise geht Intel bei diesen Modellen auch von DDR5-4800 auf DDR5-4400 zurück, was für den 2DPC-Betrieb ja ohnehin der Fall ist.

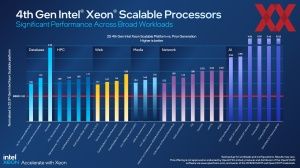

Intels eigene Benchmarks

Wie für einen solchen Start üblich, präsentiert Intel auch umfangreiche Benchmarks zu fast jedem erdenklichen Anwendungsbereich. Bereits über die vergangenen Monate hinweg wurden immer wieder Folien gezeigt, welche für bestimmte Anwendungen die Vorsprung gegenüber der Konkurrenz darlegen sollen. Auch zu HBM2e-Modellen gab es solche Daten in der Vergangenheit bereits.

Intel vergleicht hier zumeist aber auch gegen die eigene Vorgänger-Generation oder in ausgewählten Fällen auch gegen Broadwell, um einen längeren Update-Zyklus so mancher Kunden abzudecken. Hier und da wird auch gegen Milan-X vergleichen, um den Vorteil des wesentlich größeren HBM2e-Speichers zu verdeutlichen.

Besonders unter Einsatz der Beschleuniger sieht sich Intel weit im Vorteil. AI/ML-Anwendungen stehen dabei ebenso im Fokus wie Datenbank- und Netzwerk-Anwendungen, wo bestimmte Aufgaben im Verarbeitungsprozess auf die Beschleuniger ausgelagert werden können.

Eigene Benchmarks können wir zum aktuellen Zeitpunkt keine präsentieren. Die Kollegen von ServeTheHome und Phoronix sollten zum heutigen Start aber entsprechende Artikel vorbereitet haben.