Werbung

Am 13. Juni wird AMD unter dem Motto "AMD Data Center and AI Technology Premiere" einen Datacenter-Event veranstalten, bei dem es vor allem im Neuigkeiten rund um den Serverbereich geht. Erwartet wird, dass AMD seine für Cloud-Anwendungen optimierten EPYC-Prozessoren mit Codenamen Bergamo vorstellt und auch zum Beschleuniger MI300A sollte es weitere Informationen geben.

Dylan Patel und Gerald Wong haben auf Semianalysis.com bereits eine Analyse dessen veröffentlicht, was AMD in Form der Zen-4c-Architektur präsentieren wird. Bisher nutzt AMD für jede CPU-Generation eine einheitliche Architektur, die dann für die Ryzen- und EPYC-Prozessoren verwendet wird. Eine Unterscheidung durch unterschiedliche Cache-Kapazitäten oder das Abschalten einzelner Funktionseinheiten wie bei Intel gab es bisher nicht. Zen 4c besitzt aber zahlreiche Anpassungen, die es AMD überhaupt erst ermöglichen, bis zu 128 Kerne im SP5-Package unterzubringen.

AMD nimmt hier schon einen Schritt vorweg, den Intel ab 2024 mit Sierra Forest gehen will. Um die Effizienz der Prozessoren weiter zu erhöhen kommen kleine und sparsame Kerne zum Einsatz.

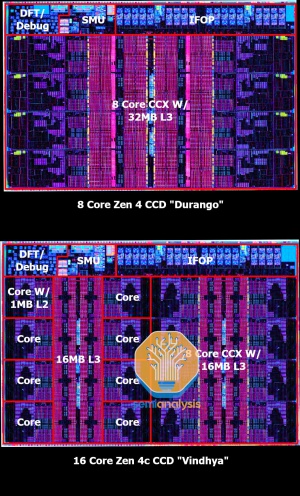

Für AMD bzw. das Bergamo-Design angepeilt sind doppelt so viele Kerne auf einem Core Complex Die (CCD) unterzubringen. Dabei soll die Chipfläche aber nicht gleich doppelt so groß ausfallen. In 5 nm gefertigt schaffte AMD die Verdopplung der Kern-Anzahl, das CCD wächst aber nur um 10 %.

Erreicht wird dies durch eine Halbierung des L3-Caches für einen Core Complexes (CCX). Dieser ist nun nur noch 16 MB groß. Statt einem CCX mit acht Kernen wie bei Zen 4 sind es hier nun zwei CCX mit jeweils acht Kernen, aber eben auf Basis von Zen 4c. Die L1- und L2-Caches bleiben mit 32 kB (Instruktionen und Data) und 1 MB unangetastet. Auf einem CCD ist der L3-Cache weiterhin 32 MB groß, aber pro Kern steht eben nur die Hälfte zur Verfügung.

Um weiter Platz zu sparen, verzichtet AMD auf die Durchkontaktierungen (TSVs). Diese befinden sich im Zen-4-CCD im Bereich des L3-Cache (Signaling) sowie des L2-Cache (Power/Control). Die Bergamo-Prozessoren wird es nicht mit 3D V-Cache geben – insofern kann AMD darauf verzichten dafür Platz vorzusehen.

Weniger Takt spart Platz und Transistoren

Die EPYC-Prozessoren mit Zen-4c-Kernen werden einen etwas niedrigeren Basis-Takt bieten, verzichten aber vor allem auf hohe Boost-Taktraten. Auch dies ist eine Maßnahme, um Platz einzusparen. Denn Hochfrequenz-Designs benötigen mehr Transistoren, entspanntere Zell-Bibliotheken und verbrauchen somit Fläche. Außerdem soll die Effizienz der Prozessoren besonders gut sein. Also wird auf das extra Quäntchen Leistung verzichtet.

Leiter, die auf einem Chip von A nach B geführt werden können zudem länger werden. Auch das macht das Design einfacher, da Blöcke nicht mehr gezwungenermaßen dicht zusammenliegen müssen, sondern wortwörtlich entspannter im Floorplan untergebracht werden können.

Auch nutzt AMD die bisherigen Erfahrung im Design der Zen-4-Prozessoren. Ein Kern besteht aus mehreren Partitionen an Funktionseinheiten (Fließkommaeinheiten, ganzzahlige Berechnungseinheiten, Sprungvorhersage, Load/Store, Caches, µOP-Cache, Decode, usw.) die allesamt getrennt voneinander entwickelt und dann zusammengebracht werden. Somit lässt sich die Fläche auch hier nicht immer ideal nutzen, da wir immer von rechteckigen Blöcken sprechen, die Freiräume haben können und zusammengesetzt werden, was im Zweifel große Lücken lässt.

Doch vom bestehenden Zen-4-Design weiß man nun, was wie funktioniert und muss einzelne Blöcke im Zweifel nicht mehr ändern. So lassen sich diese deutlich besser zusammenfassen. Entsprechend schrumpft ein einzelner Kern deutlich zusammen.

Wie so häufig ist ein solches Design auch immer eine Zusammenarbeit zwischen AMD und seinem Auftragsfertiger TSMC. Diese habe über ihre Packagung-Technologien AMD überhaupt erst in die Lage versetzt, das Chiplet-Design in dieser Form so weit zu entwickeln. Für Bergamo greift AMD auf neue 6T-SRAM-Zellen zurück. Bisher verwendet man 8T-Zellen. Pro 1 Bit im SRAM spart man also ein viertel an Transistoren und damit auch Platz ein. An diese Zellen führen auch nur noch zwei statt vier Leitungen, was wieder die notwendige Chipfläche reduziert. Statt eine Dual-Port-SRAM, der gleichzeitig gelesen und beschrieben werden kann, hat man nun einen SRAM, der bei steigender und fallender Taktflanke gelesen und beschrieben wird.

Acht CCDs für 128 Kerne

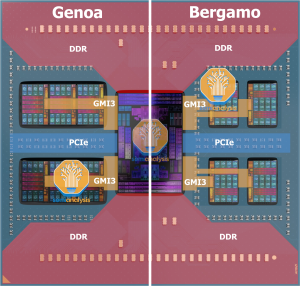

Zusammen mit dem bekannten IOD, der zudem die Plattform zu SP5 kompatibel hält, bringt AMD acht CCDs mit jeweils 16 Kernen im Package unter. Somit kommen wir hier auf 128 Kerne, die ein EPYC-Prozessoren im Bergamo-Design anzubieten hat. Das Angebot an PCI-Express-Lanes (128x PCIe 5.0) und 12 Speicherkanälen (12x DDR5-4800) bleibt unangetastet.

Die finalen Produktspezifikationen der EPYC-Prozessoren wird es dann zum Event am 13. Juni geben. Bei der Analyse handelt es sich auch noch nicht im offizielle Informationen, die von AMD in dieser Form verkündet wurden, sondern eben um eine Analyse von gewöhnlich gut informierter Quelle.