Werbung

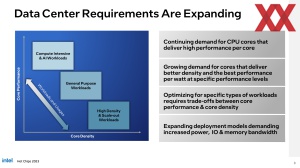

Auf der HotChips 2023 hat Intel über seine kommende Plattform namens Birch Stream gesprochen, die ab dem kommenden Jahr mit dem E-Kern-Xeon Sierra Forest und P-Kern-Xeon Granite Rapids ihre Premiere feiern wird. Die Aufspaltung in E- und P-Kern-Xeons soll Intel dabei helfen die Marktsegmente im Serverumfeld besser abzudecken. Angekündet hat man diesen Schritt bereits vor einigen Monaten.

Mitte Juni stellte AMD mit dem Bergamo-Designs seine ersten EPYC-Prozessoren mit 4C-Kernen vor, die ebenfalls auf eine maximale Effizienz und eine hohe Anzahl an Kernen ausgelegt sind. Auf Seiten der ARM-Prozessoren wie der Ampere-Familie, aber auch den Custom-Designs wie sie sich zum Beispiel Amazon selbst herstellen, ist der Trend zu kleinen aber effizienten Kernen ebenfalls klar erkennbar.

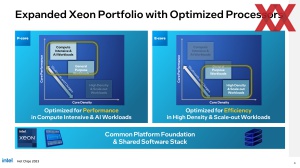

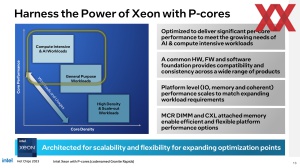

Im kommenden Jahr soll es also auch bei Intel losgehen. Zur HotChips gab es die ersten Details. Bereits bekannt und nun noch einmal bestätigt wurde, dass Sierra Forest und Granite Rapids in der Form kompatibel zueinander sind, dass Intel hinsichtlich der Fertigung auf die gleichen I/O-Blöcke, sprich PCI-Express 5.0, CXL 2.0, Speicherinterfaces setzt. Einzig die Compute Tiles mit den CPU-Kernen sind unterschiedlich gestaltet. Für den Nutzer der Birch-Stream-Plattform bedeutet dies zudem, dass er sich bei den Prozessoren nicht auf ein Modell festlegen muss, sondern theoretisch wechseln kann. Nun wird es in der Praxis weniger häufig vorkommen, dass ein Server mit anderen Prozessoren bestückt wird, denn im Vorfeld sollte abgewogen werden, ob die P- oder die E-Kern-Modelle die richtige Wahl sind. Aber eine einheitlich Plattform hat aus Sicht der Software-Unterstützung natürlich große Vorteile.

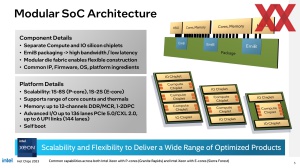

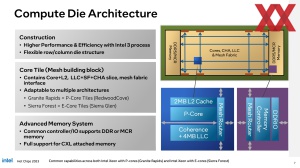

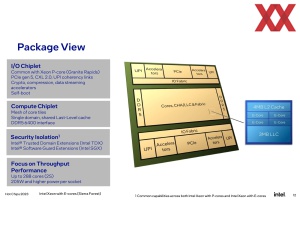

Für Sierra Forest und Granite Rapids immer zum Einsatz kommen zwei I/O-Tiles pro Package. Damit wird das einheitliche I/O-Angebot gewährleistet. Dann gibt es eine unterschiedlicher Anzahl an Compute-Tiles. Die Spanne reicht von einem, offenbar etwas größere, bis zu drei etwas kleineren. Die Verbindungen auf dem Package werden per EMIB-Technologie hergestellt. Gefertigt werden die Compute-Tiles in Intel 3. Dies hatte Intel aber schon mehrfach angekündigt.

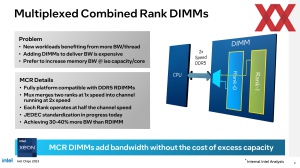

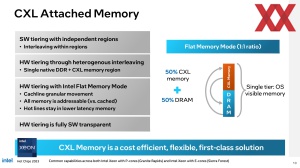

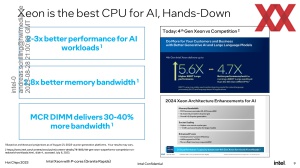

Die Granite-Rapids-Prozessoren wird es für 1S- bis 8S-Server geben. Sierra Forest wird als 1S- oder 2S-Modell erscheinen und damit maximal zwei Sockel unterstützen. Bis zu 12 Speicherkanäle können die Prozessoren ansprechen. Auf unserer Tech Tour bei Intel in Malaysia haben wir neue Server-Testsysteme gesehen, die DDR5-5600 unterstützen werden. Für die Birch-Stream-Plattform gehen wir daher davon aus, dass auch diese mindestens DDR5-5600 unterstützen wird. Neben DDR4-Speicher wird auch MCR unterstützt. Hinsichtlich des I/O-Angebotes spricht Intel auch erstmals konkret von 144 Lanes (PCI-Express 5.0 / CXL).

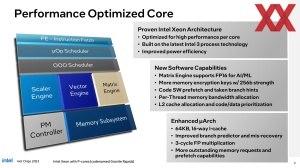

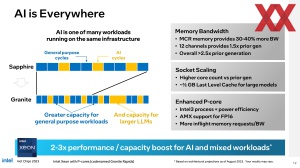

Für die dann neuen Performance-Kerne spricht Intel von Optimierungen im Bereich der Effizienz, will aber zugleich auch eben die beste Leistung in diesem Segment liefern. Dazu hat man auch Rückmeldungen seiner Kunden mit einbezogen und die Flaschenhälse in der Architektur neu evaluiert. Die AMX-Einheiten bekommen für AI-Anwendungen die Unterstützung von FP16. Der L1 Instruction Cache soll 64 kB groß sein. Bei den noch aktuellen Golden-Cove-Kernen sind es nur 32 kB. Darüber hinaus spricht Intel von einer verbesserten Sprungvorhersage und einem optimierten Fließkommadurchsatz. Mit Core- und Cache-Isolierung soll die Leistung der Kerne dennoch auf einem hohen Niveau verbleiben.

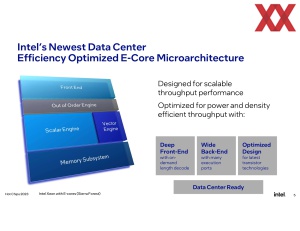

Etwas mehr Informationen gibt es zur Mikroarchitektur der Efficiency-Kerne. Durchsatz und Effizienz sind hier die Designziele gewesen, die im Fokus standen. Dazu hat man sich vor allem der Cache-Architektur gewidmet. Der L1-Instruction-Cache umfasst 64 kB – genau wie bei den Performance-Kernen. Um einen hohen Durchsatz zu erreichen spendiert Intel dem E-Kernen 6-wide Decode-, 5-wide allocate und 8-wide Reite, womit die E-Kerne auf Niveau der P-Kerne von Sapphire Rapids liegen. Den E-Kernen zur Seite gestellt werden können 4 MB an L2-Cache.

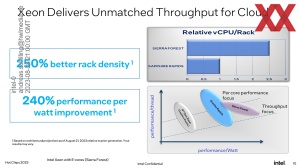

In einer Art Performance-Vorschau spricht Intel von einem um den Faktor 2,5 höheren Rack-Density durch den Einsatz von Sierra Forst. Dies dürfte sich auf die Anzahl der Kerne beziehen. Können die aktuellen Sapphire-Rapids-Prozessoren mit 2x 60 Kernen auf 2U aufwarten, dürften es bei Sierra Forest demnach 300 oder mehr sein. 2x 144 Kerne wurden in den Gerüchten mal gehandelt. Granite Rapids soll etwas später ein wesentlich besseres Leistung/Watt-Verhältnis bieten können. Für Sierra Forest gilt dies natürlich ebenso.

Sierra Forest ist für die erste Jahreshälfte 2024 geplant. Granite Rapids erscheint etwas später. Weitere Details gibt es dann sicherlich ebenfalls in der ersten Jahreshälfte des kommenden Jahres. Bis dahin wird es aber mit Emerald Rapids noch eine weitere Xeon-Generation geben, die auf kleinere Verbesserungen nach Sapphire Rapids aufbauen wird.

Update:

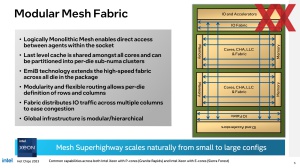

Alle obigen Informationen haben wir im Vorfeld von Intel erhalten. Auf der HotChips selbst gab Intel nun aber auch die finalen Präsentationen, die noch einige Informationen ergänzen. So fehlen in der gehaltenen Präsentation die Leistungs-Implikationen, die wir oben in einer Doppelgalerie besprochen haben. Zudem gewährt Intel einen Einblick in das Mesh zur Kommunikation zwischen den einzelnen Chiplets sowie nennt weitere technischen Details zu den E- und P-Kernen.

Der Mesh Fabric ist ein zentraler Bestandteil der letztendlich dafür sorgen muss, dass ein Multichip-Design eine ähnliche Leistung wie ein monolithischer Chip erreicht. Jeder zentraler Baustein der Compute-Tiles besitzt einen Mesh Router, der diesen Block an den Rest des Netzwerks anbindet. Die Compute-Tiles beinhalten die Speichercontroller und in den Core Tiles die einzelnen Performance-Kerne – allesamt besitzen diese Blöcke einen Mesh Router.

Die Core Tiles bestehen aus den folgenden Komponenten:

- Performance-Kern

- 2 MB an L2 Cache

- 4 MB LLC Slice (kohärent über alle Kerne)

- Caching und Home Agent (CHA)

- Mesh Router

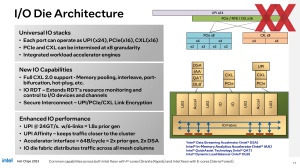

Jeder der kommenden Xeon-Prozessoren besitzt zwei I/O-Chiplets. Diese bestehen wiederum aus acht Ports, die als UPI (x24), PCI-Express (x16) oder CXL (x16). Ebenfalls ein Bestandteil sind zwei Accelerator Complexe (AC), die wiederum die verschiedenen Beschleuniger-Typen enthalten. UPI und der Interface zu den Beschleunigern soll um den Faktor 1,8 bzw. 2 schneller sein als die aktuell der Fall ist.

Noch mehr Details zu den E-Kernen

Zu den Efficiency-Kernen (Crestmont) bot Intel auf der HotChips sogar noch deutlich mehr Informationen an, als dies für die Performance-Kerne (Redwood Cove) der Fall ist.

Ein tiefes Front-End für effizientes Decoding der Instruktionen und eine breites Back-End für einen möglichst hohen Durchsatz der Berechnungen sollen die E-Kerne von Sierra Forest auszeichnen. Die 64 kB an Instruction Cache sind Teil des tiefen Front-Ends, denn er ist damit auf die aktuellen Anwendungen mit großen "Code Footprint" ausgelegt. Mit 64 kB wird der L1I-Cache im Vergleich zum Vorgänger zwar nicht größer, liebt aber auf Niveau des L1I-Cache der Performance-Kerne.

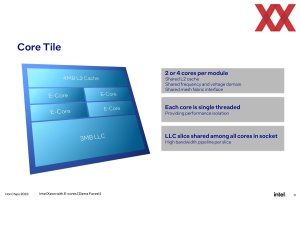

Das Core Tile der E-Kern-Xeon-Prozessoren kann aus zwei oder vier der Crestmont-Kerne bestehen. Diese teilen sich einen 4 MB großen L2-Cache. Der LLC ist pro Tile 3 MB groß und wird mit den weiteren Core Tiles geteilt. Die Kerne unterstützen nur einen Thread pro Kern.

Während Intel für die P-Kern-Xeons offenbar zwei Packages mit jeweils zwei I/O-Tiles und einem oder zwei Compute Tiles vorsieht, ist bei den E-Kern-Xeons offenbar nur ein Compute Tile vorgesehen. Dieses beinhaltet bis zu 144 E-Kerne. Intel spricht hier von einer "Single Domain" mit geteiltem LLC.

Mit den 144 Kernen können wir auch gleich den Gesamtausbau an L2-Cache und LCC/L3-Cache ausrechnen. Mit 4 MB L2-Cache für vier Kerne sind insgesamt also 144 L2-Cache zum Einsatz. Für den LLC/L3-Cache sprechen wir von insgesamt 108 MB.

Am Compute-Tile angebunden sind die Speichercontroller. Birch Stream unterstützt bis zu 12 Speicherkanäle und auch den MCR-RAM (Multiplexed Combined Rank). DDR5-6400 werden der neue Standard ab dieser Generation sein. Die TDP der Sierra-Forest-Prozessoren wird bei 205 W liegen.

Update: Package von Granite Rapids

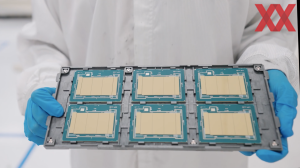

In einem Marketing-Video informiert Intel über die Entwicklung im Bereich des Packaging und zeigt hier mehrfach das Package, welches wir als Granite Rapids identifiziert haben. Zwar wird dieses Produkt nicht explizit genannt, der Aufbau aber deutet klar auf Granite Rapids hin.

Das Package besteht in diesem Fall aus drei Compute-Chiplets, in denen die CPU-Kerne sitzen. Hochkant ausgerichtet (wie auf dem ersten Bild) sitzen oben und unten jeweils ein I/O-Chiplet. Bei unserem Besuch der Packaging-Werke von Intel in Malaysia haben wir Chips für Emerald Rapids gesehen. Die fünfte Xeon-Generation wird vor der P- und E-Kern-Aufspaltung in Form von Granite Rapids und Sierra Forest noch in diesem Jahr erscheinen.