Werbung

Einen Prozessor zu entwickeln setzt einerseits eine gewisse Expertise voraus, man benötigt aber auch die entsprechenden Kompetenzen und Lizenzen. Kosten und die für die Entwicklung notwendige Zeit sind ein wichtiger Faktor. Mehrere hundert Millionen Euro an Entwicklungskosten fallen für ein modernes Design an. ARM bietet über sein Lizenzmodell zumindest schon einmal die Möglichkeit, ein Design eines CPU-Kerns verwenden zu dürfen. Die Implementierung dieses Kerns und des gesamten Chips muss der gewillte Kunde aber noch immer selbst übernehmen.

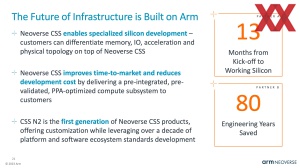

Außerdem bietet ARM mit seinen Neoverse-Designs bereits eine Art Referenzdesign für Serverprozessoren an, welches vom Lizenznehmer weitestgehend übernommen werden kann, aber auch dann muss er sich noch um viele Entwicklungsschritte kümmern, die Zeit und Geld kosten, bis am Ende ein funktionierender Prozessor dabei herauskommt.

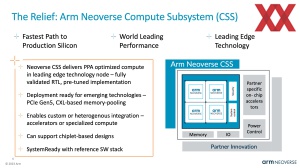

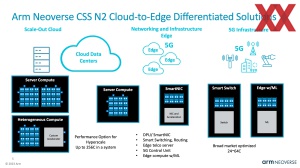

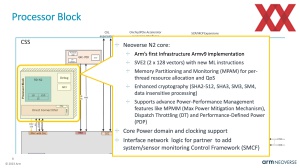

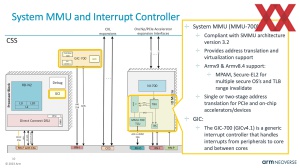

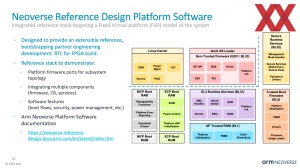

An dieser Stelle kommt nun das Arm Neoverse Compute Subsystem (CSS) ins Spiel. Mit dem Neoverse CSS N2 (CSS Genesis) bekommen die Kunden ein fertiges Design, welches bis auf wenige Schritte alles anzubieten hat, um am Ende den Prozessor aus der Foundry zu bekommen. Dies beinhaltet die Verifikation, Integration von Drittanbieter-IP, wiederum die entsprechende Verifikation dessen, ein FPGA-Image zur Simulation des Prozessors, die Back-End-Implementation und vieles mehr. Letztendlich sollen damit 80 "Engineering Years", also 80 Arbeitsjahre der sonst notwendigen Ingenieure eingespart werden können.

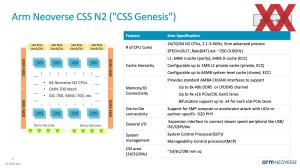

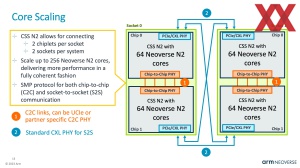

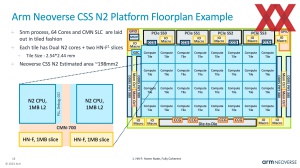

Das Neoverse-CSS-N2-Design ist zudem sehr flexibel. Der Kunde kann zwischen 24, 32 und 64 Kernen auswählen, die mit 2,1 bis 3,6 GHz arbeiten. Der L1-Instruction- und Data-Cache sind immer 64 kB groß. Der L2-Cache kann bis zu 1 MB groß sein, der L3-Cache/LLC bis zu 64 MB über alle Kerne hinweg.

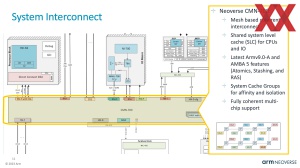

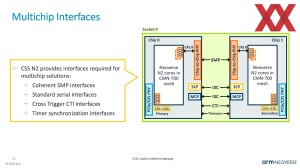

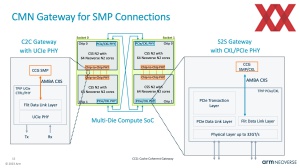

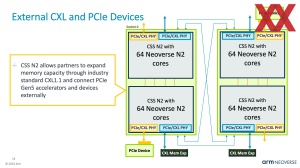

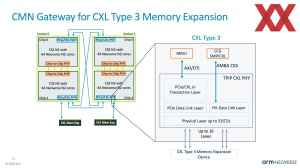

An I/O angebunden werden können bis zu acht DDR5-Speicherkanäle sowie vier Blöcke mit jeweils 16 PCI-Express- oder CXL-Lanes. Für eine weitere Skalierung ist es möglich, zwei dieser Chips per D2D-PHY (Die to Die) miteinander zu verbinden, so dass bis zu 128 Kerne in einem Package möglich sind.

Die wichtigsten Details der Neoverse-N2-Kerne kennen wir bereits. Sie sind die Armv9-Umsetzung und bieten und anderem 2x 128 Bit Vektor-Einheiten (SVE2) mit den aktuellen AI-Instruktionen. Die Neoverse-N2-Kerne sind vor allem auf eine hohe Effizienz ausgelegt und unterstützen zudem die wichtigsten Kryptografie-Funktionen.

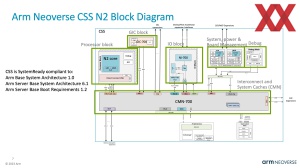

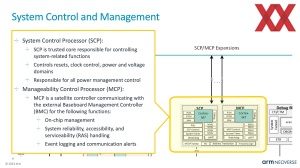

Zum Design gehören zudem jeweils ein System-Control- (SCP) und Management-Control-Prozessor (MCP), die auf jeweils einem Cortex-M7 aufsetzen. Sie kontrollieren das Power-Management und damit die Leistung einzelner Kerne. Über eine dedizierte Takt- und Spannungskontrolle sorgen sie für eine möglichst hohe Effizienz.

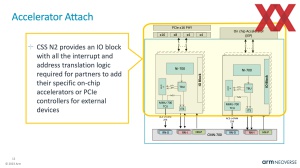

Per PCI-Express lassen sich externe Beschleuniger anbinden. Ein D2D-Interface ermöglicht – wie bereits erwähnt – das Verbinden zweier Chips auf einem Package. Per CXL lassen sich mehrere Prozessoren auf Socket-to-Socket-Ebene (S2S) miteinander koppeln. Als Interconnect-System wird das Neoverse CMN-700 verwendet.

In einer Referenzimplementation in 5 nm gefertigt kommt ein Tile, bestehend aus zwei N2-Kernen sowie 1 MB an L2-Cache und einem 1 MB Slice an LLC auf eine Größe von 6,2 mm². Ein Neoverse CSS N2 mit 24 Kernen kommt auf 53 mm², mit 32 Kernen auf 61 mm² und mit 64 Kernen auf 198 mm².

CSS N2 soll nur eine erste Variante einer solchen Referenzimplementation sein. Über mögliche weitere Varianten, beispielsweise auf Basis des Neoverse V2, spricht ARM zum jetzigen Zeitpunkt aber noch nicht. Neoverse N2 ist in Anbetracht des Bedarfs an Cloud-Prozessoren die offensichtlichste Wahl. 13 Monate sollen nun vergehen, bis vom Start einer Umsetzung des Neoverse CSS N2 ein fertiger Prozessor vom Band läuft.

Ebenfalls auf der HotChips 2023 von ARM detaillierter vorgestellt wurde die Implementation des Neoverse V2, die unter anderem von NVIDIA im Grace CPU Superchip verwendet wird. Dazu werden wir noch eine gesonderte Meldung verfassen.