Werbung

Zunächst tauchten die Bilder im Rahmen eines Marketing-Video auf, nun hat Intel eine ganze Reihe interessanter Fotos veröffentlicht. Die Fotos beschäftigen sich mit dem Thema Packaging und zeigen auf, zu was man hier inzwischen in der Lage ist. Bei unserem Besuch der Packaging-Werke von Intel in Malaysia haben wir ebenfalls einige interessante Packaging-Technologien gesehen. Das was hier vom Band läuft, ist aber entweder schon in Produktion oder wird in Kürze in Massenproduktion übergehen.

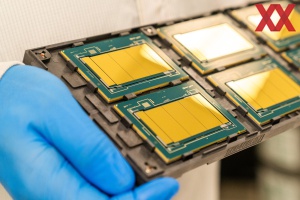

Die nun von Intel veröffentlichten Bilder zeigen das, was in Chandler, im US-Bundesstaat Arizona in Intels "Assembly und Test Technology Development-Bereich" bereits passiert. Gezeigt wird unter anderem Granite Rapids, also Intels übernächste Xeon-Generation, die in P- und E-Kern-Prozessoren (Granite Rapids bzw. Sierra Forest) aufgeteilt wird.

Das Package besteht in diesem Fall aus drei Compute-Chiplets, die in der Mitte platziert werden und in denen die CPU-Kerne sitzen. Im Querformat ausgerichtet (wie auf dem ersten Bild zu sehen) sitzen oben und unten jeweils ein I/O-Chiplet.

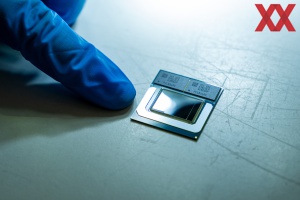

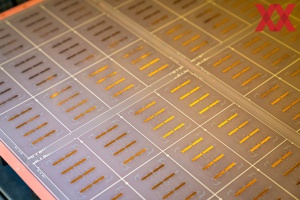

Außerdem zu sehen gibt es das organische Package-Substrat-Panel mit den schmalen, länglichen EMIB-Chips. Wie klein diese EMIB-Chips sind, zeigt abschließend folgendes Foto:

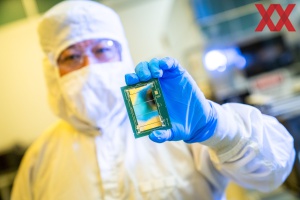

Meteor Lake mit LPDDR5X On-Package

Ein weiteres Fotos zeigt einen Meteor-Lake-Chip mit seinen vier Chiplets (Compute-Tile, SoC-Tiles, Graphics-Tile und I/O-Tile), aber mit auf dem Package sitzt auch der Arbeitsspeicher.

Neben der besseren Integration und dem geringeren Platzbedarf hat ein solches Package womöglich auch noch weitere Vorteile. Der Verwendete LPDDR5X stammt offenbar von Samsung (K3KL3L30CM). An der Speicherbandbreite ändert sich wenig im Vergleich zur weiter entfernten Anbindung von LPDDR5X, wohl aber bei der Latenz. Apple platziert den Arbeitsspeicher für seine M-Chips ebenfalls direkt auf dem Package. Über die Max- und Ultra-Serie dieser Chips verwendet Apple andere Ausbaustufen der M-Chips, aber auch eine verschieden große Anzahl an LPDDR5X-Chips im Package. Über die Anzahl der Chips skaliert Apple die Kapazität und Speicherbandbreite.