News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Packaging

-

Broadcom 3.5D XDSiP: TSMCs CoWoS als Basis für Broadcom’s 3.5D-Plattform

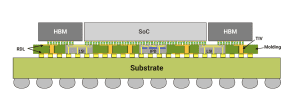

Erst Ende November präsentierte TSMC auf dem Open Innovation Platform eine Weiterentwicklung des Packaging mittels Chip-on-Wafer-on-Substrate (CoWoS). Nun verkündet Broadcom eine Weiterentwicklung seines Packaging mittels 3.5D eXtreme Dimension System in Package (3.5D XDSiP). 3.5D XDSiP verwendet dabei CoWoS von TSMC. Das, was TSMC präsentierte, soll ab 2027 ein CoWoS-Packaging mit Chiplets, gefertigt in A16, zusammen mit... [mehr]

Erst Ende November präsentierte TSMC auf dem Open Innovation Platform eine Weiterentwicklung des Packaging mittels Chip-on-Wafer-on-Substrate (CoWoS). Nun verkündet Broadcom eine Weiterentwicklung seines Packaging mittels 3.5D eXtreme Dimension System in Package (3.5D XDSiP). 3.5D XDSiP verwendet dabei CoWoS von TSMC. Das, was TSMC präsentierte, soll ab 2027 ein CoWoS-Packaging mit Chiplets, gefertigt in A16, zusammen mit... [mehr] -

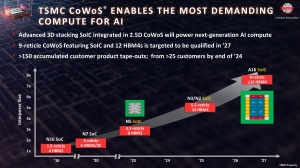

Interposer mit 12x HBM4: TSMC CoWoS soll ab 2027 riesige Packages ermöglichen

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann. In... [mehr]

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann. In... [mehr] -

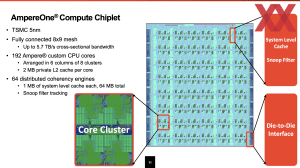

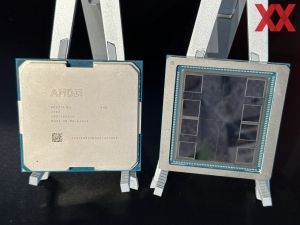

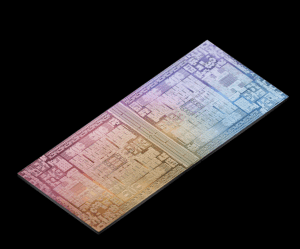

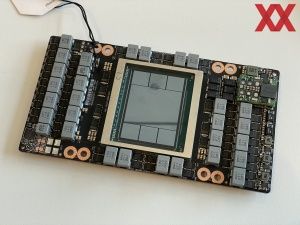

5 nm, HBM3E und aufwändiges Packaging: Hersteller protzen mit High-End-Chips

Nicht kleckern, sondern klotzen – so könnte das Motto der diesjährigen Hot-Chips-Konferenz lauten. Die Hersteller überbieten sich mit immer größeren und letztendlich auch schnelleren Chips, doch der Aufwand der betrieben wird ist ebenfalls enorm. Über NVIDIAs Blackwell-GPU haben wir ebenfalls bereits berichtet wie über den Telum II von IBM, der mit gigantischen Caches aufwarten kann. Auch Intels Xeon 6 SoC alias Granite Rapids-D ist mit zwei... [mehr]

Nicht kleckern, sondern klotzen – so könnte das Motto der diesjährigen Hot-Chips-Konferenz lauten. Die Hersteller überbieten sich mit immer größeren und letztendlich auch schnelleren Chips, doch der Aufwand der betrieben wird ist ebenfalls enorm. Über NVIDIAs Blackwell-GPU haben wir ebenfalls bereits berichtet wie über den Telum II von IBM, der mit gigantischen Caches aufwarten kann. Auch Intels Xeon 6 SoC alias Granite Rapids-D ist mit zwei... [mehr] -

Packaging und R&D: Intel stoppt Projekte in Italien und Frankreich

Ein schon fast zwei Wochen alter Artikel auf Politico spricht davon, dass Intel seine Großinvestitionen in Frankreich und Italien komplett eingestellt habe. Angekündigt wurde eine größere R&D-Abteilung in Frankreich sowie ein Werk für das Advanced Packaging in Italien zum gleichen Zeitpunkt wie auch die Fab für Deutschland bei Magdeburg. Bereits im März äußerte sich der italienische Minister Urso jedoch, dass Intel "seine... [mehr]

Ein schon fast zwei Wochen alter Artikel auf Politico spricht davon, dass Intel seine Großinvestitionen in Frankreich und Italien komplett eingestellt habe. Angekündigt wurde eine größere R&D-Abteilung in Frankreich sowie ein Werk für das Advanced Packaging in Italien zum gleichen Zeitpunkt wie auch die Fab für Deutschland bei Magdeburg. Bereits im März äußerte sich der italienische Minister Urso jedoch, dass Intel "seine... [mehr] -

Halbleitersubstrate: AMD und Samsung wollen zusammenarbeiten

In einer in der Nacht veröffentlichten, inzwischen aber wieder gelöschten Pressemitteilung, verkünden die Halbleitersparte von Samsung und AMD eine zukünftige Zusammenarbeit. Konkret sollen Hochleistungsplatinen für Hyperscale-Rechenzentren gefertigt werden. Warum Samsung die Pressemitteilung zurückgezogen hat, ist nicht bekannt. Uns liegt aber weiterhin des koreanische Original vor. Beschrieben ist die Zusammenarbeit mit der Umsetzung eines... [mehr]

In einer in der Nacht veröffentlichten, inzwischen aber wieder gelöschten Pressemitteilung, verkünden die Halbleitersparte von Samsung und AMD eine zukünftige Zusammenarbeit. Konkret sollen Hochleistungsplatinen für Hyperscale-Rechenzentren gefertigt werden. Warum Samsung die Pressemitteilung zurückgezogen hat, ist nicht bekannt. Uns liegt aber weiterhin des koreanische Original vor. Beschrieben ist die Zusammenarbeit mit der Umsetzung eines... [mehr] -

Intel 10A, Wafer- und Packaging-Kapazitäten: Der Umbau ist größer als er zunächst scheint

Die IFS-Direct-Connect-Konferenz war für Intel eine wichtige Veranstaltung. Natürlich haben wir uns zunächst einmal auf die direkten Implikationen für die Produkte konzentriert. Aktuell liefert Intel seine Prozessoren mit einer Fertigung in Intel 4 aus, was erst der zweite Schritt in der langfristig angelegten "Fünf Nodes in vier Jahren"-Strategie ist. Wir haben Intel 3, Intel 20A und Intel 18A also erst noch vor uns. Bis wir die ersten... [mehr]

Die IFS-Direct-Connect-Konferenz war für Intel eine wichtige Veranstaltung. Natürlich haben wir uns zunächst einmal auf die direkten Implikationen für die Produkte konzentriert. Aktuell liefert Intel seine Prozessoren mit einer Fertigung in Intel 4 aus, was erst der zweite Schritt in der langfristig angelegten "Fünf Nodes in vier Jahren"-Strategie ist. Wir haben Intel 3, Intel 20A und Intel 18A also erst noch vor uns. Bis wir die ersten... [mehr] -

US-Fertigung und US-Packaging: Apple und Amkor arbeiten zusammen

Erst gestern hatten wir zum Thema, dass eine vollständige Unabhängigkeit in der Fertigung und dem Packaging laut NVIDIAs CEO Jensen Huang bis zu zwei Jahrzehnte dauern wird. Dabei bezieht sich NVIDIA aber auch auf sämtliche Komponenten und ein DGX-Server enthält mehrere zehntausend Bauelemente. Apple ist sicherlich einer der größten Fabless-Chiphersteller, der bisher alle seine Chips bei TSMC fertigen lässt. Daran soll sich auch zukünftig... [mehr]

Erst gestern hatten wir zum Thema, dass eine vollständige Unabhängigkeit in der Fertigung und dem Packaging laut NVIDIAs CEO Jensen Huang bis zu zwei Jahrzehnte dauern wird. Dabei bezieht sich NVIDIA aber auch auf sämtliche Komponenten und ein DGX-Server enthält mehrere zehntausend Bauelemente. Apple ist sicherlich einer der größten Fabless-Chiphersteller, der bisher alle seine Chips bei TSMC fertigen lässt. Daran soll sich auch zukünftig... [mehr] -

W2W 3D IC: UMC will ein Stück des Packaging-Kuchens

Der taiwanesische Halbleiterhersteller United Microelectronics Corporation (UMC) kündigt für das kommende Jahr ein neues Packaging-Verfahren an, mit dem man ein Stück des aktuellen Bedarfs nach Packaging-Kapazitäten abhaben möchte. Bei W2W 3D IC handelt es sich um ein Wafer-auf-Wafer-Verfahren, bei dem mehrere Chips übereinander gestapelt werden können. Partner sind Winbond, Faraday, ASE und Cadence. Zielmarkt für UMC dürften... [mehr]

Der taiwanesische Halbleiterhersteller United Microelectronics Corporation (UMC) kündigt für das kommende Jahr ein neues Packaging-Verfahren an, mit dem man ein Stück des aktuellen Bedarfs nach Packaging-Kapazitäten abhaben möchte. Bei W2W 3D IC handelt es sich um ein Wafer-auf-Wafer-Verfahren, bei dem mehrere Chips übereinander gestapelt werden können. Partner sind Winbond, Faraday, ASE und Cadence. Zielmarkt für UMC dürften... [mehr] -

2023 OIP-Forum: TSMC rührt die Werbetrommel für 3D-Chip Hard- und Software

Neben NVIDIA, mit den Verkäufen der entsprechenden AI-Hardware, ist auch TSMC einer der großen Profiteure des aktuellen AI-Hypes, denn hier werden die größten und aufwendigsten der aktuellen Chips gefertigt. Entsprechend hat man auch große Pläne und baut die Kapazitäten weiter aus. Aber TSMC ist nicht der einzige Hersteller, der groß in seine Packaging-Werke investiert, auch bei Intel laufen die Baumaschinen in Malaysia (Werk... [mehr]

Neben NVIDIA, mit den Verkäufen der entsprechenden AI-Hardware, ist auch TSMC einer der großen Profiteure des aktuellen AI-Hypes, denn hier werden die größten und aufwendigsten der aktuellen Chips gefertigt. Entsprechend hat man auch große Pläne und baut die Kapazitäten weiter aus. Aber TSMC ist nicht der einzige Hersteller, der groß in seine Packaging-Werke investiert, auch bei Intel laufen die Baumaschinen in Malaysia (Werk... [mehr] -

Montage- und Testeinrichtung: Intel investiert 4,6 Milliarden in Polen

Bereits mit der Ankündigung einer neuen Fabrik bei Magdeburg nannte Intel weitere Milliarden-Investitionen in einigen europäischen Ländern. Unter anderem soll eine Entwicklungsabteilungen in Polen um 50 % vergrößert werden. Hier sind bereits etwa 4.000 Mitarbeiter aktiv. Nun kündigt das Unternehmen eine weitaus größere Investition an. Bei Wrocław in Polen soll eine Einrichtung für das Packaging und Testen entstehen. Insgesamt sollen... [mehr]

Bereits mit der Ankündigung einer neuen Fabrik bei Magdeburg nannte Intel weitere Milliarden-Investitionen in einigen europäischen Ländern. Unter anderem soll eine Entwicklungsabteilungen in Polen um 50 % vergrößert werden. Hier sind bereits etwa 4.000 Mitarbeiter aktiv. Nun kündigt das Unternehmen eine weitaus größere Investition an. Bei Wrocław in Polen soll eine Einrichtung für das Packaging und Testen entstehen. Insgesamt sollen... [mehr] -

Advanced Backend Fab 6: TSMC kann mehr als 1 Million Wafer pro Jahr verarbeiten

Gestern hat TSMC die offizielle Eröffnung seiner Advanced Backend Fab 6 verkündet. Damit trifft TSMC ziemlich gut den aktuellen Bedarf nach Packaging-Kapazitäten, den vor allem NVIDIA aktuell vorantreibt. Mit den drei Ausbaustufen AP6A, AP6B und AP6C entsteht mehr als die doppelte Kapazität dessen, was aktuell in der Advanced Backend Fab 1 möglich war. Auf 143.000 m² beläuft sich die Fläche der AP6-Anlage im Zhunan Science Park,... [mehr]

Gestern hat TSMC die offizielle Eröffnung seiner Advanced Backend Fab 6 verkündet. Damit trifft TSMC ziemlich gut den aktuellen Bedarf nach Packaging-Kapazitäten, den vor allem NVIDIA aktuell vorantreibt. Mit den drei Ausbaustufen AP6A, AP6B und AP6C entsteht mehr als die doppelte Kapazität dessen, was aktuell in der Advanced Backend Fab 1 möglich war. Auf 143.000 m² beläuft sich die Fläche der AP6-Anlage im Zhunan Science Park,... [mehr] -

Intel auf dem IEDM 2022: Ausblick auf zukünftige Packaging- und Fertigunstechniken

Auf dem IEEE IEDM (International Electron Devices Meeting) wird Intel gleich mehrere Forschungspapiere vorstellen. Einige Details dazu hat man nun bereits im Vorfeld veröffentlicht, denn das eigentliche Meeting findet erst in der kommenden Woche statt. Intel befindet sich aktuell in einer großen Umstrukturierungsphase hinsichtlich seiner Fertigungstechnologien. Aktuelle Produkte werden in Intel 7 gefertigt, was eine 10-nm-Fertigung in etlichen... [mehr]

Auf dem IEEE IEDM (International Electron Devices Meeting) wird Intel gleich mehrere Forschungspapiere vorstellen. Einige Details dazu hat man nun bereits im Vorfeld veröffentlicht, denn das eigentliche Meeting findet erst in der kommenden Woche statt. Intel befindet sich aktuell in einer großen Umstrukturierungsphase hinsichtlich seiner Fertigungstechnologien. Aktuelle Produkte werden in Intel 7 gefertigt, was eine 10-nm-Fertigung in etlichen... [mehr] -

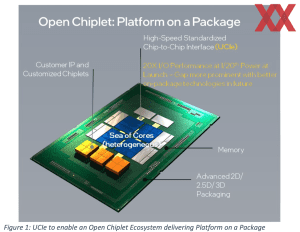

AMD, Intel, Arm und Co: UCIe soll Standard für Chiplet-Interconnects werden

Einige der großen Halbleiterhersteller haben heute angekündigt, einen neuen, offenen Standard für Chiplet-Interconnects ins Leben rufen zu wollen. Universal Chiplet Interconnect Express oder kurz UCIe tritt dabei in gewisser Weise in die Fußstapfen von PCI-Express, bzw. orientiert sich in der grundsätzlichen Herangehensweise daran. Ziel ist es gewisse Vorgaben zu entwickeln und in den beteiligten Unternehmen umsetzen zu lassen, die... [mehr]

Einige der großen Halbleiterhersteller haben heute angekündigt, einen neuen, offenen Standard für Chiplet-Interconnects ins Leben rufen zu wollen. Universal Chiplet Interconnect Express oder kurz UCIe tritt dabei in gewisser Weise in die Fußstapfen von PCI-Express, bzw. orientiert sich in der grundsätzlichen Herangehensweise daran. Ziel ist es gewisse Vorgaben zu entwickeln und in den beteiligten Unternehmen umsetzen zu lassen, die... [mehr] -

TSMC plant neue Packaging-Technologien und 1,4-nm-Fertigung

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten... [mehr]

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten... [mehr] -

Intel: Co-EMIB kombiniert EMIB und FOVEROS in riesigen Packages

Auf der SemiCon West hat Intel über neue Packaging-Technologien gesprochen. Zuletzt machte der Chipgigant mit der Nennung einiger neuer Daten zu FOVEROS auf sich aufmerksam. Co-EMIB soll die beiden bestehenden Packaging-Technologien für Intel zusammenführen. Während EMIB (Embedded Multi Die Interconnect Bridge) bereits bei den Kaby-Lake-G-Prozessoren sowie den Stratix-10-FPGAs zum Einsatz kommt, wird FOVEROS bisher nur bei den noch... [mehr]

Auf der SemiCon West hat Intel über neue Packaging-Technologien gesprochen. Zuletzt machte der Chipgigant mit der Nennung einiger neuer Daten zu FOVEROS auf sich aufmerksam. Co-EMIB soll die beiden bestehenden Packaging-Technologien für Intel zusammenführen. Während EMIB (Embedded Multi Die Interconnect Bridge) bereits bei den Kaby-Lake-G-Prozessoren sowie den Stratix-10-FPGAs zum Einsatz kommt, wird FOVEROS bisher nur bei den noch... [mehr] -

Weiteres Werk für Packaging: Intel erhöht Produktionskapazitäten von Coffee Lake

Auch Wochen nach dem offiziellen Startschuss der Coffee-Lake-Plattform von Intel kämpft das Unternehmen mit einer schlechten Verfügbarkeit seiner Core-Prozessoren aus der S-Serie. Die schlechte Verfügbarkeit soll sich allerdings bereits im Dezember 2017 verbessern, da Intel in China nun ein weiteres Werk für die Fertigstellung der Prozessoren nutzen wird. Derzeit nutzt Intel zwei Assembly/Test-Site in Malaysia zur Fertigstellung der... [mehr]

Auch Wochen nach dem offiziellen Startschuss der Coffee-Lake-Plattform von Intel kämpft das Unternehmen mit einer schlechten Verfügbarkeit seiner Core-Prozessoren aus der S-Serie. Die schlechte Verfügbarkeit soll sich allerdings bereits im Dezember 2017 verbessern, da Intel in China nun ein weiteres Werk für die Fertigstellung der Prozessoren nutzen wird. Derzeit nutzt Intel zwei Assembly/Test-Site in Malaysia zur Fertigstellung der... [mehr]