Werbung

YouTube-Leaker Moore's Law Is Dead hat in seinem neuesten Video eine Zen-Roadmap veröffentlicht, die viele Details zu den zukünftigen Architekturen Zen 5 und Zen 6 enthält. Für Zen 5 sind sogar äußerst detaillierte Informationen zur Mikroarchitekur enthalten. Die Jahresangaben zeigen allerdings auch, dass die Roadmap schon ein paar Jahre alt sein dürfte, denn hier wird Zen 5 für das aktuelle Jahr 2023 erwähnt. Auf den Markt kommen dürften die entsprechenden Prozessoren aber erst 2024. Dennoch zeigt die Roadmap die Marschrichtung, die AMD eingeschlagen hat und was uns in den kommenden beiden Generationen erwartet.

Zudem kennen wir nun sämtliche Codenamen der Zen-Architekturen und die der CCDs bis einschließlich Zen 6:

| Architektur | CCD / Core Complex | |

| Zen 2 | Valhalla | Aspen Highlands |

| Zen 3 | Cerberus | Breckenridge |

| Zen 4 | Persephone | Durango |

| Zen 5 | Nirvana | Eldora |

| Zen 6 | Morpheus | Monarch |

Nun aber zu den Details:

Grob gesprochen wird AMD mit Zen 5 die Anzahl der CPU-Kerne im CCD auf 16 erhöhen. Dies hat man auch schon bei Zen 4 getan, allerdings nur für die Zen-4c-Kerne. Möglich wäre somit das AMD auf dem Desktop nur noch einen CCD einsetzt, um auf 16 Kerne zu kommen. Die Erwähnung von "low power core option" könnte auch bedeutet, dass AMD analog wie bei Zen 4 acht normale Kerne auf ein CCD packt, aber 16 der Zen-5c-Kerne. Ob dies im Umkehrschluss bedeutet, dass wir bis zu 32 Kerne auf dem Desktop sehen, bleibt abzuwarten.

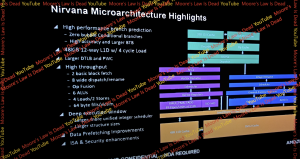

Für Zen 5 erwartet AMD ein IPC-Plus von 10 bis 15 %. Ermöglicht wird dies unter anderem durch einen auf 48 kB vergrößerten L1-Data-Cache, der bei Zen 4 noch 32 kB bemisst. Zudem sollen sechs ALUs (Arithmetic Logic Unit) zum Einsatz kommen, während es bei Zen 4 derer nur vier sind. Als Datenformat soll zudem auch FP512 verarbeitet werden können. In Zen 4 verarbeitet AMD AVX-512-Befehlssätze in dem zweimal FP256 ausgeführt werden.

Gefertigt werden sollen die Zen-5-CCDs entweder in 4 und/oder 3 nm, wenngleich diese Angaben aufgrund der zeitlichen Verschiebung der Roadmap nicht als sicher gelten können.

Für Zen 6 erwartete AMD zum Zeitpunkt an dem die Roadmap entstanden ist die Fertigung in 3 und/oder 2 nm. Das IPC-Plus soll 10 % betragen. Neue FP16-Instruktionen sollen ML/AI-Anwendungen beschleunigen.

Zudem spricht die Roadmap von einem Core Complex mit bis zu 32 Kernen, also einer weiteren Verdopplung gegenüber Zen 4c bzw. Zen 5(c). Weitere Details zur Zen-6-Architektur gibt es noch nicht.

Zum Packaging hat Moore's Law Is Dead nur wenige Informationen. Die Zen-5-Generation dürfte noch ähnlich aufgebaut sein, wie die aktuellen Ryzen- und EPYC-Prozessoren – sprich ein I/O-Die (IOD) sitzt direkt bei den CCDs und das Packaging erfolgt über eine 2.5-Technologie.

Mit Zen 6 aber soll es dann eine größere Änderung geben und die CCDs sollen auf dem IOD platziert werden. Ein dann noch hinzugefügter 3D V-Cache würde bedeuten, dass wir einen IOD sehen, auf dem der CCD sitzt und auf diesem wiederum ein kleines SRAM-Chiplet für den zusätzlichen Cache.