Werbung

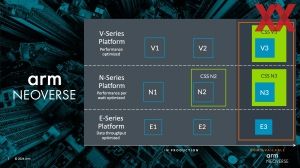

Im Sommer des vergangenen Jahres stellte ARM sein Neoverse Compute Subsystem (CSS) für die N2- und V2-Serie der Datacenter-Prozessoren vor. Das Neoverse CSS ist eine Art Referenzplattform für die Entwicklung von ARM-Prozessoren für das Datacenter, die in den vergangenen Wochen vor allem als Eigendesigns der Cloud-Anbieter auf sich aufmerksam gemacht haben.

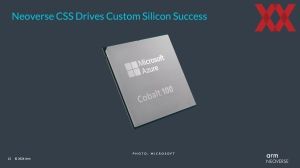

NVIDIA verwendet das V2-Design für seinen Grace-Hopper-Beschleuniger (GH100, GH200) sowie in den Bluefield DPUs, AWS verwendet in seinen Trainium-2- und Graviton-4-Prozessoren sowie den Nitro-DPUs ein ARM-Design. Zuletzt präsentierte Microsoft im November die Cobalt-100-CPU und den Maia-100-Beschleuniger, die für eigene Anwendungen sowie im Rahmen des Azure-Angebotes verwendet werden sollen.

Ob und inwieweit ARM im Datacenter weiter Marktanteile gewinnen wird, bleibt abzuwarten. Die spezifische Auslegung des Chipdesigns auf die jeweiligen Anwendungen macht für die Hyperscaler durchaus Sinn. Es gilt den Anbietern vor allem im Hinblick auf die Effizienz, weniger die Spitzenleistung.

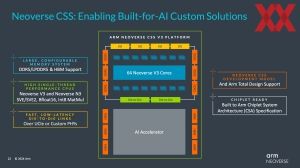

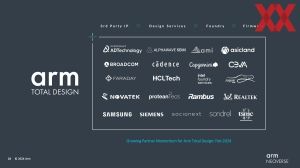

Für die nächste Generation der Nerverse-Plattform präsentiert ARM nun das Neoverse-CSS-N3- und Neoverse-CSS-V3-Design. Durch die Vorlage eines Art Referenzdesigns bietet ARM potenziellen Kunden die Möglichkeit, ihr eigenes Chipdesigns zu erstellen. Im Vergleich zu einer kompletten Eigenentwickkung von Grund auf, spart der Kunde Zeit und Geld, denn ein Tape-Out eines ersten Chips soll bereits nach neun Monaten erreicht werden können. Zudem sollen etwa 80 Ingenieursjahre eingespart werden können, was natürlich ein Kostenfaktor ist.

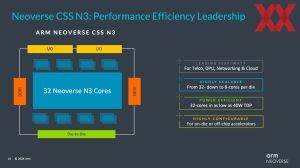

Die N-Designs sind für eine maximale Effizienz ausgelegt und waren in der Vergangenheit für bis zu 64 Kerne vorgesehen. Als CSS N3 sieht ARM im Referenzdesign 32 Kerne vor, die pro Kern um 20 % effizienter als die CSS-N2-Kerne sein sollen. Pro Chip können aber auch zwischen acht und 32 Kerne eingeplant werden. Das TDP-Ziel eines solchen Designs kann laut ARM auf 40 W festgelegt werden, wo in einer nicht näher genannten Fertigung die höchste Effizienz zu erreichen ist. Das Chiplet kann über ein Die-to-Die-Interface mit mehreren weiteren Prozessoren bzw. Chiplets zusammengebracht werden. Auch die Anbindung anderer Beschleuniger ist möglich.

Viele Details zu den Kernen und dem Aufbau der Chips macht ARM nicht. Das Blockbild zeigt zwei I/O-Optionen sowie ein Dual-Channel-DDR5-Interface für den Chiplet.

Das CMN-S3-Subsystem für die Neoverse-Plattform unterstützt theoretisch bis zu 256 Kerne pro Die und 512 Kerne pro Sockel. Aber solche Chips wird er vorerst wohl nicht geben, denn es gibt Limits in der Fertigung und der Größe eines einzelnen Chips, die hier nicht umgangen werden können. ARM erwartet CSS-N3- und CSS-V3-Designs mit maximal 96 bis 192 Kernen. Zum CSS-V3-Design kommen wir nun.

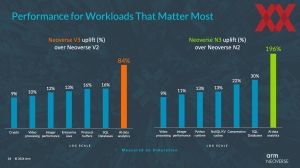

Zweites Standbein der Neoverse-CSS-Plattform sind die V-Designs und hier die neue V3-Version. Die V3-Prozessoren sollen um 50 % schneller pro Sockel sein, als ein CSS-N2-Design. Bis zu 64 Kerne sieht ARM in seiner Referenzimplementierung vor, möglich sind aber bis zu 128 Kerne. Hinsichtlich der I/O-Funktionalität nennt ARM PCI-Express 5.0 und CXL 3.0. Das Speicherinterface unterstützt DDR5, LPDDR5 und HBM3.

Gleich zwei Die-to-Die-Interfaces können verwendet werden um einen externen Beschleuniger als Chiplet anzubinden. Das Beispiel der Grace-Hopper-Beschleuniger von NVIDIA liegt hier am nächsten an dem, was sich ARM an dieser Stelle vorstellt. Das Interface unterstützt auch Universal Chiplet Interconnect Express oder kurz UCIe.

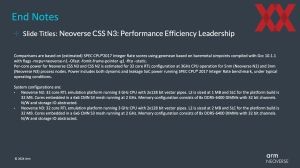

Sowohl beim CSS-N3- wie auch CSS-V3-Design handelt es sich um ein Armv9-Design mit AArch64-Instruction-Sets und Scalable Vector Extensions (SVE2). Genauere Details macht ARM an dieser Stelle aber noch nicht. Für die Benchmarks nennt ARM im Kleingedruckten für die Vergleichsbenchmarks bis zu acht DDR5-Speicherkanäle in denen Speicher mit bis zu 7.200 MT/s sitzt.

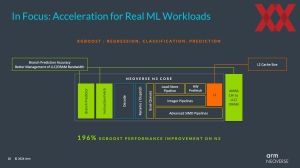

Mehr AI-Leistung durch mehr Cache und schnelle Speicher

Natürlich will ARM noch einmal auf Mitnahmeeffekte des aktuellen AI-Trends hinweisen. Alle anfangs vorgestellten Custom-Designs der Kunden sind genau darauf aufgelegt – sei es für das Training oder das Inferencing.

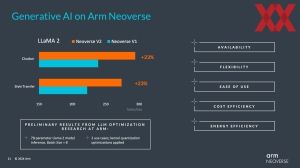

Über eine verbesserte Sprungvorhersage sowie einen größeren L2-Cache (nun 2 MB pro Kern beim N3-Design, im V3-Design sollen es 3 MB sein) will ARM die AI-Leistung der N3- und V3-Designs um 196 % bzw. 84 % verbessert haben. Ein Llama-2-Modell mit sieben Milliarden Parametern wurden durch Soft- und Hardwareoptimierungen im Vergleich zwischen Neoverse V1 und V2 bereits um 23 % schneller (+23 % mehr Token konnten pro Sekunde bearbeitet werden).

Hinsichtlich der Gewichtung der Rechenaufgaben in diesem Segment sind ARM das LLM-Inferencing bei 80 %, die weiteren 20 % fallen auf das Training und entsprechend findet auch eine Gewichtung der Hardware statt.

Neben der Optimierung in der Mikroarchitekturen sollen vor allem die CSS-V3-Designs durch die Anbindung eines schnelles DDR5/LPDDR5 bzw. HBM3 profitieren.

Neben der AI-Leistung sollen die CSS-N3- und CSS-V3-Prozessoren aber natürlich auch in den weiteren Anwendungsbereichen der Konkurrenz aus dem Hause AMD und Intel überlegen sein. Für Datenbanken, Java oder XGBoost nennt ARM teilweise deutliche Vorteile gegenüber der genannten Konkurrenz.

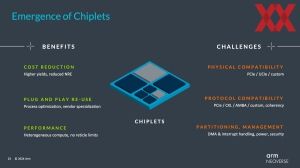

Chiplet System Architecture (CSA)

ARM treibt die Chiplet System Architecture (CSA) voran. Wie bereits für die CSS-N2- und CSS-V2-Designs sind diese als Chiplets so ausgelegt, dass sie theoretisch beliebig mit anderen Komponenten kombiniert werden können. ARM stellt an dieser Stelle sicher, dass ein CSS-N3- und CSS-V3-Design über seine physikalische Umsetzung und die Protokolle zu anderen Chiplets kompatibel ist. UCIe ist hier das Stichwort. Bisher kommt diese Kombination aus ARM-Kernen und eines externen Beschleunigers aber nur bei NVIDIAs GH100/GH200 zum Einsatz.

Wir sind daher gepannt, ob es mit den ersten CSS-N3- und CSS-V3-Designs auch eine Weiterentwicklung in dieser Hinsicht gibt und mehr Hersteller den eigenen Chiplet-Ansatz über die ARM-Kerne hinaus verwenden.

Roadmap zur Neoverse-Plattform

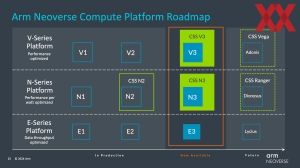

Zudem präsentierte ARM die Roadmap für die zukünftigen Neoverse-Produkte.

Auf CSS V2 (Demeter) und CSS N2 (Perseus) folgen aktuell CSS V3 (Poseidon) und VSS N3. Als nächste Generation vorgesehen sind Adonis für ein potentielles V4- und Dionysus für ein potentielles N4-Design. Die griechische Götterwelt wird weiter abgearbeitet.