Werbung

Die Wafer Scale Engine geht in die dritte Generation. Cerebras wechselt für seinen Chip in Wafer-Größe auf eine Fertigung in 5 nm – will die Leistungsaufnahme und den Preis identisch belassen, aber einen großen Sprung bei der AI-Rechenleistung machen.

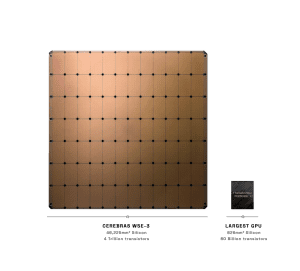

Im Sommer 2019 sorgte der gigantische AI-Chip mit 46.225 mm² für Aufmerksamkeit, da er neben der Fertigung in der Anwendung völlig neue Konzepte anführte. 2021 wurde der Nachfolger vorgestellt. Die Besonderheit ist sicherlich darin zu suchen, dass Cerebras die einzelnen Chips auf dem Wafer nicht separiert, sondern die 84 Chips auf dem Wafer zusammen belässt und direkt miteinander verbindet.

Auch wenn Cerebras also von einem Chip mit einer Größe von 46.225 mm² spricht, so muss man doch die einzelnen Chips sehen und kann nicht einfach einen Vergleich zur aktuell größten GPU ziehen. Dennoch ist dieser Vergleich zumindest in Teilen sicherlich sinnvoll. Die GH100-GPU von NVIDIA kommt auf 80 Millionen Transistoren und eine Fläche von 814 mm².

Gefertigt wird die WSE-3 in 5 nm vermutlich bei TSMC. Die Einzelbetrachtung der Chips kommt dann wieder ins Spiel, wenn von 84 unabhängigen Taktdomainen auf der WSE-3 die Rede ist.

Die eigentlichen AI-Kerne (Sparse Linear Algebra Compute Cores) SLAC haben in der dritten Generation der Mikroarchitektur ebenfalls einige Änderungen erhalten. So hat jeder der CS-3-Kerne nun eine 8-Wide FP16-SIMD-Einheit – eine Verdopplung gegenüber den CS-2-Kernen. Auf weitere Details geht Cerebras aber nicht ein.

| WSE-1 | WSE-2 | WSE-3 | |

| Fertigung | 16 nm | 7 nm | 5 nm |

| Chipgröße | 46.225 mm² | 46.225 mm² | 46.225 mm² |

| Anzahl der Transistoren | 1,2 Billionen | 2,6 Billionen | 4 Billionen |

| AI-Kerne | 400.000 | 850.000 | 900.000 |

| SRAM | 18 GB | 40 GB | 44 GB |

| Speicherbandbreite | 9 PB/s | 20 PB/s | 21 PB/s |

| Fabric-Bandbreite | 100 PB/s | 220 PB/s | 214 PB/s |

Neben der Fertigung in 5 nm sehen die Änderungen in der WSE-3 gar nicht so groß aus. Aus 850.000 werden 900.000 AI-Kerne. Der SRAM, der über die komplette Fläche verteilt ist, wächst von 40 auf gerade einmal 44 GB an. Die Speicherbandbreite sowie die interne Fabric-Bandbreite machen ebenfalls keinen großen Sprung.

Dennoch aber wächst die Anzahl der Transistoren von 2,6 Billionen auf 4 Billionen. Es muss also größere Änderungen an der Mikroarchitektur gegeben haben, als dies über die Anzahl der AI-Kerne oder den SRAM zu vermuten ist.

Auf den Aufbau eines Servers mit WSE sind wir bereits genauer eingegangen. Hier dürfte es auch nur wenig Änderungen geben. Es wird an dieser Stelle aber deutlich, welche technische Infrastruktur notwendig ist, damit ein solcher "Chip" überhaupt arbeiten kann. Das der SRAM nicht viel größer geworden ist, hängt wohl auch damit zusammen, dass der externe Speicher nun in Kapazitäten von 1,5 TB, 12 TB und 1,2 PB ausgeführt werden kann. Zusammen mit der entsprechenden Speicherbandbreite ist dieser ausreichend schnell angebunden, damit die Parameter der Large Lange Models (LLMs) schnell zu den AI-Kernen übertragen werden können.

Laut Cerebras kann eine WSE-3 ein Modell mit 24 Billionen Parametern trainieren. Aktuelle LLMs kommen zum Beispiel als Llama2-70B auf 70 Milliarden Parameter.

Zusammen mit einigen Partnern kündigt Cerebras den Aufbau von KI-Supercomputern mit WSE-3 an. Der Condor Galaxy 3 ist ein solcher und soll im zweiten Quartal 2024 an den Start gehen. 64 CS-3-Systeme werden im Condor Galaxy 3 zusammenarbeiten. Theoretisch können Cluster mit bis zu 2.048 CS-3 aufgebaut werden.