Werbung

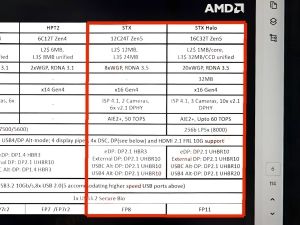

Offensichtlich sind die chinesischen Kollegen von HKEPC an ein 114-seitiges Dokument oder Ausschnitte daraus gelangt, welche technische Details zu den zukünftigen APUs Strix Point und Strix Halo enthalten. Demnach wird Strix Point auf zwölf Zen-5-Kerne setzen. Jedem Kern stehen 1 MB an L2-Cache (insgesamt 12 MB) zur Verfügung, der L3-Cache wird mit 24 MB genannt. Damit setzt Strix Point weiterhin auf die Hälfte an L3-Cache im Vergleich zu den Desktop-Prozessoren – so wie dies aktuell der Fall ist.

Die integrierte Grafikeinheit von Strix Point besitzt acht WGP (Workinggroup-Agents) und somit 16 Compute Units. Als Architektur wird RDNA 3.5 genannt. Der integrierte AI-Beschleuniger auf Basis der XDNA-2-Architektur kommt auf eine Rechenleistung von 50 TOPS, was in etwa der dreifachen Leistung dessen entspricht, was die NPU der aktuellen Generation zu leisten im Stande ist.

Die TDP-Spanne von Strix Point soll von 45 bis 65 W reichen. Als Arbeitsspeicher kann LPDDR5X-7500 zum Einsatz kommen.

Strix Halo ist die große APU, die immer wieder in den Gerüchten vorkommt. Hier sollen gleich 16 Zen-5-Kerne zum Einsatz kommen. Der L2-Cache fällt entsprechend mit 16 MB etwas größer aus. Dies gilt auch für den L3-Cache, der auf 32 MB anwächst, was pro Kern aber noch immer die Hälfte dessen ist, das die großen Desktop-Prozessoren spendiert bekommen.

Die integrierte Grafikeinheit setzt ebenfalls auf die RDNA-3.5-Architektur. Mit 20 WGPGs sprechen wir hier von 40 CUs und damit einer sehr starken GPU, wie wir sie bisher nur von den Custom-Chips für die Konsolen kennen. Vermutlich auch wegen der starken GPU kommt ein Last Level Cache (bei AMD MALL getauft) zum Einsatz, der 32 MB groß ist. Der MALL-Cache ist namentlich bereits mehrfach aufgetaucht. Bei der aktuellen GPU-Generation nennt AMD ihn Infinity Cache.

Die NPU in Strix Halo soll mit 60 TOPS noch einmal 20 % schneller als bei Strix Point sein. Darüber hinaus unterstützt die große APU LPDDR5X-8000, der über ein 256 Bit breites Speicherinterface angebunden ist. Laut Angaben von HKEPC nennt das Dokument eine Standard-TDP von 70 W für Strix Halo. Es sollen bis zu 130 W möglich sein.

Beide Prozessoren bieten 16 PCI-Express-4.0-Lanes, zahlreiche USB-Anschlüsse und unterstützen eine Display-Ausgabe per DisplayPort 2.1 UHBR10/20. Als Kontakt-Sockel zum Mainboard setzen Strix Point auf FP8 und Strix Halo auf FP11.

Zur Computex wird erwartet, dass AMD weitere Details zu seinen Zen-5-Prozessoren vorstellen wird. Ob man nur einen Ausblick gibt oder einzelne Produktserien bereits vollständig vorgestellt werden, ist nicht bekannt.