Werbung

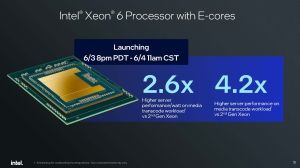

Seit Jahren in der Vorbereitung stellt Intel heute die ersten Xeon-6-Prozessoren final vor. Diese bestehen aus den auf Effizienz getrimmten Efficiency-Kern-Modellen namens Sierra Forest sowie, später 2024, auch aus solchen, die ausschließlich mit Performance-Kernen bestückten sind und unter Granite Rapids geführt werden. Die Namensänderung weg von Xeon Scalable hin zu Xeon 6 hatte Intel bereits vor einigen Wochen angekündigt.

Um es uns und unseren Lesern etwas einfacher zu machen, werden wir die Prozessoren auf Basis von Sierra Forest ab jetzt Xeon 6E nennen, während wir die Modelle auf Basis von Granite Rapids nun Xeon 6P nennen werden. Offiziell nutzt Intel diese Namensgebung nicht, die Buchstaben "E" und "P" kommen aber in den Modellnamen vor.

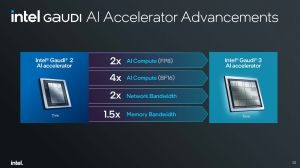

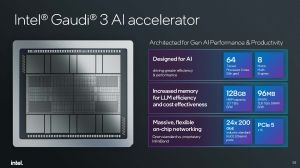

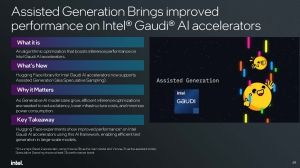

Die Xeon-6P-Prozessoren werden weiterhin den traditionellen Servermarkt bedienen. Hier kommt es auf eine möglichst hohe Leistung pro Kern an. Die Xeon-6E-Prozessoren hingegen adressieren die Nutzer bzw. Datacenter-Betreiber, der auch einen Blick auf das Leistung/Watt-Verhältnis hat. Xeon 6E startet offiziell zum heutigen Tag, was aber auch nicht für alle Modelle gilt, wie wir später noch sehen werden. Xeon 6P wird ab dem dritten Quartal an den Start gehen – gleichzeitig mit Gaudi 3.

Die Xeon-6-Serie wird aus den SP-Modellen auf Basis des Sockel LGA4710 und den AP-Modellen auf Basis des Sockel LGA7529 bestehen - allesamt auf der Birch-Stream-Plattform

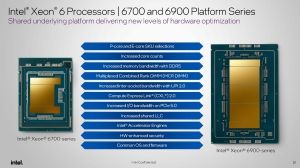

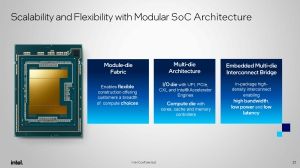

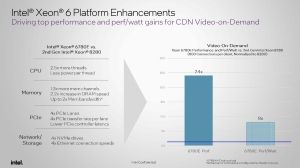

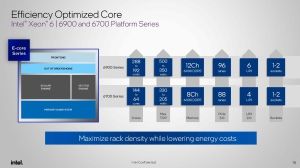

Sozusagen der ersten Staffelläufer für die Xeon-6-Serie sind die Xeon-6700E-Prozessoren. Diese bestehen aus einem einzelnen Compute-Tile mit den E-Kernen und bieten bis zu 144 dieser Kerne. Zwei I/O-Tiles flankieren den Compute-Tile und stellen die I/O-Funktionen wie PCI-Express-Lanes, den Sockel-Interconnect UPI, den I/O-Fabric und die Beschleuniger zur Verfügung. Die Speichercontroller setzen weiterhin in den Compute-Tiles. Die Xeon-6700E-Prozessoren werden acht Speicherkanäle für DDR5-6400 sowie 88 bzw. 136 PCI-Express-Lanes zu bieten haben. Die Anzahl der Lanes ist davon abhängig, ob der Prozessor in seinem 1S- oder einem 2S-, 4S- oder gar 8S-System zum Einsatz kommt. Alle Xeon-6-Prozessoren unterstützen PCI-Express 5.0.

Es wird auch eine Xeon-6700P-Serie geben, die dann bis zu 86 Performance-Kerne anzubieten hat. Server mit vier (4S) oder gar acht (8S) Prozessoren werden der Xeon-6700P-Serie vorbehalten bleiben. Die 6700E-Prozessoren sind auf zwei Sockel beschränkt. Die Xeon-6P-Modelle werden zudem MCR mit bis zu 8.000 MT/s unterstützen. Die TDP der Xeon-6700E- und Xeon-6700P-Serie reicht bis zu 350 W.

Ab dem dritten Quartal will Intel dann die Xeon-6900P-Serie einführen. Diese wird bis zu 128 Performance-Kerne im Angebot haben. Als zweite Plattform innerhalb der Serie unterstützt diese 12 Speicherkanäle für DDR5-6400 oder MCR mit bis zu 8.800 MT/s. Zudem stehen bis zu 96 PCI-Express-Lanes zur Verfügung und die Prozessoren können in 1S- oder 2S-Systemen betrieben werden. Für die Xeon-6900P-Serie sprechen wir hier also von bis zu 256 Kernen pro Server. Allerdings verbrauchen diese Prozessoren auch bis zu 500 W.

Die Xeon-6900E-Serie wiederum wird erst im ersten Quartal 2025 folgen und bis zu 288 E-Kerne pro CPU zu bieten haben. Als 2S-Server sprechen wir hier also von 576 Kernen. Die 12 Speicherkanäle für DDR5 oder MCR sowie bis zu 96 PCI-Express-Lanes sind auch hier vorgesehen – aber auch die bis zu 500 W an TDP.

Schlussendlich sollen 2025 auch die weiteren Serien wie Xeon 6700P (Gegenstück zur Xeon-6700E-Serie), Xeon 6500P, Xeon 6 SoC und Xeon 6300P folgen. Bis auf die Xeon-6700P-Serie nennt Intel zu diesem Zeitpunkt aber noch keine weiteren Details.

Theoretisch ist es innerhalb der Plattform möglich, zwischen den E- und P-Kern-Prozessoren zu wechseln – zumindest so lange man sich zwischen der 6700- und der 6900-Serie bewegt. Allerdings startet Intel derart gestaffelt, dass eine Entscheidung zwischen diesen Modellen auf Basis einer Server-Plattform erst verzögert bzw. ab dem ersten Quartal 2025 möglich ist.

| Xeon-6-Serie | Sockel | Kerne | TDP (Max) | Speicherkanäle | PCIe / CXL | UPI-Links | Sockel |

| Xeon 6700E | LGA7529 | 144 E-Kerne | 350 W | 8x DDR5-6400 | 88 | 4x UPI 2.0 | LGA4710 |

| Xeon 6700P | LGA7529 | 86 P-Kerne | 350 W | 8x DDR5-6400 8x MCR-8000 | 88 | 4x UPI 2.0 | LGA4710 |

| Xeon 6900E | LGA7529 | 288 E-Kerne | 500 W | 12x DDR5-6400 | 96 | 6x UPI 2.0 | LGA7529 |

| Xeon 6900P | LGA7529 | 128 P-Kerne | 500 W | 12x DDR5-6400 12x MCR-8800 | 96 | 6x UPI 2.0 | LGA7529 |

Um die Xeon-6-Prozessoren in einem Multi-Socket-System miteinander zu verbinden, kommt einmal mehr Intels Ultra Path Interconnect (UPI) zum Einsatz. Mit der 5. Generation alias Emerald Rapids beschleunigte Intel die UPI-2.0-Links von 16 auf 20 GT/s. Nun mit Xeon 6 sollen es 24 GT/s sein.

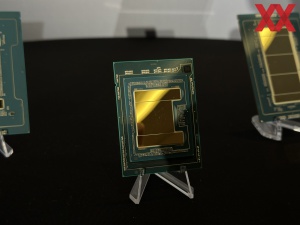

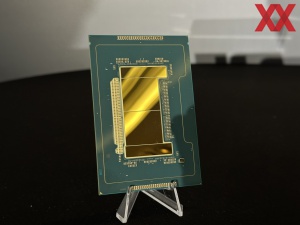

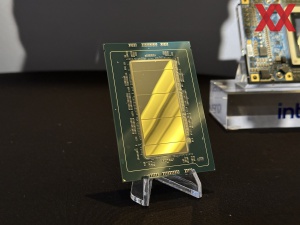

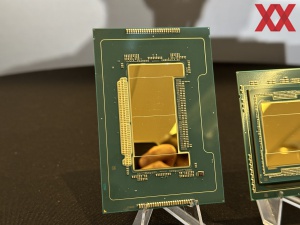

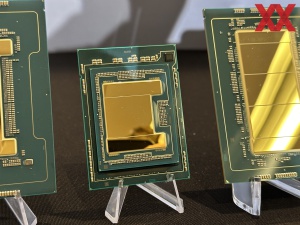

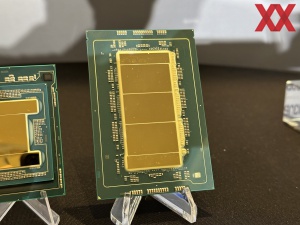

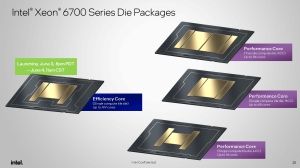

Sechs Varianten: Das Package-Design

Ausgehend von vier Dies im Package für Sapphire Rapids und dann zwei Dies für Emerald Rapids, stellen die Xeon-6-Prozessoren einen deutlichen Wechsel im Design des Package dar. Innerhalb einer Serie (Xeon 6700 und Xeon 6900) bleiben die I/O-Funktionen erhalten, was sich dadurch ausdrückt, dass hier immer wie I/O-Tiles zum Einsatz kommen. Die Anzahl der Compute-Tiles fällt je nach Serie aber unterschiedlich aus.

Für die Xeon-6700E-Serie kommt, wie bereits erwähnt, ein Compute-Tile mit den E-Kernen dazu. Für die Xeon-6700P-Serie verwendet Intel zwei Compute-Tiles mit jeweils bis zu 43 aktiven CPU-Kernen (XCC, Extreme Core Count). Die darunterliegengend Xeon-6500P- und Xeon-6300P-Serien verwenden jeweils einen Compute Tile mit 48 Kernen (HCC, High Core Count) und 16 Kernen (LCC, Low Core Count).

Xeon-6900P-Serie wird neben zwei I/O-Tiles auf drei Compute-Tiles setzen, die sich die 128 Kerne aufteilen. Wie genau dies bei 128 / 3 umgesetzt wird, hat Intel noch nicht verraten. Auch wenn Intel diese Compute-Tiles als UCC (Ultra Core Count) bezeichnet, so dürften hier dieselben Chips zum Einsatz kommen wie in der Xeon-6700P-Serie. Für die Xeon-6900E-Serie setzt Intel auf zwei Compute-Tiles mit jeweils 144 E-Kernen, sodass wir hier insgesamt auf 288 Kerne kommen. Der Einsatz von zwei Compute-Tiles mit E-Kernen und drei Compute-Tiles mit P-Kernen ist notwendig, damit Intel die 12 Speichercontroller auf der Plattform anbieten kann.

çIm Compute-Tile sind alle Kerne und Caches über ein Mesh angebunden. Der Last Level Cache (LLC) steht allen Kernen zur Verfügung, es kann aber auch eine NUMA-Clustering gewählt werden. Die Speichercontroller befinden sich wie gesagt mit in den Compute-Tiles. Intel wählt diesen Ansatz sicherlich, um die Latenzen und Bandbreite zu den Kernen möglichst gering bzw. hoch zu halten.

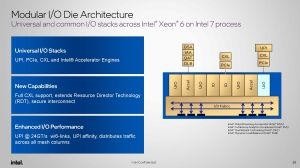

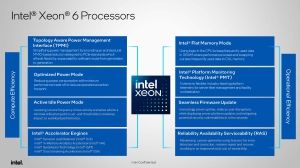

Die I/O-Tiles verfügen ihrerseits über ein I/O-Fabric, welches die verschiedenen Blöcke miteinander verbindet. Zwei dieser Blöcke sind die Accelerator Cluster, von denen jedes I/O-Tile zwei besitzt und diese beinhalten jeweils einen QAT, DLB, DSA und IAA.

An dieser Stelle wollen wir die Funktion der einzelnen Beschleuniger noch einmal erläutern:

- QAT (QuickAssist Technology): Ist nun Teil des Kerns und für Verschlüsselung und Kompression von Datenstreams vorgesehen. Network Secure Gateways und Content Delivery Networks sind zwei der denkbaren Anwendungen für QAT.

- DLB (Dynamic Load Balancer): Der DLB sorgt für ein besseres Load Balancing und eine bessere Auslastung der Kerne auch für wenig anspruchsvolle Workloads. Als eine QoS können bestimmte Pakete in der Pipeline auch priorisiert werden.

- DSA (Data Streaming Accelerator): Speicherzugriffe laufen nicht mehr über die Kerne, sondern teilweise ausgelagert werden. Dies kann für eine Datenanalyse und Distributive-Storage-Dienste sinnvoll sein.

- IAA (In-Memory Advanced Analytics Accelerator): Daten werden aus dem Speicher gelesen und in diesen geschrieben, die Dekompression und Kompression erfolgen im IAA und werden von dort in den LLC übertragen. In-Memory Datenbanken, Datenanalyse oder Datenbanken allgemein sind Anwendungsfelder von den IAA.

Einige der weiteren I/O-Blöcke können frei konfiguriert werden. So können die Standard-I/O-Blöcke als PCI-Express- oder CXL-Lanes verwendet werden. Die UIP-Blöcke können zudem auch für ein UPI verwendet werden. Für 1S- und 2S-CPUs verzichtet Intel teilweise darauf und kann daher mehr PCI-Express- und CXL-Lanes anbieten.

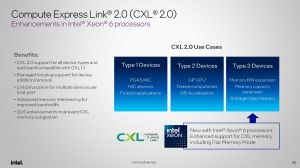

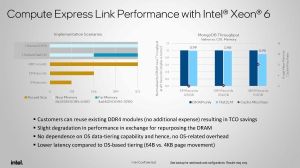

CXL 2.0 Type 3

Die Xeon-6-Prozessoren werden erstmals auch Type 3 für CXL 2.0 unterstützen. Für Type 3 geht es maßgeblich darum die Möglichkeiten der Speichererweiterung zu erweitern.

In CXL 2.0 Type 3 kann ein NUMA-Clustering des Speichers stattfinden. Dies beinhaltet auch die Kenntnis dieser Aufteilung gegenüber dem Hypervisor. Die Xeon-6P-Prozessoren unterstützen zudem ein CXL Hetero Interleaving. Hier wird der CXL-Speicher in der Speichererweiterung zum DRAM-Adressraum hinzugenommen. Die Erweiterung der Kapazität geht auch mit einer höheren Speicherbandbreite einher, denn zu den acht bzw. zwölf Speicherkanälen kommen durch das CXL Hetero Interleaving vier weitere hinzu.

Zudem gibt es nun noch einen Flat Memory Mode, in dem der Prozessor in eigener Hardware festlegt, welche Daten sich im DRAM oder in der CXL-Speichererweiterung befinden sollen. Dies ist natürlich abhängig davon, wie groß der DRAM selbst ist und ob der ständig benötigte Datensatz komplett in den DRAM passt oder nicht.

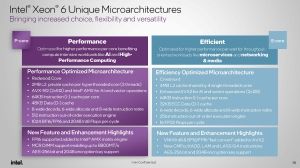

Zwei altbekannte, aber unterschiedliche Mikroarchitekturen

Für die Xeon-6-Prozessoren kommen zwei Mikroarchitekturen zum Einsatz, die wir grundsätzlich bereits kennen. Xeon 6E setzt auf die Crestmont-Architektur. Im Vergleich zur Vorgänger-Architektur Gracemont soll es für die Crestmont-Kerne eine Steigerung in der IPC-Leistung von 4 % geben – bisher kamen Gracemont und Crestmont nur bei den Endkunden-Prozessoren zum Einsatz, einen Vorgänger zu Sierra Forest gibt es nicht. Jedem Kern stehen 32 kB Data- und 64 kB Instruction-L1-Cache zur Verfügung. Es bleibt in der Anordnung bei 4 MB an L2-Cache über vier E-Kerne hinweg.

Anders sieht es bei den Xeon-6P-Modellen bzw. der dazugehörigen Redwood-Cove-Architektur aus. Diese kommt bisher nur bei den Meteor-Lake-Prozessoren zum Einsatz. Auf dem Desktop und auch für die 5. Xeon-Generation alias Emerald Rapids setzt Intel aktuell noch auf Raptor Cove.

Markant ist vor allem die Vergrößerung des L2-Caches von 1,875 auf 2 MB für jeden Kern. Zum Start von Meteor Lake ließ Intel verlauten, dass die IPC-Leistung im Vergleich zu Golden Cove fast identisch sein soll. Zu Redwood Cove gegenüber Raptor Cove als direkten Vorgänger der Xeon-Mikroarchitektur haben wir keinerlei Angaben. Ein großes IPC-Leistungsplus ist hier aber nicht zu erwarten.

Mit seinen Xeon-Prozessoren mit E- und P-Kernen fährt Intel eine grundsätzlich andere Strategie als AMD. Hier gibt es die EPYC-Prozessoren mit Zen-4c-Kernen, die zu den Zen-4-Kernen ISA-kompatibel sind und damit den gleichen Funktionsumfang abbilden können. Bei den Xeon-6-Prozessoren sieht dies anders aus. Die Basis-ISA für x86 beherrschen sowohl die E- wie auch P-Kerne. Auch AVX2 wird von beiden unterstützt. AVX-512 und auch die Advanced Matrix Extensions (AMX) unterstützen aber nur die P-Kern-Modelle. Software, die von AVX-512 oder AMX Gebrauch macht, läuft damit auf den E-Kern-Xeons bei weitem nicht so schnell, wie dies auf den P-Kern-Modellen der Fall ist. Weitere Komponenten im Software Stack wie die Betriebssysteme, Hypervisor oder bestimmte Programmbibliotheken können auf beiden Xeon-Varianten ausgeführt werden.

| Modell | Kerne | Basis-/Boost-Takt | L3-Cache | TDP | DDR5 | PCIe/CXL-Lanes |

| Xeon 6780E | 144 | 2,2 / 3,0 GHz | 108 MB | 330 W | 6.400 MT/s | 88 |

| Xeon 6766E | 144 | 1,9 / 2,7 GHz | 108 MB | 250 W | 6.400 MT/s | 88 |

| Xeon 6756E | 128 | 1,8 / 2,6 GHz | 96 MB | 225 W | 6.400 MT/s | 88 |

| Xeon 6746E | 112 | 2,0 / 2,7 GHz | 96 MB | 250 W | 5.600 MT/s | 88 |

| Xeon 6740E | 96 | 2,4 / 3,2 GHz | 96 MB | 250 W | 6.400 MT/s | 88 |

| Xeon 6731E | 96 | 2,2 / 3,1 GHz | 96 MB | 250 W | 5.600 MT/s | 88 |

| Xeon 6710E | 64 | 2,4 / 3,2 GHz | 96 MB | 205 W | 5.600 MT/s | 88 |

Der angegebene Boost-Takt deckt sich für alle Modelle mit dem All-Core-Boost, wenn alle Kerne unter Last sind. Alle oben genannten Modelle sind für 2S-Systeme vorgesehen. Eine Ausnahme bildet der Xeon 6731E, der keinerlei UPI-Links anzubieten hat, aber auch nicht mehr PCI-Express- und CXL-Lanes zu bieten hat. Alle Modelle bieten zudem jeweils zwei Beschleuniger (DSA, IAA, QAT und DLB), der Xeon 6740E und 6710E bilden eine Ausnahme, denn hier sind standardmäßig vier QAT und DLB aktiv. Bei den anderen Modellen können aber auch mehr Beschleuniger über den On-Demand-Dienst bei den OEMs oder SIs aktiviert werden.

Preise nennt Intel zu den Prozessoren der Xeon-6700E-Serie nicht. Dies ist ungewöhnlich, denn bisher sind wurden immer empfohlene Abnahmepreise genannt.

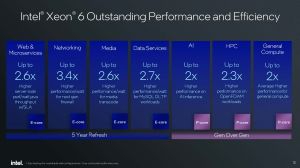

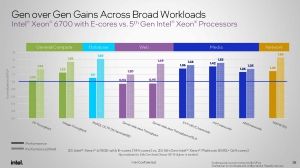

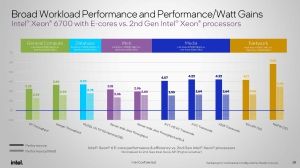

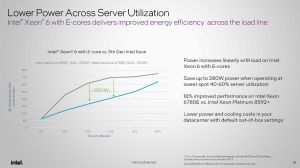

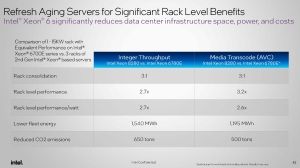

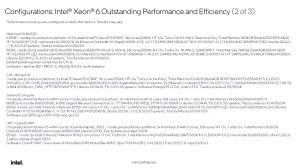

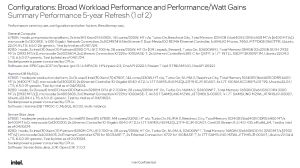

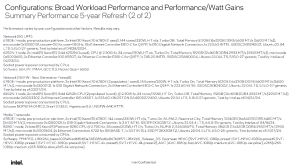

Benchmarks: Xeon 6E gegen EPYC mit Zen 4c

In den von Intel veröffentlichten Benchmarks vergleichen zwei Xeon 6780E mit jeweils 144 Kernen und einer TDP von 330 W gegen zwei Xeon Platinum 8592+ mit jeweils 64 Kernen und 350 W. Der Fokus dieser Vergleichs liegt sicherlich auf dem Leistung/Watt-Verhältnis und natürlich stehen die Xeon-6E-Kerne hier deutlich besser dar. Unternehmen, die bisher beispielsweise einen Xeon-Prozessor der zweiten Generation eingesetzt haben, sehen neben einem besserem Leistung/Watt-Verhältnis aber auch einen ebenso deutlichen Leistungssprung – trotz der E-Kerne.

Der interessante Vergleich ist aber sicherlich der Xeon 6756E mit 128 Kernen ohne Hyperthreading gegen einen EPYC 9534 mit 64 Kernen aber eben aktiviertem Hyperthreading. Je nach Anwendung sind die AMD-Prozessoren hier schneller, im Leistung/Watt-Verhältnis sieht sich Intel aber nun weit vor seinem Konkurrenten.

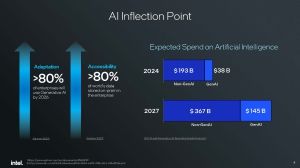

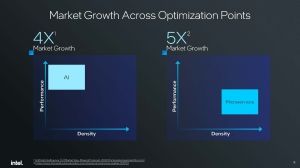

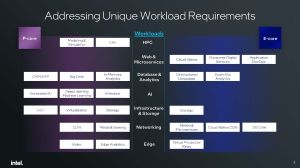

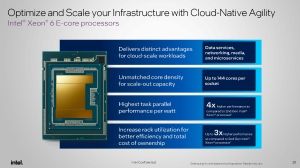

Xeon 6E: Es dreht sich alles um die Effizienz

Es soll zukünftig eine klare Aufteilung der Workloads geben – "one size fits it all" gibt es bei den Xeon-Prozessoren nicht mehr. Die E-Kern-Xeons sind für "Cloud Native"- und Datenbank-Anwendungen vorgesehen. Auch Infrastruktur wie Storage- und Netzwerk-Anwendungen sollen von den sparsamen Xeon-6E-Prozessoren profitieren.

Die Xeon-6P-Prozessoren sollen weiterhin den Bereich der HPC- und AI-Anwendungen abdecken können – deutlich besser als dies mit Xeon 6E möglich wäre. Aber natürlich gibt es hier auch eine gewisse Schnittmenge zwischen den Xeon-6E- und Xeon-6P-Prozessoren, wo es dann auf die genaue Anwendung ankommt und so beide Modelle die richtigen sein können. Entsprechend stellte Intel an dieser Stelle heraus, dass man eine gemeinsame Plattform hat und sich der Kunde somit entscheiden kann, welche der beiden Xeons er einsetzen möchte.