Werbung

Bisher haben wir von Qualcomm im Zusammenhang mit dem Snapdragon X Elite und dem Snapdragon X Plus vor allem eines gehört: Große Versprechungen. Die zahlreichen Vorstellungen der Notebook-Hersteller auf der Computex legen aber zunächst einmal nahe, dass zumindest von Seiten der Hersteller großes Interesse an einem ARM-SoC gehegt wird. Ob die Erwartungen am Ende erfüllt werden können, steht auf einem anderen Blatt, denn bisher kennen wir nur die Benchmarks von Qualcomm und solche, die von Qualcomm unter bestimmten Bedingungen ermöglicht wurden. Von unabhängigen Tests kann noch keine Rede sein.

Es ist daher recht schwierig, sich ein gutes Bild dessen zu machen, was bereits in wenigen Tagen in den Handel kommen soll. Von der Computex gab es weitere Benchmarks, die zumindest einen unabhängigeren Charakter haben, die sich allerdings nur schwer vergleichen lassen.

Neben den groben technischen Daten der einzelnen Modelle des Snapdragon X Elite und Plus kennen wir bereits einige Details zur NPU.

| Kerne | Multi-Threaded-Takt | Dual-Core-Takt | Cache | GPU-FLOPs | NPU-TOPs | Speicher | |

| Snapdragon X Elite (X1E-84-100) | 12 | 3,8 GHz | 4,2 GHz | 42 MB | 4,6 | 45 | LPDDR5X-8448 |

| Snapdragon X Elite (X1E-80-100) | 12 | 3,4 GHz | 4,0 GHz | 42 MB | 3,8 | 45 | LPDDR5X-8448 |

| Snapdragon X Elite (X1E-78-100) | 12 | 3,4 GHz | - | 42 MB | 3,8 | 45 | LPDDR5X-8448 |

| Snapdragon X Plus (X1P-64-100) | 10 | 3,4 GHz | - | 42 MB | 3,8 | 45 | LPDDR5X-8448 |

Heute nun können wir über die CPU- und GPU-Architektur sprechen, denn bisher hielt sich Qualcomm noch extrem zurück, was das Oryon-Design so besonders macht.

Etwa 200 Mitarbeiter arbeiteten zuletzt bei Nuvia an einem ARM-Prozessor für Server und entwickelten eine eigene Architektur auf Basis der ARM-ISA. Die Ambitionen waren groß. Der Phoenix getaufte CPU-Kern sollte doppelt so schnell wie damalige CPU-Kerne und dabei deutlich sparsamer agieren. Dann aber kaufte Qualcomm das CPU-Startup und widmete die Entwicklung von einem Server- in ein Client-Design um.

Heute nun können wir die ersten Details zur Architektur veröffentlichen. Der Oryon-Prozessor basiert auf einem ARMv8.7-Design. Der neueste M4-Chip von Apple hingegen basiert schon auf ARMv9. Ein ARMv9-Design muss die Erweiterungen für Memory Tagging (MTE), Transactional Memory (TME) und die Scalable-Vector-2-Erweiterungen (SVE2) enthalten. Zudem muss die Kompatibilität zu NEON gegeben sein. Dies ist mit einem ARMv8.7-Design noch nicht der Fall.

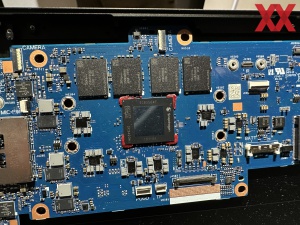

Für den Snapdragon X Elite und Plus verwendet Qualcomm drei Quad-Core-Cluster und kommt so auf maximal zwölf CPU-Kerne. Für die Plus-Variante mit zehn Kernen sind dann zwei Kerne nicht aktiv. Auch eine Achtkern-Variante (siehe erstes Bild) konnten wir bereits entdecken, diese wurde von Qualcomm aber noch nicht offiziell vorgestellt.

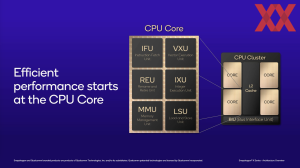

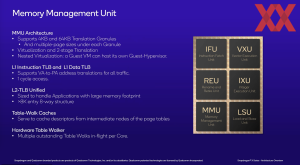

Jeder der CPU-Kerne besteht aus sechs Funktionsblöcken:

- IFU: Instruction Fetch Unit

- VXU: Vector Execution Unit

- REU: Rename and Retire Unit

- IXU: Integer Execution Unit

- MMU: Memory Management Unit

- LSU: Load and Store Unit

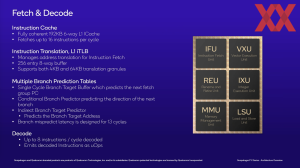

Im Front-End werden zunächst einmal die notwendigen Instruktionen aufgerufen und einsortiert. Der dazu bereitgestellte L1-Instruction-Cache misst 192 kB. Aus diesem können pro Taktzyklus 16 Instruktionen gelesen werden. Immer wichtiger wird eine möglichst schnelle und gute Sprungvorhersage, welche die nächste Instruktion bereits vorhersehen will, um diese dann schneller aufrufen zu können. Ein ausgewogenes Verhältnis aus Treffern und verfehlten Vorhersagen ist hier wichtig, denn eine fehlerhafte Vorhersage sorgt dafür, dass Instruktionen und Daten wieder verworfen werden müssen, was Leistung kostet.

Die Decoder-Einheit macht aus den Instruktionen sogenannte µOps (Mikro-Operationen), die in einem µOP-Cache abgelegt werden, bevor sie dann an die Ausführungseinheiten übergeben werden.

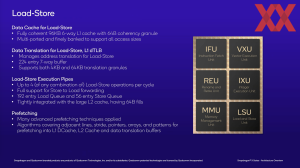

Die eigentlichen Berechnungen werden dann in den Ausführungseinheiten durchgeführt. Zuvor werden diese durch den Scheduler (Reservation Stations) in die richtige Reihenfolge gebracht. Für die IXU sieht Qualcomm eine 6-Wide und 64 Bit tiefe Pipeline mit 20 Ausführungen in der Queue vor, für die VXU sind es vier Pipelines mit 128 Bit und 48 Ausführungen in der Tiefe und für die LSU sprechen wir von ebenfalls vier Pipelines und 128 Bit bei 16 Ausführungen in der Queue.

Bis zu sechs Integer-Operationen können pro Taktzyklus ausgeführt werden. Hinzu kommen bis zu zwei MUL/MLA-Operationen pro Takt. Die Vektor-Einheiten haben eine 128 Bit Tiefe und können damit bis zu vier FP32-Operationen pro Takt ausführen. Auch Datentypen wie INT8, INT16 werden neben FP16, FP32 und FP64 unterstützt.

Um am Ende die Ressourcen für weitere Berechnungen wieder freizugeben, gibt es ein Instruction Retirement, welches acht µOps pro Taktzyklus aus der Queue entfernt und in einen Re-Order-Puffer mit 650+ µOps ablegt. Von hier aus können sie erneut aufgerufen werden.

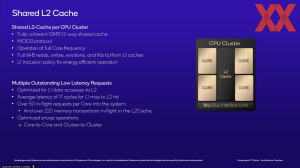

Neben der Ausführung der Instruktionen müssen in diesen natürlich die Daten verarbeitet werden, die sich zuvor irgendwo in den Caches befinden. Jedes CPU-Cluster mit vier Kernen hat 12 MB shared L2-Cache. Dieser arbeitet mit dem gleichen Takt wie die CPU-Kerne. Theoretisch ist der Cache mit seiner Anbindung in der Lage, bis zu acht Kerne zu versorgen. Dies ist sicherlich ein Überbleibsel der vorherigen Entwicklung hin zu einem Server-Prozessor mit deutlich mehr Kernen pro Cluster.

Ein Fokus in der Entwicklung der Cache-Hierarchie war es, die Latenzen für Cache-Misses so niedrig wie möglich zu halten. So vergehen bei der Suche nach Daten im L1-Cache mit einem Miss nur 17 Taktzyklen, bis diese Daten im L2-Cache gefunden werden können. Snoop-Operationen überwachen den Adressbereich stetig, um eventuelle Konflikte zwischen den Caches vorzubeugen. Dies gilt auf Kern-zu-Kern-Ebene ebenso wie zwischen den Clustern.

Eine Bus Interface Unit (BIU) verbindet die drei CPU-Cluster und den L2-Cache über einen Interconnect mit dem darüber liegenden Sub-System, welches unter anderen einen System Level Cache (SLC) mit 6 MB enthält. Aus den 3x 12 MB L2-Cache pro Cluster und 6 MB SLC ergeben sich die insgesamt 42 MB Cache eines Snapdragon X Elite oder Plus.

Die Latenzen von den CPU-Kernen zum SLC beträgt nur 26 bis 29 ns, die Bandbreite liegt bei 135 GB/s und deckt sich damit mit der Anbindung des DRAMs. Der verwendete LPDDR5X kommt auf 8.448 MT/s und ist über ein Acht-Kanäle zu jeweils 16 Bit breites Speicherinterface angebunden. Die Speicherbandbreite liegt damit ebenfalls bei 135 GB/s, so dass Qualcomm hier eine gewisse Symmetrie zwischen der Speicheranbindung und die des SLC zu den Clustern gewährleisten kann. Die Latenz zum DRAM wird mit 102 bis 104 ns angegeben.

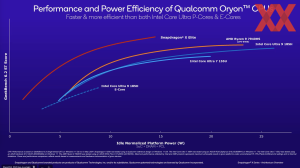

An dieser Stelle wiederholt Qualcomm die nach eigener Einschätzung und durch eigene Benchmarks belegte Vorreiterschaft bei den CPU-Architekturen. Oryon soll schneller und effizienter sein, als alles, was AMD und Intel aktuell zu bieten haben. Allerdings wird sich der Snapdragon X Elite und Plus auch gegen die neuen Ryzen-AI-Prozessoren auf Basis der Zen-5-Architektur behaupten müssen und etwas später steht auch Intels Lunar Lake an, wo es ebenfalls große Sprünge in der IPC-Leistung gegeben hat.

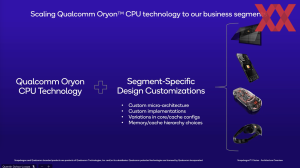

Das Oryon-Design, wie nun vorgestellt, kommt in dieser Form – dreimal Vierkern-CPU-Cluster, 12 MB L2-Cache pro Cluster und 6 MB SLC – beim Snapdragon X Elite und Plus zum Einsatz. Qualcomm kann das Design aber auch für anderen Produktsegmente anpassen. Auf die Notebooks und Office-Systeme könnten Varianten für Tablet, Smartphones oder aber Bereiche wie Automotive und VR/AR folgen. Dazu kann Qualcomm dann die Anzahl der Kerne, Größe der Caches und vieles mehr anpassen.

Qualcomm Adreno X1 GPU

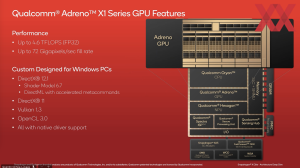

Bei der verbauten GPU des Snapdragon X Elite und Plus handelt es sich um die siebte Generation der Adreno-GPU. Sie hört auf den Namen Andreno X1. Die GPU arbeitet in den Prozessoren mit einem Takt von bis zu 1,5 GHz und kommt damit auf eine Rechenleistung von bis zu 4,6 TFLOPS für FP32-Berechnungen.

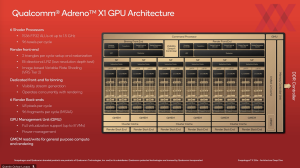

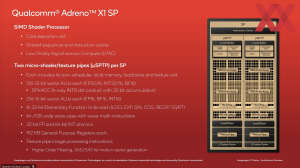

Aufgebaut ist die GPU aus sechs Shader Prozessoren (SP) und damit kommt sie auf 1.536 FP32-Recheneinheiten: 2x 64 32 Bit ALUs pro SP + 2x 128 16 Bit ALUs. Es handelt sich um SIMD Shader Prozessoren mit jeweils zwei Micro-Shader- und Textur-Pipelines. Jede dieser Pipelines hat ihren eigenen Scheduler, eigenen lokalen Speicher sowie eigene Load/Store- und Texture-Einheiten.

Die insgesamt 128 Vektoreinheiten kommen auf 32 Bit und können FP32-, FP16-, INT32-, INT16- sowie BF16-Berechnungen ausführen. Hinzu kommen 256 Bit Vektoreinheiten für FP16, BF16 und INT16. Die Wave-Größen können auf 64 und 128 Bit festgelegt werden.

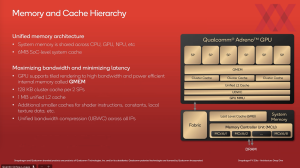

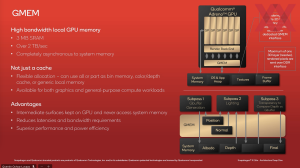

Zum Ablegen der Daten gibt es einen 128 kB Cluster Cache für jeweils zwei Shader Prozessoren. Hinzu kommen 1 MB an L2-Cache über alle SPs hinweg. Über den Interconnect-Fabric hat die GPU Zugriff auf den 6 MB großen Last Leven Cache (LLC), bzw. System Level Cache.

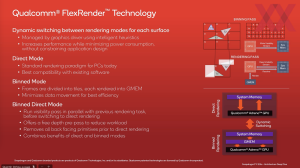

Zwischen dem L2-Cache und den Shader Prozessoren sitzt aber auch noch ein schneller GMEM. Dieser ist ein 3 MB großer SRAM mit einer Bandbreite von mehr als 2 TB/s. Er arbeitet asynchron zu den weiteren Cache- und Speicherebenen und steht ausschließlich der GPU zur Verfügung. In ihm können alle für eine GPU in der Verarbeitung wichtige Daten abgelegt werden. Sowohl grafische Berechnungen als auch Compute-Workloads können ihn verwenden.

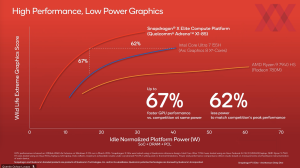

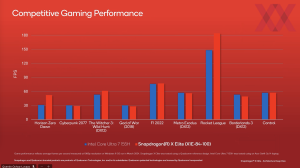

Die Adreno-X1-GPU soll in der größten Ausbaustufe (Adreno X1-85) um bis zu 67 % schneller als die integrierten Lösungen von AMD und Intel sein, dabei jedoch bis zu 62 % weniger Leistung aufnehmen. Die Vorab-Benchmarks hinterließen hinsichtlich der GPU-Leistung eher ein gemischtes Bild. Hier wird es darauf ankommen, ob Qualcomm den Treiber bereits auf das jeweilige Spiel angepasst hat und ob es in einer Emulationsschicht ausgeführt werden muss oder nativ auf ARM-Befehlscode arbeitet.

Ein erstes Fazit

Im Grunde liegen die Karten nun auf dem Tisch. Wir kennen die Oryon-CPU als generelles Konstrukt und nun auch die Details der CPU-, GPU- und NPU-Architektur. Qualcomm sieht sich in allen Belangen vor der Konkurrenz – Leistung, Effizienz, Funktionsumfang und vieles mehr. Dies gilt es nun in der Praxis unter Beweis zu stellen.

Zum Start werden wir in den kommenden Wochen zahlreiche unterschiedliche Designs mit dem Snapdragon X Elite und Plus sehen – zum einen 2-in-1 mit maximal 20 W bis über 100 W, wo dann auch die Gaming-Leistung eine Rolle spielt. Ob die Prozessoren ihre Versprechen über ein derart breites Leistungsband werden halten können, werden die Tests zeigen müssen.