Werbung

Nachdem wir bereits in der vergangenen Woche einige Details zur Zen-5-Architektur und den darauf basierenden Produkten veröffentlicht haben, ergänzte AMD diese nun noch vor dem Start der Ryzen-9000-Prozessoren in der kommenden Woche mit weiteren Daten.

Die Zen-5-Architektur bildet für AMD eine Basisarchitektur für die kommenden Jahre. Innerhalb der bisherigen Zen-Architekturen gab es immer wieder kleinere und größere Änderungen. Zen 5 setzt nun gewisse Vorgaben, die auch in den kommenden Generationen beibehalten werden und als eine Art Fundament dienen.

Mit der Umsetzung in den Zen-5- und den kompakten Zen-5c-Kernen bietet AMD auch eine gewisse Flexibilität, die sich auch in der Form äußert, dass AMD die Zen-5-Architektur für gewisse Produkte anpassen kann. So verfügt diese über einen 512 Bit breiten Fließkomma-Datenpfad und nutzt diesen in der Unterstützung von AVX512 auch in der vollen Breite, AMD kann die Kerne aber auch so konfigurieren, dass dieser Fließkomma-Datenpfad nur 256 Bit breit ist.

Diese Flexibilität nutzt man für Strix Point bzw. die Ryzen-AI-300-Prozessoren. Im Zen 5 Core Complex mit den Zen-5- und Zen-5c-Kernen hat man die Architektur so umgeändert, dass diese jeweils den 256 Bit breiten Fließkomma-Datenpfad verwendet. Für Granite Ridge bzw. die Ryzen-9000-Prozessoren wird die volle Breite von 512 Bit verwendet und dies dürfte auch bei den EPYC-Prozessoren auf Basis der Zen-5-Architektur der Fall sein.

Das der Zen 5 Core Complex in Strix Point für beide Kern-Typen jeweils 256 Bit verwendet, liegt an der notwendigen ISA-Kompatibilität über alle Kerne hinweg, die AMD stets anstrebt.

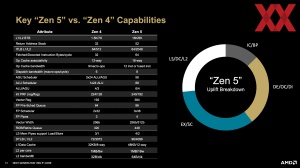

In der Architektur beginnt alles mit der Sprungvorhersage. Diese macht in der Zen-5-Generation pro Taktzyklus mehr Vorhersagen und soll auch eine höhere Genauigkeit erreichen. Ermöglicht wird dies durch einen L1 BTB (Branche Target Buffer) in der Größe des L2-Cache (16K) und einen größeren Adress Stack mit 52 Einträgen für die entsprechende Rückmeldung. Das Vorhersage-Fenster pro Taktzyklus wächst auf drei an. Für gewisse Berechnungen ist der L1-Cache zu klein und es müssen Daten aus dem L2-Cache abgefragt werden, zu denen es aber ebenfalls Sprungvorhersagen geben soll. Zu diesem Zweck hat AMD den L2-Cache ITLB (Instruction Translation Lookaside Buffer) auf 2.048 Einträge erweitert. Zudem können Instruktionen nun mit 64 anstatt derer 32 Bytes pro Taktzyklus abgerufen werden.

Auf der Decode-Seite bekommt der Op-Cache 33 % mehr Verknüpfungen/Assoziativität und auch die Bandbreite an Instruktionen wächst auf zweimal sechs und demnach zwölf pro Taktzyklus an. Es gibt zwei Decode-Pipelines die parallel arbeiten und vier Instruktionen pro Taktzyklus verarbeiten können. Im SMT-Modus bekommt jeher Thread eine dedizierte Decoder-Pipeline.

Am Ende werden acht Instruktionen pro Taktzyklus an die Fließkomma- und Integer-Einheiten versendet. Bei Zen 4 waren es derer sechs.

Der Integer-Scheduler kann acht Dispatch-, Rename- und Retire-Funktionen ausführen. Bei den Integer-Einheiten verfügt die Zen-5-Architektur nun über sechs ALUs (Arithmetic Logic Unit) und vier AGUs (Address Generation Units). Der Scheduler wird auf 56 Einträge bei den AGUs und 88 Einträge bei den ALUs erweitert. Der PRG (Physical Register File) wächst auf 240 Einträge an und der ROB (Re-Order Buffer) wird von 320 auf 448 Einträge erweitert. Im SMT-Modus wird der ROB auf 224 halbiert.

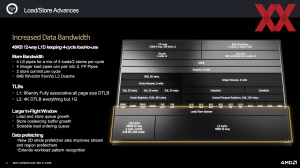

Der L1-Data-Cache ist nun 48 kB groß und umfasst bei der Zen-4-Architektur noch 32 kB. Die größere Kapazität geht mit einer Verbreiterung auf 12-Way einher, wobei man die Load-Latenz mit vier Taktzyklen beibehalten konnte. Der L1D-Cache kann vier Lese- und zwei Schreibzugriffe ausführen. Vier Integer Load Pipelines können zu zwei Fließkomma-Pipelines zusammengeführt werden.

Der DTLB (Data Translation Lookaside Buffer) ist für den L1-Cache nun 96 Einträge (vollständig assoziativ zu allen Page Sizes) groß und umfasst für den L2-Cache 4.096 Einträge. Die Sprungvorhersage spielt nicht nur in den Instruktionen eine wichtige Rolle, sondern auch die notwendigen Daten sollen bestenfalls vorab bereitgestellt werden. Dazu hat AMD eine sogenannte "2D Stride"-Vorhersage entwickelt, die gewisse Muster in den Workloads erkennen soll.

Auf Seiten der Fließkomma-Einheiten spielt der 512 Bit breite Datenpfad sicherlich die wichtigste Rolle. Es gibt nun vier anstatt wie bisher mit Zen 4 nur drei Fließkomma-Pipelines, die eine Vektorbreite von 256 oder 512 Bit unterstützen. Möglich sind zwei Loads pro Taktzyklus oder ein Store. Die Latenz für Floating Points Adds (FADD) wird von drei auf zwei Taktzyklen reduziert.

Der Vektor-Register wird von 192 auf 384 Einträge erweitert, was mit der Verdopplung des Datenpfades einhergeht und nur eine logische Anpassung in der Verbreitung der Fließkomma-Berechnungen ist.

In der Befehlssatzarchitektur (ISA) gibt es ein paar neue Instruktionen:

- MOVDIRI/MOVD64B - move 4,8 or 64 bytes as a direct store, bypassing caches

- VP2INTERSECTIDQ] - AVX512 vector pair intersection to a pair of mask registers

- VNNI/VEX – extends AVX512 instruction to VEX encoding

- PREFETCH[I*] – software prefetch of instruction lines into cache hierarchy

Cache-Hierarchie und SoC-Design

Mehr und breitere Ausführungseinheiten verlangen auch nach mehr Bandbreite in den verschiedenen Cache-Stufen. Für den Core Complex mit den Zen-5-Kernen sieht dies wie folgt aus:

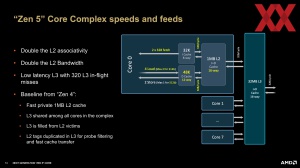

Der L1-Data-Cache ist nun 48 kB groß und umfasst bei der Zen-4-Architektur 32 kB. Zwischen dem L1- und L2-Cache wird die Bandbreite von 32 auf 64 Bytes pro Taktzyklus verdoppelt. Ausgehend von einem Takt des Infinity Fabric von 1.800 MHz verdoppelt sich die Bandbreite zwischen L1- und L2-Cache von 57,6 auf 115,2 GB/s. Keinerlei Änderungen gibt es in der Bandbreite zwischen dem L2- und L3-Cache sowie in der Anbindung zum Speichercontroller. Hier bleibt es bei 32 Bytes pro Taktzyklus und bei 1.800 MHz Takt des Infinity Fabric bei 57,6 GB/s.

Der L1D-Cache bleibt bei 8-Way in seiner internen Bandbreite, der L1D wird nicht nur von 32 auf 48 kB größer, sondern auch die interne Bandbreite geht von 8-Way auf 12-Way nach oben.

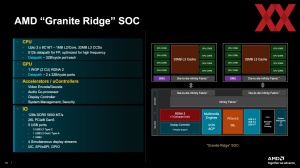

Dieser Core Complex findet in Granite Ridge bzw. den Ryzen-9000-Prozessoren verwendet. In jedem der bis zu zwei CCDs (Core Complex Dies) befinden sich bis zu acht Zen-5-Kerne und jeweils 32 MB an L3-Cache.

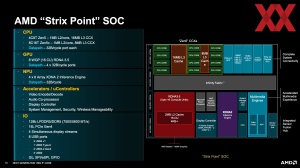

Für Strix Point alias Ryzen AI 300 setzt AMD auf einen Core Complex mit vier Zen-5-Kernen und 16 MB L3-Cache sowie einen weiteren Core Complex mit acht Zen-5c-Kernen und 8 MB L3-Cache. Erstmals in einem SoC-Design von AMD kommt ein asymmetrisches Verhältnis an L3-Cache-Kapazität zum Einsatz. Dies setzt auch voraus, dass AMD etwas mehr Arbeit in das Scheduling der Threads steckt, da die Unterscheidung nicht nur zwischen Zen-5- und Zen-5c-Kernen machen muss, sondern auch mit der L3-Cache-Kapazität im Hinterkopf.

Für die EPYC-Prozessoren auf Basis der Zen-5-Architektur wird AMD nach eigenen Angaben auf CCX-Designs setzen, die größer und kleiner als das sein können, was wir nun schon offiziell kennen. Es wird offenbar auch hier heterogene Designs geben. Bisher trennt AMD zwischen EPYC-Prozessoren mit den klassischen Kernen und solchen mit den kompakten Kernen. Auf Basis der kleineren Embedded-Designs kommen nur Prozessoren mit Zen-4-Kernen zum Einsatz, also auch hier bisher kein heterogenes Design.

Im SoC-Design für Strix Point sind die beiden CCX mit jeweils 32 Byte pro Taktzyklus für das Lesen und Schreiben an den Infinity Fabric angebunden. Die GPU kommt auf vier Datenpfade mit jeweils 32 Byte pro Taktzyklus. Die NPU ist wieder mit 32 Byte pro Taktzyklus an den Infinity Fabric angebunden.

Gehen wir hier von 1.600 MHz für den Takt des Infinity Fabric aus (so hoch konnte dieser in Phoenix und Hawk Point takten), dann sind die CCX und die NPU mit 51,2 GB/s angebunden und die GPU kommt auf 204,8 GB/s. Der Speichercontroller für DDR5 und LPDDR5 kommt auf 89,6 bzw. 120 GB/s, sodass wir je nach Workload hier eher in der Speicherbandbreite beschränkt sind.

Für Granite Ridge findet die Anbindung des CCX/CCD an den IOD ebenfalls per Infinity Fabric statt. Was das Schaubild nicht zeigt, ist die asymmetrische Anbindung, wie sie auch bei den Ryzen-7000-Prozessoren vollzogen wird. Der IOD kann mit 32 Byte pro Taktzyklus vom CCD lesen, aber mit nur 16 Bytes pro Taktzyklus schreiben. Dies hat dahingehend Auswirkungen, dass die Ryzen-Prozessoren mit nur einem CCD (Ryzen 7 9700X und Ryzen 5 9600X) im Lesedurchsatz limitiert sein werden. Dies konnten wir bei den Ryzen-7000-Prozessoren bereits darstellen. Für Strix Point gilt diese Einschränkung nicht. Hier sind beide CCX mit 32 Bytes pro Taktzyklus bidirektional angebunden.

Platz und Leistungsaufnahme der SerDes für den Infinity Fabric sind die Gründe, warum sich AMD im Chiplet-Design für diese asymmetrische Anbindung entschieden hat. Für ein monolithisches Design wie Strix Point spielen diese Faktoren keine Rolle, da die Integration auf Chipebene stattfindet.

Die integrierte GPU der Ryzen-9000-Prozessoren ist über zwei Datenpfade mit jeweils 32 Byte pro Taktzyklus angebunden. Der IOD ist zum Vorgänger identisch und entsprechend gibt es in diesem Bereich keinerlei Änderungen.

Zen 5c um 25 % kleiner als Zen 5

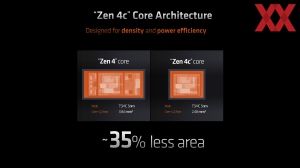

Mit der Ankündigung der kompakten Zen-4c-Kerne verwies AMD stolz auf den Umstand, dass diese Kerne zusammen mit dem dazugehörigen L2-Cache um etwa 35 % kleiner als die großen Zen-4-Kerne sind.

Für die kompakten Kerne auf Basis der Zen-5-Architektur fällt die Einsparung weniger groß aus. Anstatt 35 % sollen die Zen-5c-Kerne nur um etwa 25 % kleiner sein, als ihren großen Zen-5-Geschwister.

| Fertigung | Die-Größe | Transistoren | Dichte | |

| CCD (Durango, Ryzen 7000) | 5 nm | 71 mm² | 6,5 Milliarden | 92,9 MTr/mm² |

| IOD (Ryzen 7000) | 6 nm | 122 mm² | 3,4 Milliarden | 27,9 MTr/mm² |

| CCD (Eldora, Ryzen 9000) | 4 nm (N4X) | 70,6 mm² | 8,315 Milliarden | 117,78 MTr/mm² |

| IOD (Ryzen 9000) | 6 nm | 122 mm² | 3,4 Milliarden | 27,9 MTr/mm² |

| Fertigung | Die-Größe | Kern-Konfiguration | L2-Cache | L3-Cache | |

| Phoenix1 | TSMC 4 nm | 178 mm² | 8x Zen 4 | 8 MB | 16 MB |

| Phoenix2 | TSMC 4 nm | 137 mm² | 2x Zen 4 + 4x Zen 4c | 6 MB | 16 MB |

| Hawk Point1 | TSMC 4 nm | 178 mm² | 8x Zen 4 | 8 MB | 16 MB |

| Hawk Point2* | TSMC 4 nm | 137 mm² | 2x Zen 4 + 4x Zen 4c | 6 MB | 16 MB |

| Strix Point | TSMC 4 nm (N4P) | 232,5 mm² | 4x Zen 5 + 8x Zen 5c | 12 MB | 24 MB |

Das weniger kompakte Design für die Zen-5c-Kerne sowie deren Anzahl mit einem 4+8-Design wird auch einer der Gründe sein, warum die Chipgröße von Strix Point mit 232,5 mm² trotz Fertigung in 4 nm vergleichsweise groß ausfällt.

Es fehlen die Tests

Nun werden vor allem die Ryzen-9000-Prozessoren bald zeigen müssen, ob AMD seine Leistungsprognosen halten kann. Wir haben viele Prozessoren vorherigen Generationen von AMD und Intel erneut getestet, um eine frische Datenbasis zu haben. Die Ryzen-9000-Prozessoren werden ab dem 31. Juli verfügbar sein. Preise nennt AMD zum jetzigen Zeitpunkt aber noch nicht.