Werbung

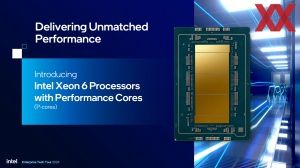

Gut drei Monate nach dem Start der Xeon-6700E-Serie mit Efficiency-Kernen alias Sierra Forest starten heute die großen Performance-Kern-Modelle der Xeon-6900P-Serie alias Granite Rapids. Uns steht auch ein Server mit zwei dieser Prozessoren zur Verfügung, den Test werden wir aber in den kommenden Tagen erst fertiggestellt haben. Zusammen mit dem offiziellen Startschuss schauen wir uns heute die Plattform sowie die vorgestellten Modelle etwas genauer an.

Die Xeon-6-Serie wird aus den SP-Modellen auf Basis des Sockel LGA4710 und den AP-Modellen auf Basis des Sockel LGA7529 bestehen - allesamt auf der Birch-Stream-Plattform. Erste Details dazu veröffentlichte Intel zur diesjährigen Computex. Die von uns bereits getesteten Prozessoren der Xeon-6700E-Serie sind SP-Modelle für den Sockel LGA4710, die nun von Intel veröffentlichten Prozessoren der Xeon-6900P-Serie verwenden als AP-Modelle den größeren Sockel LGA7529.

Damit zündet Intel die zweite Stufe im Veröffentlichungs-Rhythmus der Xeon-6-Serie. Im ersten Quartal 2025 werden dann mit Sierra Forest-AP die großen Xeon 6900E mit bis zu 288 Kernen pro CPU sowie mit Granite Rapids-SP die kleineren Xeon 6700P folgen. Hinzukommen werden die darunter platzierten Xeon 6500P, 6300P und der Xeon 6 SoC.

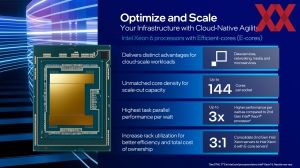

Mit der Xeon-6900P-Serie adressiert Intel den Bedarf nach maximaler Rechenleistung auf kleinstem Raum, während die Xeon-6700E-Series auf eine hohe Effizienz ausgelegt ist.

Für die Xeon-6-Prozessoren mit Performance-Kernen kommt die Redwood-Cove-Architektur zum Einsatz. Diese wird auch für die P-Kerne in Meteor Lake verwendet. Für die Xeon-6900P-Serie unterstützt die Redwood-Cove-Architektur AVX512 und jeder Kern bekommt auch etwas mehr L2-Cache spendiert. Zudem setzt Intel die Kerne auf einem Compute-Tile ein, der in Intel 3 gefertigt wird – für Meteor Lake war es noch eine Fertigung in Intel 4.

Auch wenn die Xeon-6900P-Serie auf maximale Leistung ausgelegt ist, so will Intel dennoch nicht die Effizienz aus den Augen verloren haben. Zuletzt musste sich Intel mit Sapphire Rapids und Emerald Rapids immer wieder den berechtigten Vorwurf gefallen lassen, die Rechenleistung stiege fast ausschließlich über eine höhere Anzahl an Kernen und eine höhere TDP an.

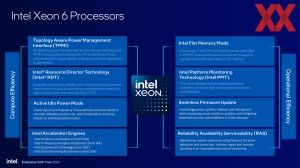

Der optionale Optimized Power Mode, den Intel schon mit der 4. und 5. Xeon-Generation anbot, ist mit der Xeon-6900P-Serie der neue Standard-Modus. Damit erreicht Intel gegenüber der 5. Xeon-Generation eine um bis zu 1,9fach höhere Leistung/Watt.

Einen weiteren Punkt den Intel mit der Xeon-6900P-Serie ansprechen möchte ist, dass Serverprozessoren in den wenigsten Fällen und dauerhaft zu 100 % ausgelastet sind. Zwar ist dies das Ziel eines Cloud- und Services-Anbieters, erreichen lässt sich dies jedoch nicht immer. Aus diesem Grund zielt der Optimized Power Mode in der Effizienz auf eine möglichst breite Spannung in der Auslastung.

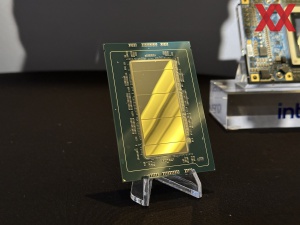

Bis zu 128 Kerne und 12 Speicherkanäle

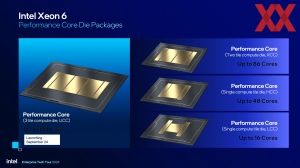

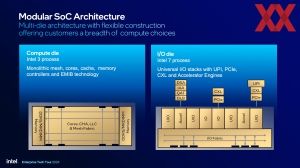

Aber nun zur Xeon-6900P-Serie selbst: Deren Produktpalette reicht bis zu Modellen mit 128 Kernen. Um auf 128 Kerne und die I/O-Funktionen der Plattform zu kommen, setzt Intel bei den Prozessoren der Xeon-6900P-Serie auf drei Compute-Tiles mit den P-Kernen sowie auf zwei I/O-Tiles, welche die I/O-Blöcke für PCI-Express 5.0, CXL 2.0 und auch die Beschleuniger enthalten. Die Compute-Tiles werden in Intel 3 gefertigt, während die I/O-Tiles aus einer Fertigung in Intel 7 kommen. Die Verbindung der Tiles erfolgt per EMIB.

Einige dieser I/O-Blöcke im I/O-Tile können frei konfiguriert werden, sodass sie entweder für PCI-Express- oder CXL-Lanes verwendet werden können. Die UPI-Blöcke können zudem als UPI zur Anbindung eines oder mehrerer weiterer Sockel eingesetzt werden. Für 1S- und 2S-CPUs verzichtet Intel teilweise darauf und kann daher mehr PCI-Express- und CXL-Lanes anbieten.

Egal ob Granite Rapids-AP oder ab dem ersten Quartal 2025 mit Sierra Forest-AP – die Plattform besitzt die gleichen I/O-Funktionen und Beschleuniger, wohingegen die Entscheidung für die Xeon-6900P- und Xeon-6900E-Serie einzig eine Wahl für den Einsatz von P- und E-Kernen bedeutet. Konkret bedeutet dies für Granite Rapids-AP, dass hier 12 Speicherkanäle, sechs UPI-2.0-Links und bis zu 96 PCIe-5.0- bzw. CXL-2.0-Lanes auf Plattformebene unterstützt werden.

Die Compute-Tiles mit bis zu der Xeon-6900P-Serie bezeichnet Intel als UCC (Ultra Core Count). 44 Kerne sind für den UCC-Chip vorgesehen, aber bei keinem Prozessor sind alle diese 44 Kerne aktiv. Bei 128 Kernen für das größte Modelle ergeben sich bei drei Compute-Tiles 42,6 Kerne pro Tile, was in der Form natürlich nicht funktioniert, sodass Intel zum Beispiel 42 + 44 + 44 aktive Kerne einsetzen wird.

Der Einsatz von drei Compute-Tiles mit P-Kernen der Xeon-6900P-Serie und später dann zwei Compute-Tiles mit E-Kernen der Xeon-6900E-Serie ist notwendig, damit Intel die 12 Speichercontroller auf der Plattform anbieten kann, denn diese befinden sich nicht in den I/O-Tiles, sondern in den Compute-Tiles. Im Compute-Tile sind alle Kerne und Caches über ein Mesh-Interconnect angebunden. Der Last Level Cache (LLC) steht allen Kernen zur Verfügung, es kann aber auch eine NUMA-Clustering gewählt werden. Die Speichercontroller befinden sich wie gesagt mit in den Compute-Tiles. Intel wählt diesen Ansatz sicherlich, um die Latenzen und Bandbreite zu den Kernen möglichst gering bzw. hochzuhalten.

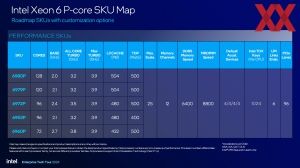

| Modell | Kerne | Basis-/Boost-Takt | All-Core-Boost | L3-Cache | TDP | DDR5 | MRDIMM | PCIe/CXL-Lanes |

| Xeon 6980P | 128 | 2,0 / 3,9 GHz | 3,2 GHz | 504 MB | 500 W | 12x 6.400 MT/s | 12x 8.800 MT/s | 96 |

| Xeon 6979P | 120 | 2,1 / 3,9 GHz | 3,2 GHz | 504 MB | 500 W | 12x 6.400 MT/s | 12x 8.800 MT/s | 96 |

| Xeon 6972P | 96 | 2,4 / 3,9 GHz | 3,5 GHz | 480 MB | 500 W | 12x 6.400 MT/s | 12x 8.800 MT/s | 96 |

| Xeon 6952P | 96 | 2,1 / 3,9 GHz | 3,2 GHz | 480 MB | 400 W | 12x 5.600 MT/s | 12x 8.800 MT/s | 96 |

| Xeon 6960P | 72 | 2,7 / 3,9 GHz | 3,8 GHz | 432 MB | 500 W | 12x 6.400 MT/s | 12x 8.800 MT/s | 96 |

Genau wie auch schon in der Xeon-6700E-Serie zeigt sich die Xeon-6900P-Serie sehr aufgeräumt und nicht mehr mit Dutzenden von Modellen. Zudem konzentriert sich Intel ausschließlich auf eine Differenzierung über die Anzahl der Kerne und deren Takt. Alle weiteren Funktionen sind identisch. Bei der 4. und 5. Xeon-Generation gab es noch Unterscheidungen in der Anzahl der Beschleuniger, der Multi-Sockel-Fähigkeit und vieles mehr. Das alles ist mit der Xeon-6-Serie nun Geschichte.

Schaut man sich die Xeon-6900P-Serie an, dann reicht diese von 72 bis 128 Kerne. Zwischen dem Xeon 6980P und 6979P liegen gerade einmal acht Kerne Unterschied, was sich auch in der Namensgebung ausdrückt. Mit 504 MB bekommt man hier auch den größten Cache geboten. Das Sweet Spot dürften der Xeon 6972P und 6952P mit 96 Kernen sein. Letztgenannter hat mit 400 W auch die niedrigste TDP zu bieten.

MRDIMMs verhilft Xeon-6900P-Serie zur Mehrleistung

Mit acht DDR5-Speicherkanälen mit 6.400 MT/s erreicht die Xeon-6700E-Serie in unseren Tests bereits ordentliche Speicherbandbreiten von 380 bis 424 GB/s. Die Xeon-6900P-Serie wird zudem MRDIMMs unterstützen, die Transferraten von 8.800 MT/s erreichen. MRDIMM ist die offizielle JEDEC-Bezeichnung des als MCR von Intel, Renesas und Sk hynix entwickelten Speicherstandards.

MCR steht für Multiplexer Combined Ranks und der DRAM arbeitet mit der halben Signalrate, in diesem Fall also 4.400 MHz. Zwei Pseudo-Kanäle werden per Multiplex-Verfahren wieder zusammengeführt und so ergeben sich aus 2x 4.400 MT/s eben zusammengenommen 8.800 MT/s. Gezeigt hat Intel den Betrieb von MCR bereits mit Granite Rapids in einer Quad-Channel-Konfiguration mit 6.400 MT/s, später dann auch deutlich schneller mit 8.800 MT/s und so wird er auch von den P-Kern-Xeons unterstützt werden.

HPC- und AI-Anwendungen sollen vom Einsatz von MRDIMM profitieren. Bis zu 33 % an Leistungsplus sind je nach Anwendung durch die höhere Speicherbandbreite zu erreichen.

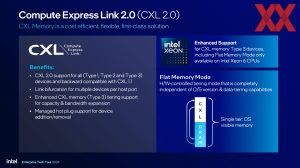

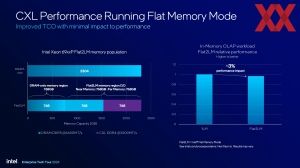

CXL 2.0 Type 3

Die Xeon-6-Prozessoren werden erstmals auch Type 3 für CXL 2.0 unterstützen. Für Type 3 geht es maßgeblich um die Möglichkeit der Speichererweiterung. Anstatt 2,3 TB (12x 192 GB) an DDR5 zu verbauen, können die Serverhersteller 1,5 TB (12x 128 GB) an schnellem DDR5 verbauen und ergänzen dies um 768 GB an CXL-Speicher, der als DDR4-3200 deutlich günstiger umzusetzen ist. Je nach Anwendung ist der Leistungsunterschied trotz dieser Maßnahme nicht besonders groß. Für Datenbankanwendungen spricht Intel von einer um 3 % geringeren Leistung, aber auch einer deutlichen Kostenersparnis.

Zudem gibt es einen Flat Memory Mode, in dem der Prozessor in eigener Hardware festlegt, welche Daten sich im DRAM oder in der CXL-Speichererweiterung befinden sollen. Dies ist natürlich abhängig davon, wie groß der DRAM selbst ist und ob der ständig benötigte Datensatz komplett in den DRAM passt oder nicht.

In CXL 2.0 Type 3 kann ein NUMA-Clustering des Speichers stattfinden. Dies beinhaltet auch die Kenntnis dieser Aufteilung gegenüber dem Hypervisor. Die Xeon-6900P-Prozessoren unterstützen zudem ein CXL Hetero Interleaving. Hier wird der CXL-Speicher in der Speichererweiterung zum DRAM-Adressraum hinzugenommen. Die Erweiterung der Kapazität geht auch mit einer höheren Speicherbandbreite einher, denn zu den acht bzw. zwölf Speicherkanälen kommen durch das CXL Hetero Interleaving vier weitere hinzu.

Das NUMA-Clustering spielt auch in der generellen Anbindung des Arbeitsspeichers eine Rolle. Der Standardmodus ist ein SNC3 (Sub NUMA Clustering), bei dem ein Compute-Die mit seinen Kernen direkt mit den vier Speicherkanälen des Chips zusammenarbeitet. Ein HEX-Modus ermöglicht eine Kommunikation über alle Compute-Tiles und Speicherkanäle hinweg.

Je nach Anwendung und Anforderungen an die Speichergröße und Latenzen kann entweder der SNC3- oder HEX-Modus sinnvoll sein. Mit einer immer größeren Anzahl an Kernen und dem Einsatz von Chiplets sind die Latenzen immer weiter gestiegen. Mit SNC3 bietet Intel hier aber eine Alternative – genau wie AMD mit dem Memory Interleaving bei den EPYC-Prozessoren.

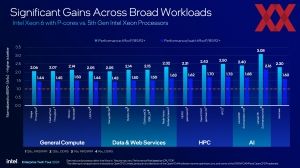

Intels eigene Benchmarks

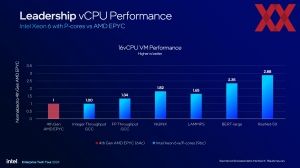

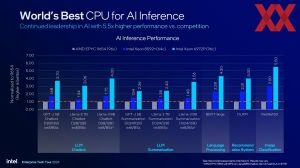

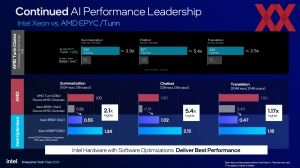

Natürlich kann es keine Ankündigung einer neuen CPU geben, ohne dass auch über deren Leistung gesprochen wird. Und natürlich kann es in der aktuellen Phase auch keinerlei Benchmarks geben, die ohne das Thema AI auskommen. Für Intel ist und bleibt die CPU eine Hardware-Basis für das Inferencing. Die AMX-Einheiten und die großen Caches sollen einen ausreichenden Durchsatz erlauben und mit der Xeon-6900P-Serie sieht sich Intel gegenüber der Konkurrenz aus dem Hause AMD gut aufgestellt.

Durch die höhere Anzahl an Kernen kann die Inferencing-Leistung gegenüber dem Vorgänger um den Faktor zwei gesteigert werden.

Die Xeon-6900P-Serie wird aber nicht nur gegen AMDs aktuelle EPYC-Generation antreten, sondern auch die kommende Turin-Generation. Bei all den Benchmarks und Grafiken darf man auch nicht vergessen, dass die verwendete Software eine große Rolle spielt. Optimierungen in der Software können große Unterschiede ausmachen. AMD und Intel lieferten sich nach der Computex bereits eine öffentliche Schlacht darum, welche Software-Basis nun für die Vergleiche verwendet werden sollte.

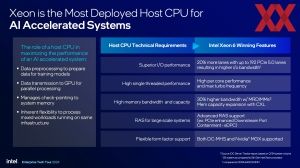

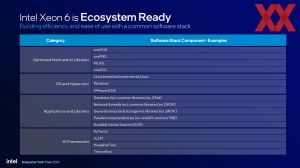

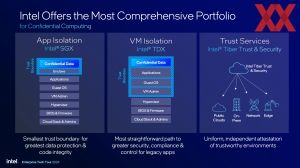

Aber Intel ist sich auch bewusst, dass im KI-Zeitalter die CPU meist nur ein Host für die deutlich schnelleren GPU-Beschleuniger ist. Aber Intel sieht die CPU daher noch lange nicht in den Hintergrund gerückt, denn auch dem Host kommt hier eine wichtige Rolle zu. Mit den Prozessoren der Xeon-6900P-Serie sieht sich Intel aber auch in dieser Hinsicht gut aufgestellt.

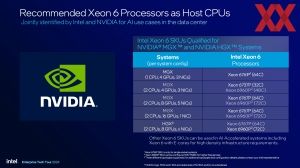

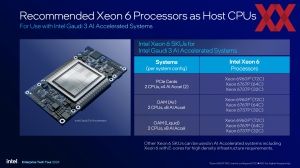

Mit einigen Modellen der Xeon-6900P-Serie stellt sich Intel speziell für den Einsatz als Host der DGX- und HGX-Systeme von NVIDIA auf. Natürlich bilden sie auch die x86-Basis für Server mit Gaudi-3-Beschleuniger.

In den weiteren Benchmarks vergleicht Intel die Leistung der Xeon-6900P-Serie in einer breiten Palette an Workloads sowie im HPC-Segment im Speziellen.

Heute fällt der Startschuss für die Xeon-6900P-Serie und damit beginnt offiziell die Auslieferung der ersten Systeme. Hyperscaler und OEMs haben die Prozessoren teilweise bereits erhalten und hat die Bereitstellung der Xeon-6900P-Serie bereits begonnen. Sie ergänzt die bereits veröffentlichte Xeon-6700E-Serie – bevor es dann im ersten Quartal 2025 mit der Xeon-6900E-Serie und bis zu 288 Kernen pro CPU und den kleineren Xeon-6700P-. 6500P- und 6300P-Modellen weitergeht.