Werbung

Aufgrund der Export-Bestimmungen darf TSMC keinerlei Chips mit einer gewissen Rechenleistung mehr nach China liefern. Davon betroffen ist unter anderem Huawei für den KI-Beschleuniger HiSilicon Ascend 910. In der Folge tauchte der Ascend 910B auf, der sich in einigen Details von der originalen Variante unterscheidet und offenbar nicht mehr von TSMC gefertigt wird.

Der Ascend 910 besteht aus einem "Virtuvian AI" getauften Compute-Die, einem "Nimbus V3" I/O-Die und vier HBM2-Chips. Am grundsätzlichen Aufbau tut sich nichts, aber der Wechsel in der Fertigung des Compute von TSMC N7 auf SIMC 7 nm (N+2) hat Auswirkungen im Hinblick auf die Komplexität des Compute-Die sowie dessen Ausbeute.

Zwischen dem Ascend 910 und 910B liegen drei Jahre. Die erste Version wurde 2019 vorgestellt, die zweite 2022. Die bisher berichteten Rechenleistung für FP16-Rechenoperationen ist von 220 bis 320 TFLOPS auf nun 280 bis 400 TFLOPS angestiegen. Dabei ist die Anzahl der KI-Kerne von 30 bis 32 auf 20 bis 25 gesunken. Durch einen fast doppelt so hohen Takt konnte die Rechenleistung trotz weniger KI-Kerne gesteigert werden. Aber auch beim On-Chip SRAM hat es Änderungen gegeben, die für eine höhere Rechenleistung sorgen könnten.

| Ascend 910 | Ascend 910B | |

| Fertigung | TSMC N7 | SMIC 7 nm (N+2) |

| Chipgröße | 456,2 mm² | 665,6 mm² |

| FP16-Rechenleistung | 220 - 320 | 280 - 400 |

| AI-Kerne (vorhanden) | 30 - 32 (32) | 20 - 25 (?) |

| Takt | 0,9 - 1,15 GHz | 1,65 - 1,85 GHz |

| On-Chip SRAM | 76 MB | 211 MB |

| Speicher | 32 GB (HBM2) | 32/64 GB HBM2E |

| Speicherbandbreite | 1.228 GB/s | 800/1.600 GB/s |

Einige der oben genannten Daten stammen vom Center foer Security and Emerging Technology (CSET) und nennen 30 bis 32 aktive AI-Kerne bei insgesamt maximal vorhandenen 32 KI-Kernen. Für einen Chip, gefertigt in 7 nm bei TSMC wäre eine solch hohe Ausbeute nicht weiter verwunderlich. Die Überführung in eine Fertigung bei SMIC 7 nm hat gleich mehrere Auswirkungen:

Wie viele aktive KI-Kerne der Compute-Die des Ascend 910B hat, ist nicht bekannt. Es sollen allerdings nur zwischen 20 und 25 Kerne aktiv sein. Sollten auch hier 32 Kerne vorgesehen sein, fiele die Ausbeute bei den Chips deutlich geringer aus.

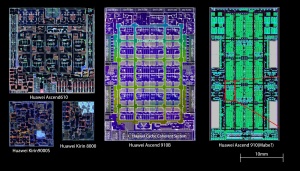

Ein weiterer Punkt ist die Chipgröße. Diese wächst von 456,2 mm² auf 665,6 mm² um 46 % an. Auch hier dürfte die noch nicht ausgereifte Fertigung bei SMIC eine Rolle spielen. Bei der Steigerung der Chipgröße spielen aber auch weitere Faktoren eine Rolle. Laut CSET gibt es zusätzliche Vektoreinheiten in den KI-Kernen sowie eine andere Zählweise in der Rechenleistung in der Kombination der Vektor- und Matrix-Rechenleistung. Allein durch letztgenannte Maßnahme steigt die theoretische maximale Rechenleistung pro Kern leicht an. Die nun folgenden Dieshots stammen von Kurnalsalts.

Der KI-Beschleuniger HiSilicon Ascend 910 hat auf dem Papier eine Rechenleistung einer A100 von NVIDIA. Soweit, die Theorie, denn in der Praxis soll die Rechenleistung weiter darunter liegen. Wo der Ascend 910B landet, ist nicht bekannt. Aktuell setzt Huawei den KI-Beschleuniger nur in der eigenen Cloud ein, will ihn aber auch über Baidu, Tencent und iFLYTEK anbieten.

Die Exportbeschränkungen für TSMC haben Auswirkungen auf Huawei in dem Sinne, dass SMIC weder in der Kapazität noch in der Ausbeute das liefern kann, was TSMC am Huawei liefern konnte. Aber es zeigt sich auch, welchen technischen Stand China in Form von SMIC schon erreicht hat. Offen ist die Frage, in welchem Tempo die chinesischen Chipfertiger gegenüber den westlichen Unternehmen werden aufholen können. SMIC und YMTC sind hier die beiden Größen am chinesischen Chipmarkt und als DRAM-Spezialist hat YMTC zuletzt gezeigt, dass man inzwischen riesige Kapazitäten benötigt, die man größtenteils bereits aus eigenem Lande decken kann.