HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 115.245

... weiterlesen

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

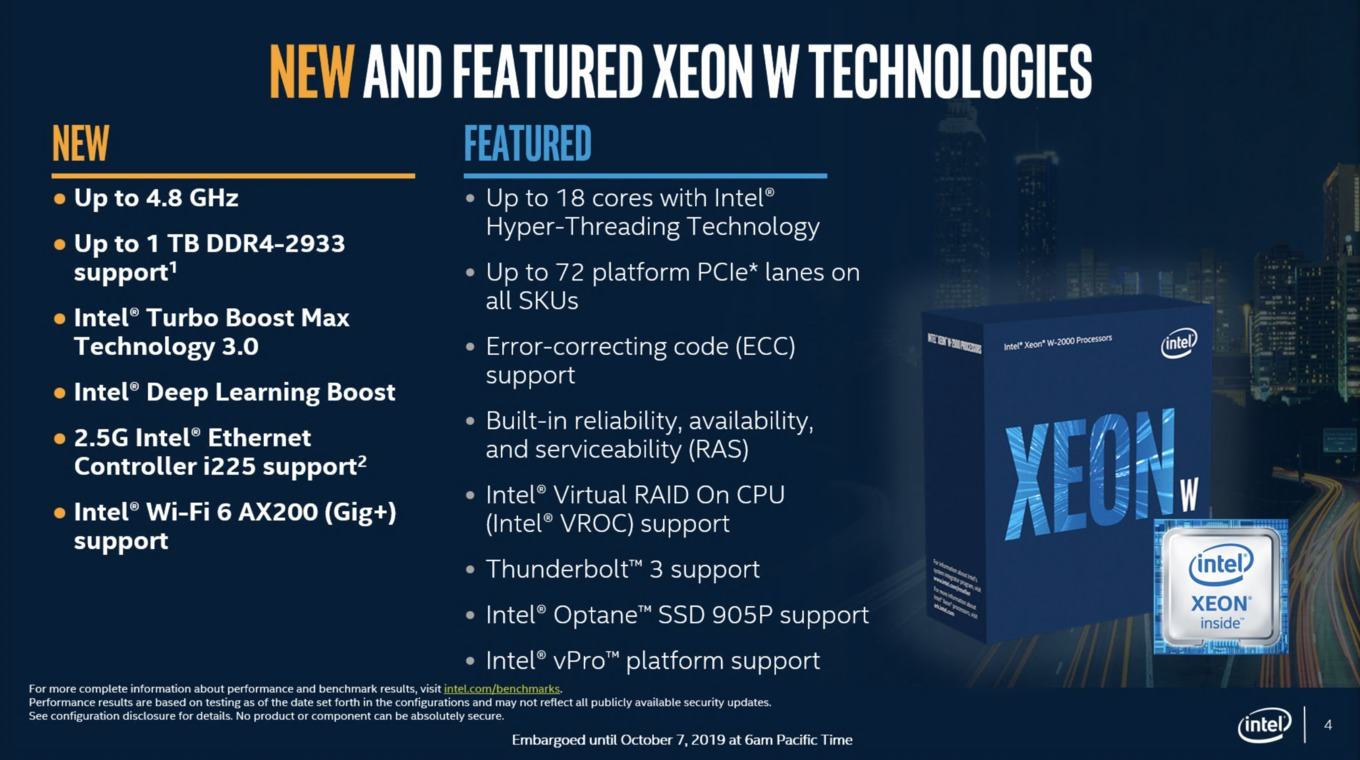

Das ist schlecht formuliert, denn die Plattform bietet bis zu 72 PCIe Lanes, die Prozessoren selbst haben ja wie ihre Vorgänger 48 Lanes, plus der 4 für die Anbindung des C422, also nach AMD Zählweise dann 52. Da steht doch auch extra "Up to 72 platform PCIe lanes on all SKUs" auf der Folie.Alle Xeon-W-Prozessoren der 2200-Serie bieten bis zu 72 PCI-Express-Lanes

Zumindest bisher hat Intel da noch keine direkte Konkurrenz von AMD, da die TR bisher als Desktop CPUs angepriesen und vermarktet werden, während die Xeon-W als Workstation CPUs platziert sind. Dies ist aber ein weiterer Hinweis das sich das mit TR3000 ändern dürfte und AMD diese dann auch offiziell als Workstation qualifiziert.eine Reduzierung der Preise ist wohl für Intel eine Maßnahme, um die Xeon-W-Prozessoren gegen die starke Konkurrenz von AMD zu stellen.

Den Preiskampf wird Intel verlieren, wenn sie nicht tatsächlich anfangen die Dinger unterhalb der Produktionskosten zu verkaufen.

Das "selbst fertigen" hat aber auch den Nachteil, dass Intels Kapazitäten futsch sind. Intel kommt nicht hinterher, weil der 10nm-Prozess im Sack ist und 14nm++++++++ aus dem letzten Loch pfeift.Bin mir fast sicher das die noch immer sehr gut dran verdienen gerade WEIL sie selbst fertigen, im Gegensatz zu AMD.

Der Ramsch muss sofort raus!

Intels verzweifelter Versuch noch einige Kunden durch den Preis zum Kauf zu bewegen.

Die werden schon ahnen, was noch mit Ryzen TR 3000 kommt!

Das Problem von Intel wird aber sein, dass AMD durch den modularen Aufbau schlicht viel billiger fertigen kann.

Die riesigen monolithischen CPUs erzeugen in der Produktion einfach mehr defekte Ware.

Den Preiskampf wird Intel verlieren, wenn sie nicht tatsächlich anfangen die Dinger unterhalb der Produktionskosten zu verkaufen.

Als ob sie je eine Qualität gehabt hätte, der hat nur Gamerkind nachgeäfft. Das die großen monolithischen CPUs mehr teildefekte Dies haben, ist klar und nicht neu, aber ebenso lange gibt es die Politik diese dann für CPUs mit weniger aktiven Kernen zu verwenden als auf dem Die sind. Dies machen Intel und AMD schon sehr viel Jahren so und so ausgereift wie die 14nm Prozesse bei Intel inzwischen sind, sollte die Ausbeute dort inzwischen nun wirklich schon sehr gut sein.Deine Beiträge verlieren auch immer mehr an Qualität, schade eigentlich.

Als ob sie je eine Qualität gehabt hätte, der hat nur Gamerkind nachgeäfft.

Wieso nur 48 Lanes? Außerdem sind die Rome Server CPUs und bisher gibt es nicht einmal Versionen mit etwas höheren Takt, wie es sie noch von den Vorgängern gab, während die Xeon-W eindeutig Workstation CPUs sind. Bei den TR 2990WX die AMD als Desktop CPU bezeichnet, wollten so viele Leute aus dem W in der unbedingt ableiten das es Workstation CPUs wären, bei den Xeon-W gibt es auch das W und Intel sagt sogar ganz offiziell, dass es Workstation CPUs sind! Wieso will man die nun mit dem Rome vergleichen? Deren künftige Gegner dürften die TR 3000 werde, wenn AMD diese dann offiziell als Workstation Plattform qualifiziert.

Außerdem braucht man ja nicht für jede Anwendung so viele Lanes oder auch extrem viele Kerne oder extrem viel RAM. Die Wahl der richtigen CPU hängt immer vor allem vom geplanten Einsatz ab!

Was bringen dir die vielen NVME und 40 GBE ? Steht dein Server im Rechenzentrum und hast darauf Anwendungen laufen wo Pro Sekunde tausende oder zehntausende Zugriffe erfolgen ? Oder ist das wieder mehr so ne Spielerei ? Ist ne ernstgemeinte Frage.

Wer will diesen gammeligen Müll noch? AMD forever!

Wenn du beruflich mal mit Rancher/K8s und großen Elasticsearch Clustern zu tun hast und privat gerne damit rumspielen möchtest, brauchst du IOPS ohne Ende. Nebenbei arbeite ich noch mit DPDK als Stresstests für Anwendungen, da können die CPUs nie hoch genug takten, wobei ich das aber eher auf der Arbeit teste, da es mir daheim an passenden Gegenspielern dazu fehlt. Meine PCs sind daheim auch schon mit 10G angebunden, ivm Resilio Sync ganz nett nicht immer den PC die halbe Nacht anlassen zu müssen für Backups oder ihn vollgestopft zu haben mit Platten, die Shares zum Zwischenspeichern sind mit 10G ja ausreichend schnell angebunden. Mittlerweile merke ich auch, das 8 HDDs als VM Storage trotz viel RAM, nativem Solaris ZFS und einer Intel Optane als SLOG ziemlich träge und lahmarschig ist. Außerdem kosten die 1TB P4510 SSDs nicht mehr so viel, 4-8 Stück davon gestripped mit Sicherung auf dem RAIDZ2 Plattenpool gehen garantiert ab wie Lutzie

Nebenbei dient der Server noch als Steamcache auf unserer LAN-Party mit 60-80 Usern und lahmer 50 Mbits Leitung.

Dich kann man nur noch auf ignore setzen.

Iss ja auch logisch, jetzt wo er weg ist, hab ich nix mehr zum nachäffen ergo Qualität der Beiträge gesunken! Ein Teufelskreis /:

So als ganz grobe Richtung. Real wird das Verhältnis sicher bisschen anders sein, aber der IO DIE kostet eben nicht nichts... Und die Chiplets auch nicht. Genau so wie Intels Output da exorbitante Kosten verursacht. Nur so wird das hier immer dargestellt...

So als ganz grobe Richtung. Real wird das Verhältnis sicher bisschen anders sein, aber der IO DIE kostet eben nicht nichts... Und die Chiplets auch nicht. Genau so wie Intels Output da exorbitante Kosten verursacht. Nur so wird das hier immer dargestellt...

Das ist ein Fake Account.

Danke für deine ehrliche Antwort, also wie vermutet mehr eine Spielerei. Habe da nichts gegen, wollte es nur wissen.

Naja, aber es bringt mir ja beruflich was, klar braucht Privat idr kaum einer 40G, selbst 10G oder 1G bräuchte man nicht, aber es ist schon schön es zu haben

Übrigens noch fix zum Behauptung mit den Chiplets. Der Rome IO DIE ist grob 430mm², die Chiplets ~75mm². AMD bekommt also auf die Größe des IO DIEs ca. 5,73x Chiplets theoretisch... Bei ca. doppelten Kosten pro belichteten mm an Waferfläche für 7nm bei TSMC schleppt man für alle teildeaktivierten Epyc Romes nicht nur die volle DIE Size beim IO Chiplet mit sondern auch die Chiplets um auf die L3 Cachegrößen zu kommen.

Jo, nur "mal eben". Hat auch keinen Einfluss auf Defekte oder so.Nur mal im Vergleich, Intel fertigt den größten XCC DIE mit knapp 700mm², das sind gerade mal 65% mehr Fläche als AMD in JEDEM Epyc einfach so rumschleppt, scheiß egal ob benötigt oder nicht.

Und weil der I/O Die ja auch mit so vielen Transistoren ausgestattet ist und absolut gar keine redundanten Elemente hat, genauso viele Masken benötigt und die gleiche Komplexität wie ne CPU hat, ist die Ausbeute mit den CPUs auch total vergleichbar.Im für Intel billigen, weil durch lange Erfahrung sehr hohe Ausbeute alt Prozess von 14+++++++++++++++ oder wie viele Plus auch immer...

Da können die noch so günstig an 7nm Chiplets kommen, das riesen IO Ding macht hier 1/4-1/3tel der Waferkosten alleine für sich. Und im Verhältnis sogar noch mehr, wenn da eben kein 64C Rome bei raus kommt - bei 32C und vier Chiplets sinds ~430mm² für den IO DIE + ~300mm² für die Chiplets. Halbe Kosten beim IO DIE auf den mm² macht also schon 2/3tel der Kosten.

Noch witziger ist der Vergleich HCC DIE Intel vs. IO DIE AMD. Das sind unwesentliche 40mm² oder so Unterschied. Das kostet real also am Silizium ziemlich ähnlich. So steckt also in jedem Rome ein Kostenblock eines HCC 18C Skylake based Intel DIEsSo als ganz grobe Richtung. Real wird das Verhältnis sicher bisschen anders sein, aber der IO DIE kostet eben nicht nichts... Und die Chiplets auch nicht. Genau so wie Intels Output da exorbitante Kosten verursacht. Nur so wird das hier immer dargestellt...

Hast du den Zug verpasst? Zeig mir mal den Intel 64 Kerner und dessen Ausbeute. Ich hab da mal was bei semiaccurate gelesen, was da mal eben gar nicht so rosig klang. Gut, der Typ ist wahrscheinlich auch nur ein Vollidiot der keine Ahnung hat oder so.So naiv hier von "günstiger" als Intel zu philosophieren, schaffen auch nur die treuen Anhänger der Marketingfolien.

Ja, das ist auch Intels einziger Punkt der ihnen das Geschäft so halbwegs rettet: Selbstkostenfertigung. Sie können es billiger, aber nicht besser und schon gar nicht konkurrenzfähiger. Wo ist im Lineup da oben ein 64 Kerner mit 128 PCIe Lanes?Einfach mal Hirn einschalten würde dabei schon helfen. Ganz ohne Zahlen sind das logische Schlussfolgerungen mit nur einer einzigen Annahme, die nicht belastbar ist -> Intel kann 14nm mindestens genau so günstig produzieren wie AMD ihren IO DIE bei gleicher Fläche kosten wird. Wäre Intel hier sogar noch ne Ecke günstiger (weil Selbstkostenfertigung intern) - geht die Rechnung gleich 2x nicht auf. Aber hey, das interessiert euch ja idR eh nicht. Hauptsache die Hucke vollhauen

Da AMD keine eigene Fab hat, ist das Silizium pro Stück *gleichwertiger* Technologie teurer. Allerding hat AMD auch gar nicht das Kapital ne eigene Fab zu bezahlen. Die Kosten dafür gehen in die Milliarden und allein die Entwicklungskosten für 7nm waren höher als AMDs kompletter Umsatz. Damit sich das überhaupt lohnen würde, müsste AMD massive Stückzahlen umsetzen - ähnlich wie Intel.Ach und bevor es kommt, für AMD ist das ganze trotzdem stimmig. Denn ihre Chiplet Strategie sorgt dafür, dass sie einen viel größeren Marktbereich mit ein und der selben Fertigung abdecken können. Das ist in Summe ab einem gewissen Volumen nicht die kosteneffizienteste Methode. Aber ohne dieses Volumen eben ganz sicher günstiger, als für alle Marktbereiche ne eigene Produktion hoch zu ziehen.

Heist unterm Strich, JA, die Chiplets lohnen für AMD. Aber NEIN, es ist nicht davon auszugehen, dass sie dadurch günstiger als Intel fertigen.

65% mehr Fläche? 700mm² sind keine 63% mehr als 430mm², also nur die Größe des I/O Chips. Wenn auch noch in jedem Rome immer 8 Chiplets stecken (keine Ahnung ob dies so ist, gibt es dazu Quellen?), kommen noch 8*75mm² = 600mm² dazu und dann stecken im Rome schon 1030mm² Diefläche (fast 50% mehr als die 700mm²) und wenn man die Kosten für die 7nm Chiplets mit dem doppelten Preis wie für 12/14nm ansetzt, dann kommt man bei Rome mit 8 Chiplets auf Kosten wie für 1630mm², bei einem mit 4 Chipets wären es dann Kosten wie für 1030mm² in 12/14nm. Ob die Kosten von AMD bei GF nun höher oder geringer als die von Intel für seine eigene 14nm[+/++] Fertigung sind, wissen wir nicht, aber bei der Größe von Intel und GF dürfte die Skaleneffekte eher zu Gunsten von Intel ausfallen und GF muss ja auch Geld verdienen, kann also auch an AMD nicht zum Selbstkostenpreis abgeben.Übrigens noch fix zum Behauptung mit den Chiplets. Der Rome IO DIE ist grob 430mm², die Chiplets ~75mm². AMD bekommt also auf die Größe des IO DIEs ca. 5,73x Chiplets theoretisch... Bei ca. doppelten Kosten pro belichteten mm an Waferfläche für 7nm bei TSMC schleppt man für alle teildeaktivierten Epyc Romes nicht nur die volle DIE Size beim IO Chiplet mit sondern auch die Chiplets um auf die L3 Cachegrößen zu kommen.

Nur mal im Vergleich, Intel fertigt den größten XCC DIE mit knapp 700mm², das sind gerade mal 65% mehr Fläche als AMD in JEDEM Epyc einfach so rumschleppt, scheiß egal ob benötigt oder nicht.

Eben und außerdem kann Intel die Dies mit defekten Kernen ja auch für die Modelle mit weniger Kernen verwendet, keine Ahnung wie viel Redundanz AMD im I/O Chip bei Teildefekten hat, aber wenn es nicht der I/O Bereich für die Anbindung von Chiplets ist die dann bei kleineren Modellen nicht bestückt werden, so müsste es bei den PCIe Lane und RAM Controller mehr geben als benötigt werden um bei Teildefekten in diesem Bereich die Dies noch verwerten zu können, oder man verwurstet sie dann in TR 3000, sofern dort Modelle mit weniger als 8 RAM Channels und 128 PCIe Lanes erscheinen.Im für Intel billigen, weil durch lange Erfahrung sehr hohe Ausbeute alt Prozess von 14+++++++++++++++ oder wie viele Plus auch immer...

2/3 der Kosten entfallen dann auf die Chiplets, sofern deren Kosten pro mm² eben doppelt so hoch sind wie die für das I/O Die. Und da die Kosten von Intel 14nm Prozess wohl eher mit denen von GFs 12/14nm zu vergleichen sind als denen von TSMCs 7nm, liegen die reinen Herstellungskosten für ein XCC mit seinen 700mm² damit noch unter denen für ein Rome mit 4 Chiplets, denn bei doppelten Kosten für 7nm, muss man kostenmäßig die Größe pro Chiplet ja mit 150mm² und nicht nur mit 75mm² ansetzen.Und im Verhältnis sogar noch mehr, wenn da eben kein 64C Rome bei raus kommt - bei 32C und vier Chiplets sinds ~430mm² für den IO DIE + ~300mm² für die Chiplets. Halbe Kosten beim IO DIE auf den mm² macht also schon 2/3tel der Kosten.

Eben, ich denke schon das Intel seine Xeons günstiger fertigt als AMD seine TR und Rome fertigen wird. Außerdem sind die reinen Fertigungskosten nur ein Teil der Kosten, die Entwicklungskosten sind auch nicht zu verachten, vom Design bis hin zu den Masken für die Fertigung, bis alles final läuft. Dazu die Validierungen und diese ganzen Kosten muss man dann eben durch die Anzahl der verkauften Chips teilen (die teuren Modelle müssten mehr dazu beitragen als die Einstiegmodelle, aber so eine Mischkalkulation sollte jedem bekannt sein) und da dürfte Intel mit seinen hohen Marktanteile in den meisten x86 Segmenten klar im Vorteil sein, auch wenn man mehr unterschiedliche Modelle hat als AMD.So naiv hier von "günstiger" als Intel zu philosophieren, schaffen auch nur die treuen Anhänger der Marketingfolien. Einfach mal Hirn einschalten würde dabei schon helfen. Ganz ohne Zahlen sind das logische Schlussfolgerungen mit nur einer einzigen Annahme, die nicht belastbar ist -> Intel kann 14nm mindestens genau so günstig produzieren wie AMD ihren IO DIE bei gleicher Fläche kosten wird. Wäre Intel hier sogar noch ne Ecke günstiger

Eben, sie haben aus der Not eine Tugend gemacht, denn man hätte es sich gar nicht leisten können so viele Bereiche mit eigenen Designs abzudecken, gerade bei den Server CPUs wäre es bei dem minimalen Marktanteil den AMDs vor Erscheinen der ersten EPYC noch hatte, ein enormes Risiko gewesen die hohen Kosten für große eigene Dies für die Server CPUs zu stemmen.Ach und bevor es kommt, für AMD ist das ganze trotzdem stimmig. Denn ihre Chiplet Strategie sorgt dafür, dass sie einen viel größeren Marktbereich mit ein und der selben Fertigung abdecken können.

So ist es und wir werden ja sehen wie die nächste APU Generation aussehen wird, ob diese dann mit I/O Chip und einem CPU und einem GPU Chiplet kommen oder wieder als ein eigens monolithisches Die mit allem drauf. Ich tippe auf letzteres, einfach weil die Kosten dafür viel geringer sind und die APUs inzwischen auch auf ausreichende Stückzahlen kommen dürften. Spätestens wenn die Aussage stimmt, dass das bisherige I/O Die für RYZEN nicht für APUs vorbereitet ist, was Sinn macht um die Fläche kleiner zu halten und Kosten zu sparen, dann wäre sowieso ein neues Die fällig, entweder ein neues I/O Die oder eben ein Die wo man gleich alles integriert und letzteres ermöglich dann hinterher eine kostengünstigere Fertigung der APUs. Dies ist wichtig, man schaue sich nur an in welchem Marktsegment die APUs positioniert sind. Und träumt nicht von einer Monster APU mit HBM, sowas macht Null Sinn, dies wäre ein Produkt für eine extrem kleine Nische. Wie klein diese Nische ist, hat man bei Kaby Lake-G gesehen, den Intel gerade erst EoL gesetzt hat.Das ist in Summe ab einem gewissen Volumen nicht die kosteneffizienteste Methode. Aber ohne dieses Volumen eben ganz sicher günstiger, als für alle Marktbereiche ne eigene Produktion hoch zu ziehen.

Heist unterm Strich, JA, die Chiplets lohnen für AMD. Aber NEIN, es ist nicht davon auszugehen, dass sie dadurch günstiger als Intel fertigen.

Eben, sie haben aus der Not eine Tugend gemacht, denn man hätte es sich gar nicht leisten können so viele Bereiche mit eigenen Designs abzudecken, gerade bei den Server CPUs wäre es bei dem minimalen Marktanteil den AMDs vor Erscheinen der ersten EPYC noch hatte, ein enormes Risiko gewesen die hohen Kosten für große eigene Dies für die Server CPUs zu stemmen.[/URL].

5 Jahre und immer noch kein Fortschritt^^ (außer bei amd)

5 Jahre und immer noch kein Fortschritt^^ (außer bei amd)