HWL News Bot

News

Thread Starter

- Mitglied seit

- 06.03.2017

- Beiträge

- 121.194

... weiterlesen

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Ja On Die ECC wird unterstützt, ist aber meines Wissens nur optional.Ich teile seine Kritik, jedoch ist der Zeitpunkt etwas unglücklich. Mit DDR5 ist das Thema ja vom Tisch, weil da laut JEDEC eh ECC und ECS unterstützt wird.

Each DIMM has two independent channels. While earlier SDRAM generations had one CA bus controlling 64 or 72 (non-ECC/ECC) data lines, each DDR5 DIMM has two CA buses controlling 32 or 40 (non-ECC/ECC) data lines each, for a total of 64 or 80 data lines.

DDR5 Datenübertragungsrate DDR4-3200 (Jedec) DDR5-6400 bis DDR5-8400 Bandbreite (theoretisch) 25,6 GByte/s pro Kanal 51,2 GByte/s bis 67,2 GByte/s pro Kanal Datenleitungen 64+8 Bit mit ECC 2x 32+8 Bit mit ECC Fehlerkorrekter Off-Die-ECC On-Die-ECC (optional) SDRAM-Die-Kapazität bis zu 16 GBit (DUV) bis zu 64 GBit (EUV) DIMM-Kapazität (Desktop) bis zu 32 GByte bis zu 128 GByte DIMM-Kapazität (Server) bis zu 256 GByte bis zu 1 TByte Prefetching 8n 16n Speicherbänke 4 Gruppen mit 4 Bänken 8 Gruppen mit 4 Bänken Auffrischung All Bank Refresh (REFab) Same Bank Refresh (REFsb) Burst Length 8 16 Spannung (VDD/VPP) 1,2 Volt / 2,5 Volt 1,1 Volt / 1,8 Volt

On-Die-ECC, jeder RAM hat im Inneren 6,25 % zusätzliche RAM-Zellen, um Fehler auch bei Nicht-ECC-RAM zu erkennen und zu korrigieren. Dieser Test kann periodisch und unabhängig von der CPU ausgeführt werden.

Ich hatte immer im Hinterkopf, dass es in jedem Fall für DDR5 verwendet wird und nicht optional ist. Aber ich lese immer wieder "optional" in den Berichten zu DDR5. Aber: Wenn es auf dem Die für DDR5 ist, es also keinen separater Chip wie bei DDR4 gibt, dann ist es nicht optional. Alles deutet darauf hin, dass in DDR5 das ECC immer mit eingebaut ist.

Ist das so?afaik geht ja ECC nur bei den i5 und i7 nicht (bzw. teils i3) die Pentium und Celerons bzw. je nach gen auch i3 können ja ECC wenn es das MB und der Chipsatz kann - zum Thema Xeon only.

Ein Beispiellink: https://www.overclock3d.net/news/me...ynix_spills_the_beans_on_its_ddr5_dram_tech/1@pescA Hast du dazu weiteren Input? Zuminest bei Wiki findet man dazu leider nix.

Unlike DDR4, ECC (Error Correcting Code) and error check and scrub (ECS) are part of the DDR5 standard. No longer will these features be limited to specialised processors and memory modules.

Linus ist halt auch ne Laberbacke. Stark fördern tut AMD den ECC im Mainstream natürlich auch nicht(Threadmonster abseits der Threadripperplattform), er wird einfach optional gehalten weil man ohne ihn schneller ist und keinen Support gewähren muss.

Ich glaube Intel selbst hat sogar bei den Xeons keine double-bit error correction Methode oder ?, das hatte nur der Bulldozer 🤪.

Die Argumentation seitens Intel ist einfach das dies so selten vor kommt(Fehler) das es preislich einfach nicht lohnt das abseits der Hamming Variante zu machen, also sich derart zu verteuern und zu verlangsamen. Und da Intel evtl. zu unfähig und trotzdem sehr stark verbreitet ist bei den Xeons blockiert man halt den Weg für Neues, absichtlich oder versehentlich.

Ich geh wie Don auch davon aus das der DDR-5 die allermeisten Module mit on-die ECC bekommen werden die kaum bis gar keine Performance kostet, evlt. abschaltbar halte das standardmäßig allerdings für eine gute Idee. Ich denke wer anfängt blickende Module zu konsumieren sollte mit etwas "Puffer" für Sicherheit und Stabilität leben können.

, bzw. den Pöbel zu kastrieren

, bzw. den Pöbel zu kastrieren  , irgendwie muss aber auch die ganze Forschung und die Börse geldmäßig überbespaßt werden.

, irgendwie muss aber auch die ganze Forschung und die Börse geldmäßig überbespaßt werden.

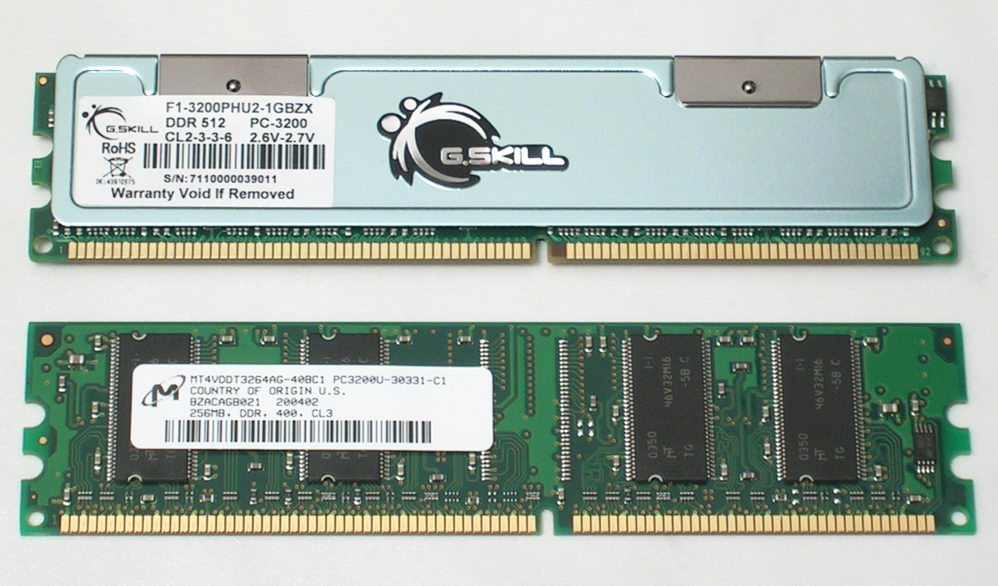

Buffered und Registered RAM sind aber zwei verschiedene Methoden........Was vielleicht auch noch interessant ist, ECC gibt es als unbuffered und als Buffered (Registered) ECC Module.

Das hat den Hintergrund, dass Server mehr Speicher Module bestücken können, um da den IMC zu entlasten werden Verstärker Bausteine Verbaut.

Die Verstärker erzeugen eine höhere Latenz bei den RAM Zugriffen.

Unbuffered hat keine Verstärker nur einen Zusätzlichen Speicher Chip pro Rank, daher ist die Latenz mit unbuffered ECC deutlich niedriger als Reg-ECC.

Sehe ich auch so, zumal es ja noch die kleinen Xeon E3 (mittlerweile nur E?)auf Core Basis gibt. Die sind auch für Privat bezahlbar.Ich verstehe ehrlich gesagt das Problem nicht

Das kann sein, so weit bin ich nicht zurück gegangen in die Vergangenheit.Buffered und Registered RAM sind aber zwei verschiedene Methoden........

Der Begriff wird oft fälschlicherweise synonym mit der Vorgängertechnik Buffered Module („gepuffertes Modul“) verwendet, da beide ähnliche Ziele verfolgen.

Bei ECC Registrered RAM hat man Latenzen von CL 7 bis 9 bei DDR3-1333 zum Beispiel. Sind also recht niedrig.Das kann sein, so weit bin ich nicht zurück gegangen in die Vergangenheit.

Wichtig ist nur, das die Ryzen unbuffered ECC nutzen und damit kaum Nachteile bei der RAM Latenz haben.

Bei den Threadripper wird es sogar offiziell Unterstützt.

Das ist die Zeit die die Speicherzellen benötigen, das ist nicht die Latenz die der IMC braucht bis er die Daten fertig gelesen und geschrieben hat.Bei ECC Registrered RAM hat man Latenzen von CL 7 bis 9 bei DDR3-1333 zum Beispiel. Sind also recht niedrig.

Wie das bei FB-Dimms aussieht weiß ich nicht.

Die nutzen aber nur Single-Bit ECC, das ist ja was Linus beanstanded:Sehe ich auch so, zumal es ja noch die kleinen Xeon E3 (mittlerweile nur E?)auf Core Basis gibt. Die sind auch für Privat bezahlbar.