Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

AMD zeigt Ryzen-Prozessor mit gestapeltem 3D V-Cache

- Ersteller HWL News Bot

- Erstellt am

Shevchen

Urgestein

- Mitglied seit

- 20.01.2011

- Beiträge

- 2.955

- Desktop System

- Rotkäppchen

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X @4.7GHz allcore

- Mainboard

- Asus X570 Crosshair VIII Impact

- Kühler

- Custom Wasserkühler 4x480

- Speicher

- 32GB (2x16) G.Skill Samsung B-Die @3800 CL14

- Grafikprozessor

- AMD Radeon 5700XT 50th Anniversary edition

- Display

- LG 38GN950-B

- SSD

- 2x2TB Samsung 970 Evo Plus

- Soundkarte

- RME ADI-2 pro FS

- Gehäuse

- Corsair 1000D

- Netzteil

- Corsair AX1600i

- Keyboard

- Das Keyboard 5Q

- Mouse

- Logitech G502

- Betriebssystem

- Win10 pro/Arch Linux

Da dieser Chip die erste Gen einer neuen Technik ist, kannst du wohl ruhigen Gewissens den tatsächlichen AM5 Sockel mit DDR5 und der entsprechenden CPU abwarten. AM4 ist ein dead-end und nur Leute, die jetzt noch auf Zen 2 hocken mag das kitzeln. Spiele sind auch mit Zen 3 weiterhin größtenteils GPU limitiert und bevor du den Vorteil des Caches merkst, musst du schon ne 3090/6900XTH in deiner Kiste haben - und selbst da darfst du dann nicht auf 4k spielen.Zen3+ war in den letzten Monaten und Wochen eher als Startschuss für AM5 mit DDR5 für Herbst/Winter 2021 vermutet worden, soweit ich das mitbekommen habe, und davor immer mal wieder totgesagt bzw. nur sehr vage existent.

Beitrag automatisch zusammengeführt:

Da könntest du dem Chip dann zukucken, wie er aus dem Sockel springt. So ein Chip mit... ach machen wir es einfach: Mit 2,6cm Breite würde er dann um 1cm "wachsen" bei 1 Kelvin höherer Temperatur. Macht dann bei einem Delta von 80°K von Zimmertemperatur bis edge dann 80cm Breitenzuwachs. Das Ding wäre dann größer als dein Mainboard.@smalM

Würde rin ausdehnungskoeffizient von 2.6 bedeuten dass 1nm auf 2.6nm sich ausdehnt?

Beitrag automatisch zusammengeführt:

Heist das dieser refresh bekommt massiven cache noch vor zen4?

smalM

Enthusiast

Für Dich noch einmal ausgeschrieben:Würde rin ausdehnungskoeffizient von 2.6 bedeuten dass 1nm auf 2.6nm sich ausdehnt?

Ein Die von 1 Millimeter Höhe hat eine Höhenausdehnung von 2,6 Nanometer pro ein Kelvin Temperaturerhöhung.

D.h. die Die-Höhe beträgt nach der Erhöhung der Temperatur um ein Kelvin 1,0000026 Millimeter.

Bitmaschine

Urgestein

- Mitglied seit

- 01.03.2013

- Beiträge

- 2.452

Das gefällt mich auch sehr. Vor allem in Bezug auf Effizienz und Verbrauch der CPU Architektur im Detail ist AMD recht innovativ und sie lassen auch nicht locker. Intelligentes Caching bringt doch was, als die Taktfrequenz nach oben zu prügeln, was dann mehr Verbrauch und Abwärme bedingt. Ich hoffe das Stacking wird sich bewähren, weil es wahnsinnig viel Möglichkeiten zulässt, wie auch das Chipletdesign. Beides in Kombination hat Potenzial. 😜Wow, richtig beeindruckend was AMD immer wieder vorlegt. Sowohl bei den GPUs wie auch bei den CPUs.

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.705

Update in der News: https://www.hardwareluxx.de/index.p...zessor-mit-gestapeltem-3d-v-cache-update.html

AMD hat uns einige Fragen beantwortet.

AMD hat uns einige Fragen beantwortet.

Danke ^^Für Dich noch einmal ausgeschrieben:

Ein Die von 1 Millimeter Höhe hat eine Höhenausdehnung von 2,6 Nanometer pro ein Kelvin Temperaturerhöhung.

D.h. die Die-Höhe beträgt nach der Erhöhung der Temperatur um ein Kelvin 1,0000026 Millimeter.

Holzmann

The Saint

- Mitglied seit

- 02.05.2017

- Beiträge

- 43.591

- Desktop System

- The Behemoth

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen™ 9 9950X3D

- Mainboard

- ASUS ROG Crosshair x870e Hero

- Kühler

- CPU: ALC Core One Light

- Speicher

- GSkill 32GB 6000er CL26 1.4v expo @8200 CL34

- Grafikprozessor

- ASUS ROG Astral LC RTX 5090 OC Edition

- Display

- ASUS ROG Swift OLED PG34WCDM

- SSD

- Samsung 9100 pro 1TB System / Samsung 990 evo plus 2TB Daten

- Soundkarte

- Sound Blaster X5 / Beyerdynamic MMX 330 PRO

- Gehäuse

- Corsair 7000D

- Netzteil

- ASUS ROG Strix 1200 W Platinum ATX3.1

- Keyboard

- ASUS ROG Azoth

- Mouse

- ASUS ROG Spatha X on ASUS ROG Balteus

- Betriebssystem

- Win11 pro

- Sonstiges

- MO-RA3 420 LT White / D5 Next / Thrustmaster T 818 Base

Ist bekannt wo AMD das Cache-Die fertigen lässt?

Welcher Prozess?

Welcher Prozess?

Chaund

Experte

- Mitglied seit

- 01.06.2016

- Beiträge

- 566

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7700X

- Mainboard

- MSI MEG X670E ACE

- Kühler

- Heatkiller IV @Custom Loop (3x 420 Mo-Ra3)

- Speicher

- 32GiB G.Skill Trident Z5 NEO (DDR5-6000, CL30-38-38-96)

- Grafikprozessor

- Gigabyte GeForce RTX 4090 Gaming OC

- Display

- LG OLED42C27LA

- SSD

- Samsung 980 Pro 1TB / Samsung PM9A1 2TB / Samsung 970 Evo Plus 2TB u.a.

- Gehäuse

- Lian Li O11D XL

- Netzteil

- be quiet! Straight Power 11 850W Platinum

- Keyboard

- Razer Tartarus Pro / Razer Pro Type

- Mouse

- Razer Naga Pro

- Betriebssystem

- Windows 11

- Webbrowser

- Mozilla Firefox

- Sonstiges

- nubert nuPro SP-200 / nubert nuSub XW-700

- Internet

- ▼250 MBit ▲50 MBit

7nm TSMC.

Bitmaschine

Urgestein

- Mitglied seit

- 01.03.2013

- Beiträge

- 2.452

Hört sich nicht schlecht an.Update in der News: https://www.hardwareluxx.de/index.p...zessor-mit-gestapeltem-3d-v-cache-update.html

AMD hat uns einige Fragen beantwortet.

Holt

Legende

- Mitglied seit

- 05.07.2010

- Beiträge

- 30.436

Dies wurde mit dem Update der News ja nun beantwortet.- Das aufsitzende Cache-Die ist gar nicht nur ein einzelnes Die, sondern ein Stapel.

Ja, wobei dies offenbar nur für die Versionen der Prozesse zutrifft, bei denen SRAM und Logik gemischt sind, denn hier soll ja auch ein N7 Prozess verwendet werden, der aber bei SRAM mehr Transistoren auf der Fläche unterbringen kann. Aber durch die neuen Verbindungstechnologien dürfte die Tendenz für die Zukunft sein, dass man noch mehr einzelne Dies verwendet die jeweils unterschiedlich gefertigt werden, je nachdem welches Prozess dafür das beste Ergebnis bringt, ggf. bei unkritischen Dingen auch am preiswertesten ist und dies dann zu einem Prozessor verbindet. Die Rechenaufgabe für die Produktplaner wird sicher um einiges komplexer werden als früher, da ja auch die Verbindungstechnik Geld kostet.Es würde mich nicht wundern, wenn das Cache-Die in N6 produziert würde und der Zen4-CCD in N5 gar keine eigenen SRAM-Bänke im L3 mehr besäße; dort befänden sich dann nur noch Logic und Tags.

smalM

Enthusiast

Holt

Legende

- Mitglied seit

- 05.07.2010

- Beiträge

- 30.436

So heftig ist die Zunahme gar nicht, dies hatte ich gerade in einem Video gesehen und die Zahlen sollten von 2018 sein:wegen der heftigen Zunahme der Waferpreise je Node-Generation

Natürlich hängen die Preise von vielen Faktoren ab, aber am Ende ist der Preis pro Transistor die entscheidende Größe, aber natürlich spielen auch der Zeitraum und Volumen der Lieferungen eine Rolle.

Wieso unterschiedliche Wege? Intel macht mit EMIB und Foveros nichts anderes und hat dies schon bei Lakefield eingesetzt und auch bei 3D NAND ist Stacking schon lange üblich. Die kochen da also alle mit dem gleichen Wasser.welch unterschiedlichen Wege die Firmen einschlagen

smalM

Enthusiast

@Holt

Ich kenne die Darstellung und fand sie seltsam.

Ich kenne auch diese hier:

Und das sind Waferpreise für den Großkunden Apple.

Unterschiedliche Wege: Ich meinte nicht das Packaging an sich, sondern die Konzepte, was auf separate Dies ausgelagert werden wird und was nicht.

Die-Shot von Fritzchens Fritz mit Annotationen von redit-User Locuza (Original hier)

Die hinzu gefügte Umrahmung zeigt die Lage und Größe des aufgesetzten Cache-Dies nach Vorlage von AMDs Schema.

Alleine der SRAM der L3-Speicherbänke macht etwas mehr als die Hälfte dieser umrahmten Fläche aus.

Die grün eingezeichneten Strukturen könnten die Kontaktstellen für die Vias sein, im Zen2-L3 sind sie jedenfalls noch nicht vorhanden.

Ich kenne die Darstellung und fand sie seltsam.

Ich kenne auch diese hier:

Und das sind Waferpreise für den Großkunden Apple.

Unterschiedliche Wege: Ich meinte nicht das Packaging an sich, sondern die Konzepte, was auf separate Dies ausgelagert werden wird und was nicht.

Beitrag automatisch zusammengeführt:

Die-Shot von Fritzchens Fritz mit Annotationen von redit-User Locuza (Original hier)

Die hinzu gefügte Umrahmung zeigt die Lage und Größe des aufgesetzten Cache-Dies nach Vorlage von AMDs Schema.

Alleine der SRAM der L3-Speicherbänke macht etwas mehr als die Hälfte dieser umrahmten Fläche aus.

Die grün eingezeichneten Strukturen könnten die Kontaktstellen für die Vias sein, im Zen2-L3 sind sie jedenfalls noch nicht vorhanden.

Zuletzt bearbeitet:

Man munkelt ja schon das AMD im neuesten Zen3 Stepping B2 und sogar im ersten Stepping die VIAs mit drin hatte... Nur das es kein Mensch bemerkt hat. Da muss man einfach mal sagen: Hut ab, das das nicht durchgesickert ist. Denke Intel bekommt gerade richtig kalte Füße, weil AMD nun schon wieder Vorreiter ist was die Cpus im Desktop angeht

Aber mal gucken was AMD letztendlich an Cpus bringt. Eventuell kommen ja welche mit extra Cache und ein paar ohne.

Aber mal gucken was AMD letztendlich an Cpus bringt. Eventuell kommen ja welche mit extra Cache und ein paar ohne.

tgh1978

Enthusiast

- Mitglied seit

- 19.12.2010

- Beiträge

- 259

- Details zu meinem Desktop

- Prozessor

- Intel Core i9-12900K

- Mainboard

- Gigabyte Z690M Aorus Elite AX

- Kühler

- Be quiet! Dark Rock TF 2

- Speicher

- 4x 16GB DDR4-4600 CL18 Corsair Vengeance

- Grafikprozessor

- ASUS TUF Gaming GeForce RTX 3060 Ti OC

- Display

- AOC Agon AG272FCX

- SSD

- WD Red SN700 4TB + 2x SanDisk Ultra 3D 4TB in Raid 0

- HDD

- 3x Seagate SkyHawk AI 12TB in Raid 0 + 1x WD Red SN700 500GB als Cache

- Opt. Laufwerk

- Panasonic UJ-267 BDXL-RW

- Gehäuse

- Chieftec Mesh CI-02B

- Netzteil

- Fractal Design Ion+2 860P

Jetzt bin ich noch mehr froh, dass ich zum Start von Zen 3 erst überhaupt keinen Ryzen 9 5950X bekommen habe, und danach dann nur zu Mondpreisen, und somit zugeschlagen habe, als ich bei Ebay UK eine neue Ryzen 9 3950X für ca. EUR 520,- gesehen habe...

Ich werde warten bis Zen 4 startet und mir dann (hoffentlich) günstig eine Zen 3+ holen, das scheint ja dann nochmals ein besserer Sprung zu werden als wenn ich "nur" von Zen 2 auf Zen 3 aufrüsten würde...

Und ich gehe mal fix davon aus das Gigabyte beim B550I Aorus Pro AX sicher dann ein UEFI-Update rausbringen wird, welches Zen 3+ auch noch unterstützt...

Ich werde warten bis Zen 4 startet und mir dann (hoffentlich) günstig eine Zen 3+ holen, das scheint ja dann nochmals ein besserer Sprung zu werden als wenn ich "nur" von Zen 2 auf Zen 3 aufrüsten würde...

Und ich gehe mal fix davon aus das Gigabyte beim B550I Aorus Pro AX sicher dann ein UEFI-Update rausbringen wird, welches Zen 3+ auch noch unterstützt...

MSAB

Urgestein

Kann man da dann ähnliche Leistungssteigerungen wie beim Intel 5775C erwarten? Dieser ist ja auh heute noch schnell.

Holt

Legende

- Mitglied seit

- 05.07.2010

- Beiträge

- 30.436

Oder sagen wir besser, die sollten die Waferpreise für den Großkunden Apple sein, denn ich glaube kaum, dass TSMC oder Apple diese veröffentlichen. Außerdem ist auch die Frage, von wann sie sein soll, bei der derzeitigen Knappheit dürften die Preise für neue Verträge sicher höher ausfallen als noch vor einem Jahr.Und das sind Waferpreise für den Großkunden Apple.

Wieso sollte Intel kalte Füsse bekommen? Die können dies auch, Intel hat die Technologie zum Durchkontaktieren schon lange bei seinen NANDs im Einsatz, tatsächlich sind Intel neue 144 Layer NANDs die ersten bei denen drei Die gestackt sind.Denke Intel bekommt gerade richtig kalte Füße

Der 5775C ist auch nur bei einigen Anwendungen schnell, während andere von dem eDRAM wenig profitieren. Außerdem haben größere Caches und auch ein zusätzlicher L4 Cache wie das eDRAM auch den Nachteil, dass die Latenz steigt, weil die Verwaltung aufwendiger ist, es dauert eben in aller Regel länger in einen großen Cache die Daten zu finden oder festzustellen das sie da nicht drin sind, wie in einem kleinen Cache.Kann man da dann ähnliche Leistungssteigerungen wie beim Intel 5775C erwarten? Dieser ist ja auh heute noch schnell.

- Mitglied seit

- 13.07.2010

- Beiträge

- 5.025

- Details zu meinem Desktop

- Prozessor

- r9 5900x B2 (CO -20, -15, -10, -5, 0, 5 je nach Core)

- Mainboard

- MSI MPG Gaming Plus x570

- Kühler

- Thermalright Macho Rev. B

- Speicher

- g.skill Trident Z (leider RGB) DDR4-3600 (CL16-16-16-36)

- Grafikprozessor

- Powercolor 6900XT (Referenzdesign) mit Eiswolf 2

- Display

- 35" LG UWQHD, HDR, Freesync, 100Hz

- SSD

- 3x Samsung (2x 860 EVO,1x 850 EVO) 1x Seagate (Firecuda 530 NVMe) 1x SK hynix (P41 NVMe)

- HDD

- 1x Western Digital green, 2x Seagate Ironwolf Pro

- Soundkarte

- ASUS Xonar DX

- Gehäuse

- PHANTEKS Enthoo Pro 2

- Netzteil

- BeQuiet! Pure Power 12 M 1000 W

Ich freue mich drauf.

Wahrscheinlich werde ich dem alten Board hier dann nen neuen Tower und dem System ne gute Kühlung spendieren, sofern ein brauchbarer Ersatz für meine CPU aufschlägt.

Wahrscheinlich werde ich dem alten Board hier dann nen neuen Tower und dem System ne gute Kühlung spendieren, sofern ein brauchbarer Ersatz für meine CPU aufschlägt.

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.705

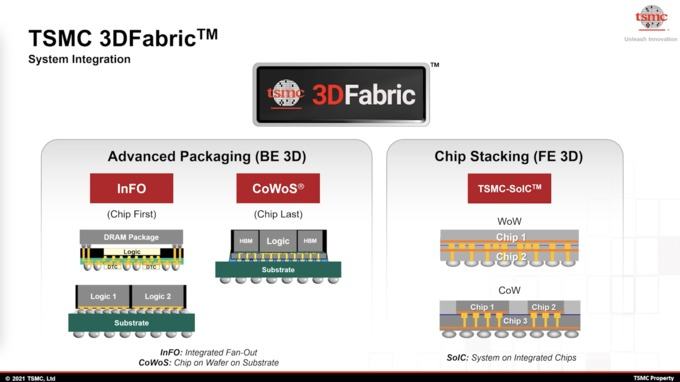

TSMC-SoIC als Zukunftstreiber: Die Technik hinter AMDs 3D V-Cache - Hardwareluxx

TSMC-SoIC als Zukunftstreiber: Die Technik hinter AMDs 3D V-Cache.

Niftu Cal

Enthusiast

- Mitglied seit

- 02.12.2018

- Beiträge

- 4.970

Immer nett sowas, denn ein neuer Release drückt die Preise der alten CPUs meistens. Für 300 € würde ich mir glatt einen 5800X neu kaufen, leider sind die Zeiten vorbei. Ich tendiere aber ohnehin stark zum 3900X, da die FPS in 4K immer identisch sind laut Youtube. Ich bereue es bis heute damals auf Zen+ gesetzt zu haben, hätte ich mal ein Jahr mehr gewartet, denn die CPUs waren neu noch sehr günstig, ~300 für den Achtkerner bei Launch war normal. Jetzt sehe ich es einfach nicht ein das für ein auslaufendes Produkt hinzulegen.

Für 1080p-Spieler könnte gerade ein Sechskerner mit dem neuen Cache interessant sein, sofern der auch noch kommt. Nochmal 15 - 20 % FPS lassen Intel dann vermutlich alt aussehen.

Für 1080p-Spieler könnte gerade ein Sechskerner mit dem neuen Cache interessant sein, sofern der auch noch kommt. Nochmal 15 - 20 % FPS lassen Intel dann vermutlich alt aussehen.

Holzmann

The Saint

- Mitglied seit

- 02.05.2017

- Beiträge

- 43.591

- Desktop System

- The Behemoth

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen™ 9 9950X3D

- Mainboard

- ASUS ROG Crosshair x870e Hero

- Kühler

- CPU: ALC Core One Light

- Speicher

- GSkill 32GB 6000er CL26 1.4v expo @8200 CL34

- Grafikprozessor

- ASUS ROG Astral LC RTX 5090 OC Edition

- Display

- ASUS ROG Swift OLED PG34WCDM

- SSD

- Samsung 9100 pro 1TB System / Samsung 990 evo plus 2TB Daten

- Soundkarte

- Sound Blaster X5 / Beyerdynamic MMX 330 PRO

- Gehäuse

- Corsair 7000D

- Netzteil

- ASUS ROG Strix 1200 W Platinum ATX3.1

- Keyboard

- ASUS ROG Azoth

- Mouse

- ASUS ROG Spatha X on ASUS ROG Balteus

- Betriebssystem

- Win11 pro

- Sonstiges

- MO-RA3 420 LT White / D5 Next / Thrustmaster T 818 Base

V-Cache wohl doch später als gedacht:

www.3dcenter.org

www.3dcenter.org

Hardware- und Nachrichten-Links des 2. Juni 2021 | 3DCenter.org

Laut Twitterer Vegeta tritt der Zen-3-Refresh erst im ersten Quartal 2022 an, war also AMDs Aussage zur Vorstellung von "3D V-Cache" etwas zu optimistisch angelegt. Die im Tweet getroffenen Namenswahl "Zen 3 XT" deutet möglicherweise

n3cron

Enthusiast

- Mitglied seit

- 13.05.2020

- Beiträge

- 6.538

- Ort

- DE - BY - MILF

- Details zu meinem Desktop

- Prozessor

- Intel Core i7 13700K 16 (8+8) 3.40GHz So.1700

- Mainboard

- MSI Tomahawk WIFI Intel Z790 So. 1700

- Kühler

- be quiet! Silent Loop 2 360mm All-in-One

- Speicher

- 64GB (2x 32GB) G.Skill Ripjaws S5 weiss DDR5-5600 DIMM CL28

- Grafikprozessor

- Gigabyte Nvidia RTX 3080 Gaming OC 10G

- Display

- Xiaomi Mi Curved Gaming Monitor 34" 144hz@ UWQHD 3440*1440

- SSD

- Samsung 990Pro 2 TB, Samsung 970 Evo Plus M.2 2280 PCIe 3.0 x4 3D-NAND TLC

- Opt. Laufwerk

- -

- Soundkarte

- -

- Gehäuse

- be quiet! Silent Base 802

- Netzteil

- 750 Watt be quiet! Dark Power 13 Modular 80+ Titanium

- Betriebssystem

- Windows 11 Pro

- Internet

- ▼950 Mbit ▲600 Mbit

Wahrlich interessante Neuigkeiten!

Anders als man vor 1 Jahr gedacht hätte das wir uns langsam der technischen Grenzen näheren des machbaren, kommt im wahrsten Sinne noch was oben drauf ! ;-)

Mich würde an der Stelle interessieren, ob es technisch machbar wäre anstelle eines zweiten CCX z. b 1 CCX mit 8 Kernen und L3 Cach und CCX 2 mit IGPU + HBM Speicher im 3D-Stack auszustatten für APUs?

Für Notebooks wäre das natürlich ziemlich geil wenn das ginge, nicht nur bezüglich Strom verbrauch sondern das spart ja an allem unter anderen Platz und würde die Performance explodieren lassen. So wie ich das in etwa mitbekommen habe all die Jahre ist bei den APUs immer das Problem die miese Speicher Anbindung die quasi ein Limit setzt.

Anders als man vor 1 Jahr gedacht hätte das wir uns langsam der technischen Grenzen näheren des machbaren, kommt im wahrsten Sinne noch was oben drauf ! ;-)

Mich würde an der Stelle interessieren, ob es technisch machbar wäre anstelle eines zweiten CCX z. b 1 CCX mit 8 Kernen und L3 Cach und CCX 2 mit IGPU + HBM Speicher im 3D-Stack auszustatten für APUs?

Für Notebooks wäre das natürlich ziemlich geil wenn das ginge, nicht nur bezüglich Strom verbrauch sondern das spart ja an allem unter anderen Platz und würde die Performance explodieren lassen. So wie ich das in etwa mitbekommen habe all die Jahre ist bei den APUs immer das Problem die miese Speicher Anbindung die quasi ein Limit setzt.

Holt

Legende

- Mitglied seit

- 05.07.2010

- Beiträge

- 30.436

Die Grenzen des technisch Nachbaren verschieben sich immer!Anders als man vor 1 Jahr gedacht hätte das wir uns langsam der technischen Grenzen näheren des machbaren

Acki-84

Profi

- Mitglied seit

- 25.01.2021

- Beiträge

- 284

- Desktop System

- Ryzen 5950x

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5950X

- Mainboard

- MSI X570 Tomahawk

- Kühler

- Noctua NH-D14

- Speicher

- 64GB Patriot 3600 MHz

- Grafikprozessor

- MSI RTX 3080 Suprim X

- Display

- LG 32GK850G

- SSD

- Samsung 970 Pro 512GB

- HDD

- Seagate ST2000VX 2TB

- Gehäuse

- Phanteks P400

- Netzteil

- Corsair RMX750

- Betriebssystem

- Win 10 64 Bit

- Internet

- ▼1000 ▲50

Wie sich alle ihre Investition in "langsamere" und "ältere" Ryzen CPUs schön reden.

Ich hab nen 5950x gekauft im Dezember und habe damit keine Probleme - wieso? Weil die neuen Dinger nicht billiger werden und die Verfügbarkeit noch mieser wird..

Die Features kann ich nur vermuten wo und wann ich diese spüren werden. Da jetzt 2 Jahre warten bis ich die vielleicht doch nicht brauche und ne langsame CPU nutzen? Nö...

Ich hab nen 5950x gekauft im Dezember und habe damit keine Probleme - wieso? Weil die neuen Dinger nicht billiger werden und die Verfügbarkeit noch mieser wird..

Die Features kann ich nur vermuten wo und wann ich diese spüren werden. Da jetzt 2 Jahre warten bis ich die vielleicht doch nicht brauche und ne langsame CPU nutzen? Nö...

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.705

Update in der News: https://www.hardwareluxx.de/index.p...ssor-mit-gestapeltem-3d-v-cache-2-update.html

Im Rahmen einer Episode der YouTube-Serie "The Bring Up" hat AMD einige weitere interessante Details zum 3D V-Cache verraten.

So wird der CCD um 180 ° gedreht und 95 % des Chips werden abgeschliffen. Am Ende bleiben nur noch 20 µm des ansonsten 400 µm dicken Chips als aktives Silizium übrig. Auf diese dünne Schicht wird dann der 3D V-Cache gestapelt. TSVs aus Kupfer stellen bekanntermaßen die Verbindung zwischen dem CCD und SRAM her. Laut AMD reicht die Adhäsion der Kupfer-Kontaktpunkte der TSVs auf beiden Seiten aus, um die beiden Chips miteinander zu verbinden.

Ok, das ist krass. hätte ich nicht erwartet, das die beiden Chips einfach aufeinander pappen und so halten. Schleifen auf 20um ist auch fies... Versteh ich das richtig, das AMD vorher die Schaltkreisseite unten (zum PCB) hatte und diese nun nach oben packt, dann den Sram drauf und zusätzlich unten drunter noch wegschleift?Laut AMD reicht die Adhäsion der Kupfer-Kontaktpunkte der TSVs auf beiden Seiten aus

Ähnliche Themen

- Antworten

- 2

- Aufrufe

- 684

- Antworten

- 7

- Aufrufe

- 1K

- Antworten

- 52

- Aufrufe

- 4K

- Antworten

- 10

- Aufrufe

- 2K

- Antworten

- 3

- Aufrufe

- 1K

Nicht dass ich das jetzt irgendjemandem blind empfehlen würde...

Nicht dass ich das jetzt irgendjemandem blind empfehlen würde...