Braegnok

Profi

- Mitglied seit

- 22.01.2021

- Beiträge

- 105

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 9950X

- Mainboard

- Asus ROG Crosshair X670E Gene

- Kühler

- MO-RA3 420 Pro

- Speicher

- G.SKILL F5-6000J2636G16G

- Grafikprozessor

- XFX Mercury Radeon RX 9070 XT OC

- Display

- ASUS ROG Strix OLED XG27ACDNG

- SSD

- Crucial T700

- Gehäuse

- BENCHLAB - Open Benchtable (v2)

- Netzteil

- SeaSonic Prime TX-1600

- Keyboard

- Keychron Q1 HE

- Mouse

- G502 Lightspeed

- Betriebssystem

- Windows 11 Pro 64-Bit

Those values are purposefully wrong.

It's not the real values.

ASUS does not want to share settings so everyone could copy.

Those will change, if user sets something.

You want to start with RTT_WR only, but not now.

Target is 48-60ohm for 24gb kits.

All Hynix Target 80Ohm NOM.

Why only these?

NonK OC is a microcode thing.

Unless you focus specifically on the 2nd clockgen?

IA CEP Enable [Auto]

SA CEP Enable [Auto]

Both off

ICCMAX 400A, if 13th gen 320A

VDDQ training off

Ctl0 dqvrefup [Auto]

Ctl0 dqvrefdn [Auto]

178-96

Check again if 2 & 10

First check if 3 loops y-cruncher work at all.

RTT is usually @tibcsi0407 work

But lets see~

I did not set ICCMAX 400A, there are 3 shown in bios, all are in Auto,.. IVR Transmitter VDDQ ICCMAX, Unlimited ICCMAX, and IA SoC ICCMAX Reactive Protector,.. I would be guessing it's IVR Transmitter VDDQ ICEMAX?

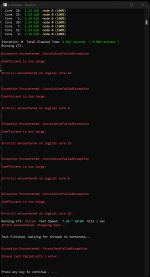

Everything else set. Y Cruncher error @ start. Checking TM5 now.