Keine Errors in den Torture tests, sowie beim Gaming,

Können sie nicht.

Clock/Voltage Gating.

% Anzahl (n Zeit) vom gehaltenen Clockstrap reduziert sich.

Ob du jetzt 80% lang den Clock hälst oder 50%,

Fällt dir auch bei 500ms Pooling nicht auf 🤭

Nu is alles in Sync und Benchmarks bestätigen den Lesistungszuwachs.

Gegenfrage,

Wie tief (positive) kannst du im CO gehen, ohne einen Leistungsverlust zu haben

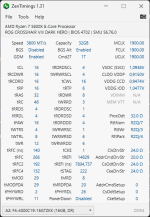

Wie verhält sich das mit den tRFC? Du sagtest ja 272 wäre ok, ich hab aber 260. Ist niedriger nicht besser? Oder weißt du das 260 mit meinen Settings definitv zu wenig ist?

Man braucht sich nicht auf World-Clock Werte zu fokusieren.

Wie zb 120,130,140ns.

RAM läuft nicht auf wold-clock. Weswegen er ein "lesbares Werte" System hat. nCK (x times amount of tCK).

Somit sollte man sich auch nicht zuu sehr auf "CL14" usw fokusieren. Virtuelle Werte ohne jegliche Bedeutung.

Die einzige wichtige Bedeutung, ist wie langsam die Transition-Delays sein müssen, damit 3-4 Timings (welche gleichzeitig geschehen) alle Korrekt überlappen.

Aka BurstLength 8 ~ 8x clock sinus-curve hoch und sinus-curve runter. BL8 wäre dann der Roundtrip delay, und der normale "ausführ-delay" heißt Burst-Chop.

BC4 . Er ist genau halb so lang. Immer.

Sprich minimum Operation delay ~ in dem Fall perfekt passend für RRD (done RAS to next RAS) aka Read to Read ~ wäre 4 clock minimum.

Die übersetzten Clock Werte, in echtzeit ns ~ wären meistens 16-17 stellige Kommazahlen,

Worin die Übersetzung zu unserer Wold-Clock in picosecounds geschieht. Und dennoch Rundungsfehler hat.

wie krass is der Sprung von diesen Settings auf 1T mit GDM On erstma?

Identisch.

Es kann langsamer sein, da wir absichtlich langsamere Settings verwenden.

Timings sind extras. Bonuse.

Wichtig wäre maximum Clock und korrektes Powering.

Das hat Priorität, den ohne korrektes Powering ~ kannst du niedrige Timings vergessen

Danach ist "alignment" wichtig. Den kein Timing gehe alleine. Niedriger ≠ Besser.

2T vs 1T

1T auf Dual Rank ist kaum möglich. Bzw nicht mehr auf high clock

Manche Boards schaffen das. Aber eigentlich braucht es eine user-korrektur durch SETUP Timings.

56 bis 63 Setup timings, ab dem 32er Wert ~ wäre von GDM nicht zu Unterscheiden.

// Setup timings zwischen 0-31 verhalten sich anders ! Ab Wert 32, ändert es seine Bedeutung.

Außer dass es unrunde Timings erlaubt und somit "potentiell hat" schneller zu sein.

Plus korrigiert nicht mehr, und rennt nicht auf "half strain".

Weswegen es den Overclocker zwingt, sein Setup korrekt einzustellen. (GDM aus)

GDM aus zu 2T, braucht kein VDIMM zuwuchs.

Gibt es Probleme, wäre es ein Powering bzw "zuu tiefe Timings" Problem

Welches nur dank GDM als "Hilfsmittel" funktionierte.

In der Realität waren die Settings jedoch inkorrekt.

Anstelle das Problem versucht zu umgehen, sollte man sich darauf fokussieren es zu lösen. 🤭

Es gibt GDM oder 2T oder 1T

GDM ist ein dynamischer Modus zwischen 2T und 1T ~ mit ein Paar extra's, welche uns OCer eher stören.