You're soo polite, thank you !

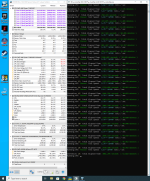

How come you remain on RCD 16 ?

Please supply those, they are actually correct. I think this time math adds up.

4-6 is a bit low.

Once you hit the right delays there, you can see a potential bandwidth bump.

Due to things ending at the right time, instead of too early.

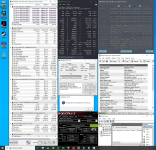

^ every timing remains loaded and supplied, even if not needed. Its inserted duration. SD, DD, SC, SC_L are all (mathematical) offset timings for synchronization.

Wouldnt bring much in reality as its just "potential" random bandwidth, but nevertheless a sign that values are on point.

For further RCD lowering trouble, you may need to start making tradeoffs. Either on RTP or on RRD/WTR.

WTR already has tradeoffs, but that's more CPU and powering focused. Same for tWR more CPU and WTR_ focused.

RRD is more dimm-pcb (well also powering) focused. PCB Trace-distance design, especially on _L's.

EDIT:

Anhang anzeigen 980692

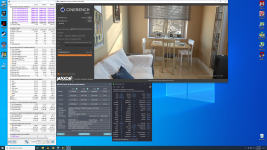

FCLK remains stable, writes add up.

30932MB/s target on 1CCD & clean OS.

Reads sit where they should. Can have more, but you meet a satisfying target.

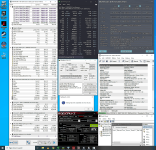

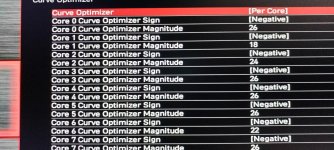

Hier meine Werte, mit den ich am besten fahre.

Hier meine Werte, mit den ich am besten fahre.