Werbung

Heute fällt der Startschuss für die zweite Generation der Xeon-Scalable-Prozessoren von Intel. Auch diese werden die Purley-Plattform verwenden, die schon mit den Skylake-SP/AP-Modellen zum Einsatz gekommen ist. Doch es gibt Änderungen in der Architektur, vor allem aber im Speicher-Ökosystem, die Cascade-Lake-Xeons in zahlreichen Bereichen besser aussehen lassen sollen. Heute schauen wir uns die Architektur als solches an, wir werden die Hardware aber ebenfalls zu einem späteren Zeitpunkt noch unter die Lupe nehmen.

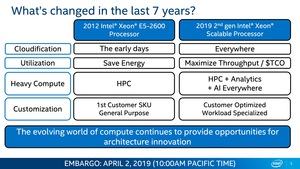

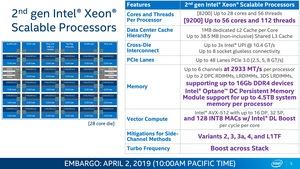

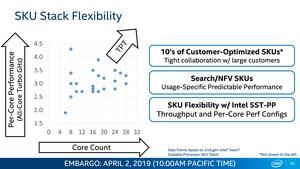

Bei Intel scheint sich die Erkenntnis durchgesetzt zu haben, dass man mit einer recht schwerfälligen zentralen CPU-Architektur nicht mehr weit kommen wird. Die Anwendungsfelder sind inzwischen derart divers, dass eine reine Auslegung auf FP64- und FP32-Rechenleistung ebenso wenig erfolgreich sein wird wie durch das reine Angebot spezieller Beschleuniger im Bereich der geringeren Rechengenauigkeit. Entsprechend bietet die Cascade-Lake-Architektur zahlreiche Änderungen, welche sie deutlich flexibler macht. Intel skaliert die flexible Architektur aber auch in Hardware in Form diverser Modelle und bietet nun eine Vielzahl an Varianten an, die sehr speziell auf eine bestimmte Anwendung ausgelegt sind.

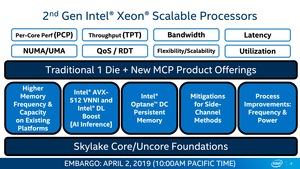

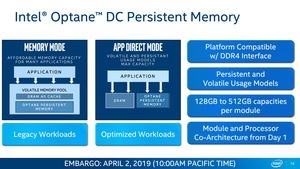

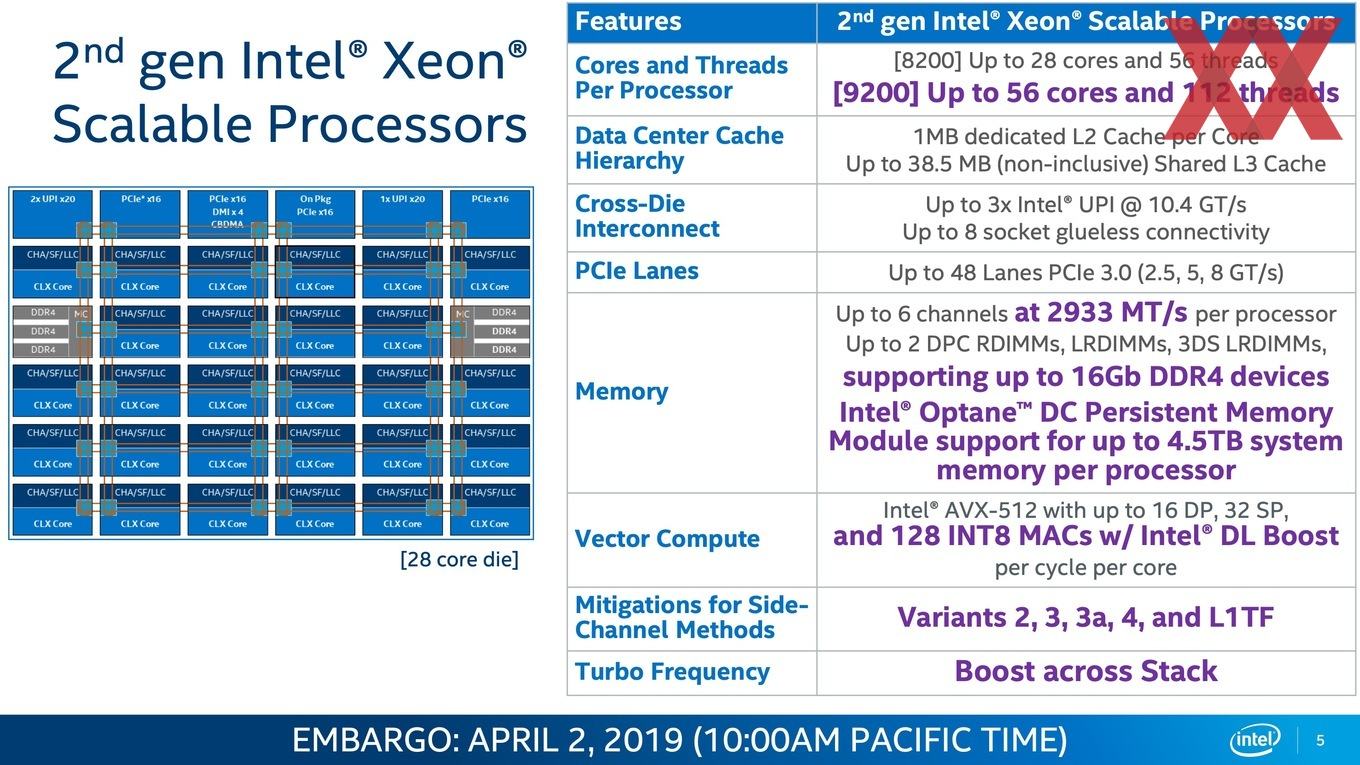

Auch wenn alle Skylake-Derivate sich nur in wenigen Details unterscheiden, so sieht Intel für den Wechsel von Skylake auf Cascade Lake zahlreiche Punkte, die eine Neuauslegung rechtfertigen. So werden die Kapazität und Geschwindigkeit des Arbeitsspeichers erhöht – dazu gehört auch die Unterstützung für den Intel Optane DC Persistent Memory. Die Änderungen der Architektur sind auf eine Beschleunigung bestimmter Befehlssätze ausgelegt. Dazu gehören die AVX-512-Instruktionen mit der Erweiterung der Vector Neural Network Instructions (VNNI) sowie die dazugehörige Softwareoptimierung, die Intel unter DL-Boost zusammenfasst. Außerdem schließt Intel mit der Cascade-Lake-Architektur die Lücke für einige Sidechannel-Attacken, die als Spectre und Meltdown noch über Jahre eine Rolle spielen werden.

Beim Aufbau und den Uncore-Bereichen des Prozessors bleibt vieles bei durch Skylake-SP etablierten Strukturen. Auf die Detailverbesserungen in der DL-Boost-Beschleunigung sowie der Unterstützung des Optane DC Persistent Memory gehen wir später noch genauer ein.

Etwas unter dem Radar laufen die Verbesserungen in der Fertigung, denn auch wenn die Cascade-Lake-Prozessoren weiterhin in 14 nm gefertigt werden, so hat Intel hier doch einige Verbesserungen einfließen lassen, die dafür sorgen, dass die Boost-Taktraten der einzelnen Modelle im Vergleich zum Vorgänger leicht ansteigen. Zwischen 200 und 300 MHz höher takten die neuen Modelle. Große Sprünge machen die Xeon-Scalable-Prozessoren der zweiten Generation damit aber sicherlich nicht.

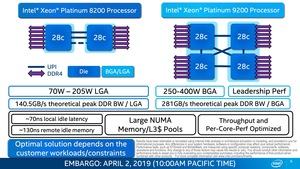

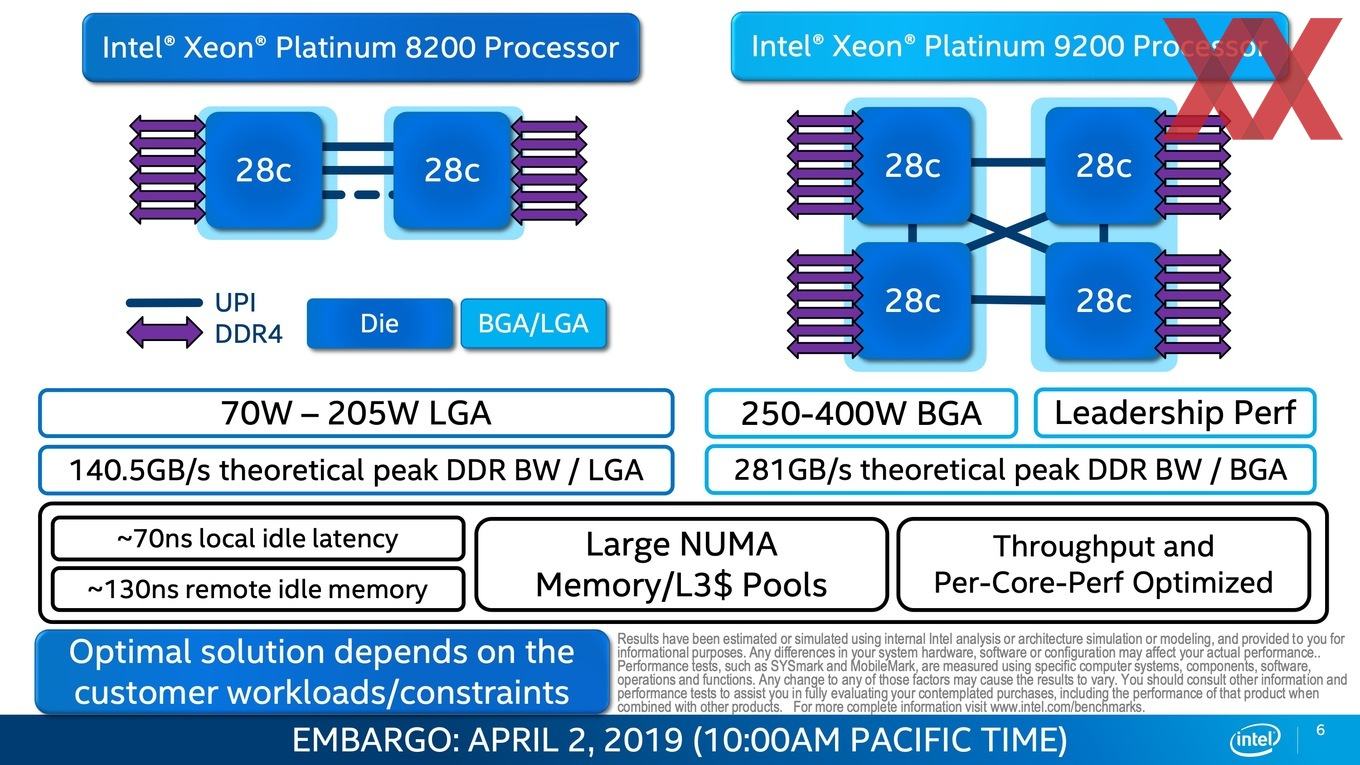

Im High-End-Segment sieht Intel eine neue 9200-Serie vor, die im Multi-Chip-Design zwei Cascade-Lake-Dies mit jeweils bis zu 28 Kernen in einem BGA-Package zusammenbringt. Damit kann Intel die Rechenleistung pro Sockel/Node deutlich steigern. Durch die Verdopplung der entsprechenden Ressourcen steigen auch die Speicherbandbreite und Interconnect-Datenraten an. Je nach Workload können solche großen NUMA-Nodes und L3-Cache-Speicherpools von Vorteil sein. Auf die Xeon-Prozessoren der 9200-Serie sind wir aber in einer gesonderten Meldung genauer eingegangen.

VNNI und DL-Boost: Flexibler durch neue Instruktionen

Bereits mehrfach hat Intel öffentlich auf die Unterstützung der neuen AVX-512-Instruktionen mit der Erweiterung der Vector Neural Network Instructions (VNNI) verwiesen. Deren Funktionsweise wird im Rahmen des öffentlichen Starts der Cascade-Lake-Prozessoren nun genauer ausgeführt.

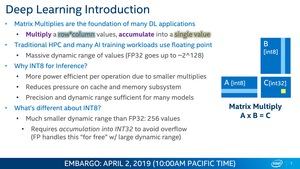

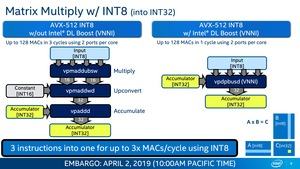

Bisher werden Matrix-Multiplikationen über Fließkomma-Operationen berechnet. Der Dynamikumfang dieser Fließkomma-Operationen (FP32 kann bis zu 2128 Werte einnehmen) wird aber im Falle einfacher Matrix-Multiplikationen nicht benötigt, also wird für DL-Boost (so der Oberbegriff für alle Hard- und Softwarebeschleunigungen in diesem Bereich) der Datentyp INT8 als Eingangsdatentyp und INT32 als Ausgangsdatentyp verwendet. Wir sprechen hier also von deutlich weniger komplexen Zahlenwerten, denn INT8 bedeutet einen Wertebereich von 28 = 256 und INT32 von 232, was immer noch deutlich weniger komplexe Zahlen als 2128 bedeutet. Die geringere Komplexität wirkt sich auch auf die Belegung im Cache und die Speicherbandbreite aus.

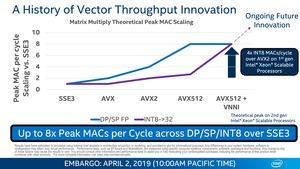

Die Rechenleistung für einfache und doppelte Genauigkeit bleibt für die AVX512-Beschleunigung im Vergleich zwischen Skylake und Cascade Lake identisch, durch die Möglichkeit 4x INT Macs/Cycle im Vergleich zu AVX2 auf Skylake-SP zu berechnen, erreichen die Cascade-Lake-Prozessoren eine theoretisch vierfach so hohe Rechenleistung für solche Berechnungen – in der Praxis sind sie bis zu dreimal schneller.

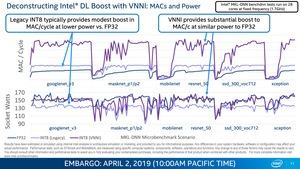

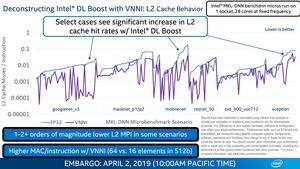

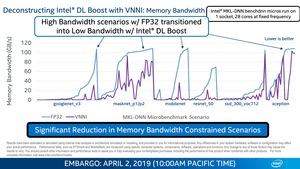

Intel liefert dazu auch gleich eigene Benchmarks, welche dies belegen sollen:

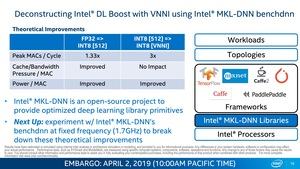

Die VNNI-Optimierungen zeigen sich in einer höheren Leistung und/oder einer gleichzeitigen Reduzierung der Leistungsaufnahme. Zugleich sinkt die L2-Cache Missrate mit VNNI. Dies verhindern erneute Zugriffe auf den L3-Cache und reduziert damit dessen Belastung. Dritter Vorteil ist der reduzierte Bedarf nach Speicherbandbreite. Während ohne VNNI die Speicherbandbreite zum limitierenden Faktor werden kann, soll dies mit VNNI nicht mehr der Fall sein.

Die Anwendung von VNNI in den Xeon-Scalable-Prozessoren macht diese flexibler für den Einsatz im Training und Inferencing von Deep-Learning-Netzwerken. Noch immer aber sind für ein reines Inferencing, also eine Auswertung eines solchen Netzwerks, spezielle Prozessoren besser geeignet. Intel will diesen Bereich mit den Agilex-FPGAs abdecken.

Mehr Flexibilität durch Resource Director und Speed Select

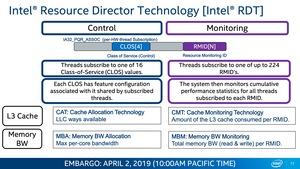

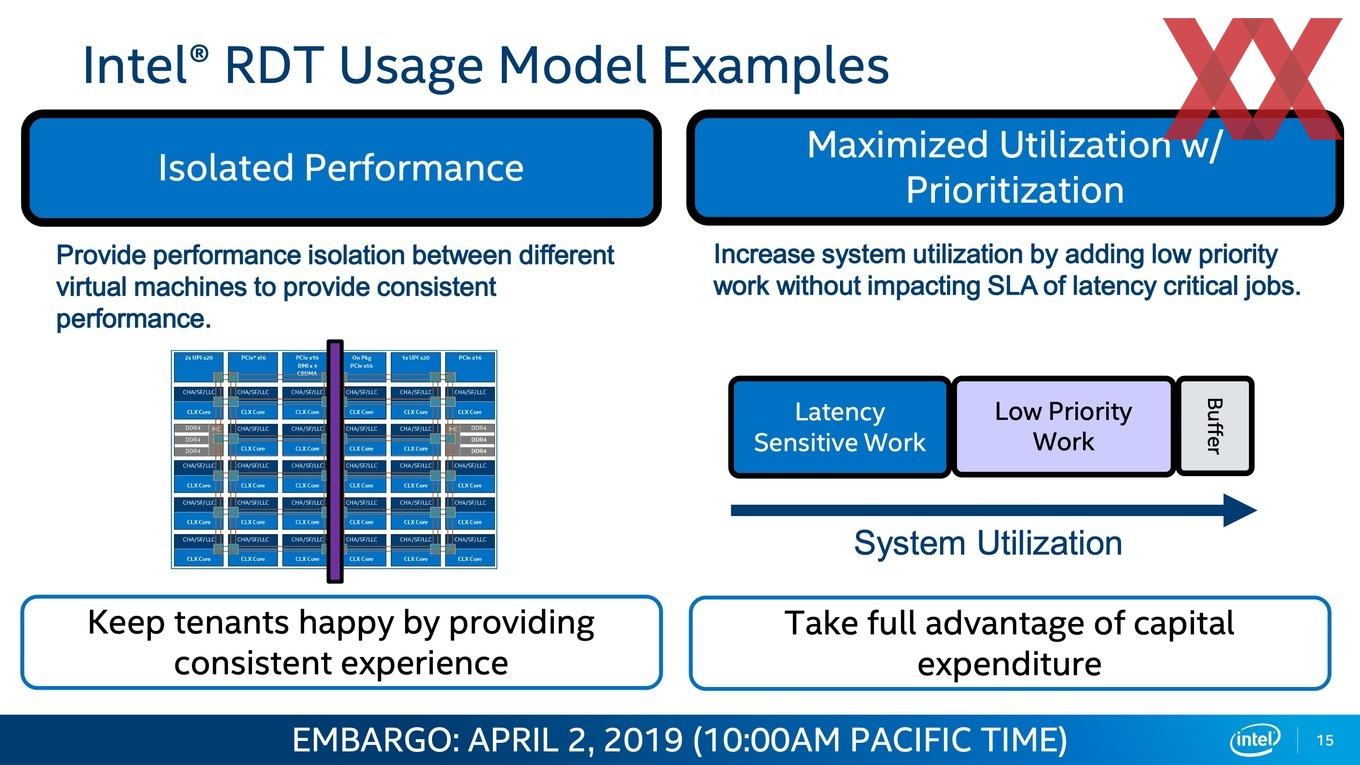

Bereits mit den Broadwell-Xeons führte Intel die Resource Director Technology (RDT) ein. Mittels RDT macht es Intel möglich, die zur Verfügung stehenden Ressourcen besser anzupassen. Der Nutzer oder Besitzer der Hardware bzw. des Servers hat die Wahl, ob dessen Ressourcen einem bestimmten Workload exklusiv zur Verfügung stehen oder ob sich diese flexibel zuteilen lassen.

Dazu werden die Caches und Speicherbandbreite ständig kontrolliert und können entsprechend zugeteilt werden. Ziel ist es die Prozessoren und das Datacenter besser auszulasten, denn typischerweise liegt die Auslastung bei weitem nicht bei 100 %. Je nach Plattform sind sogar weniger als 50 % typisch. Viel Hardware läuft also einen nicht unerheblichen Zeitraum ohne genutzt zu werden. Die Betreiber der Hardware sind aber natürlich daran interessiert die Auslastung so hoch wie möglich zu halten. Die Resource Director Technology macht vor allem für Cloud-Anbieter Sinn, kann aber je nach Unternehmen und dessen Anforderungsprofil auch in eigenen Rechenzentren Anwendung finden.

Diese Technologie soll eine Steuerung zwischen hoch-priorisierten und niedrig-priorisierten Workloads ermöglichen. Damit soll eine bessere Auslastung der Hardware ermöglicht werden. Damit wird aber auch einen Teil der Kontrolle über die Hardware abgegeben. Für Workloads, die auf eine exklusive Leistung angewiesen sind, kann RDT natürlich nicht angewendet werden.

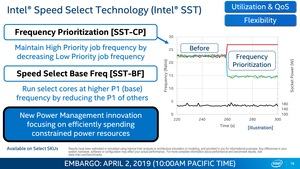

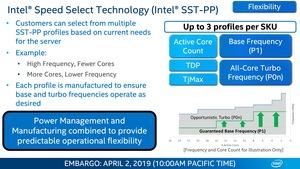

In eine ähnliche Kerbe wie die Resource Director Technology schlägt auch die Speed Select Technology (SST). Sie erlaubt es einer bestimmten Anzahl an Kernen besonders hoch zu takten. Dafür werden andere heruntergetaktet. Zum Start sieht Intel drei Xeon-Modelle vor, die über Profile verschieden angesteuert werden können.

Es gibt aber auch bestimmte Workloads, die sich auf einen gewissen Basistakt verlassen müssen, weil die Berechnung der Leistung entsprechend ausgelegt ist. Per Speed Select Technology lässt sich die Hardware auch hier besser steuern.

Hardware-Mitigationen gegen Sidechannel-Attacken

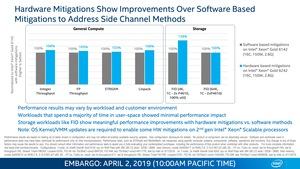

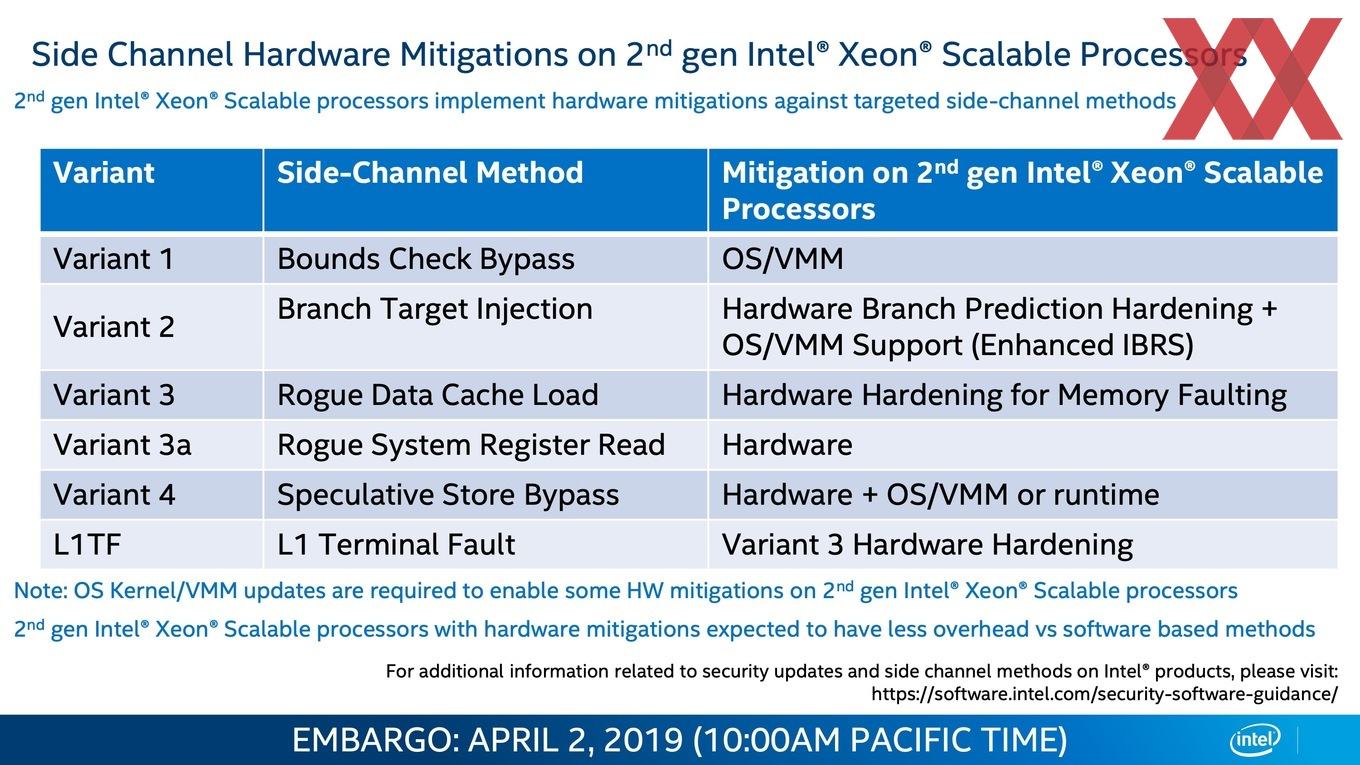

Noch eine ganze Zeit lang wird Intel die Sicherheitslücken Spectre und Meltdown begleiten. Diese lassen sich als Sidechannel-Attacken zusammenfassen. Cascade Lake sieht folgende Verbesserungen in dieser Hinsicht vor, die sich in Kombination aus Hard- und Software wie folgt darstellen:

- Variante 1: Absicherung per Betriebssystem und VMM (Virtual Machine Monitor)

- Variante 2: Hardware Branch Prediction Hardening (was auch zukünftige Angriffe in der Richtung verhindern soll) + OS und VMM

- Variante 3: Hardware Hardening

- Variante 3a: Hardware

- Variante 4: Hardware + OS/VMM

- L1TF: durch Hardware Hardening für Variante 3 schon geschlossen

Intel kompensiert einige Leistungsverluste durch die Mitigation durch die grundsätzlich höhere Leistung der neuen Prozessoren im Hinblick auf deren Taktfrequenz. Das Taktplus von 200 bis 300 MHz wird also durch den Leistungsverlust wieder egalisiert. Damit ausgestanden ist das Thema somit noch lange nicht und zukünftige CPU-Architekturen werden beweisen müssen, ob sie durch die Auslegung im Design gegen Sidechannel-Attacken weitestgehend immun sind.