Werbung

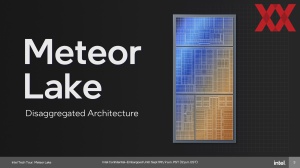

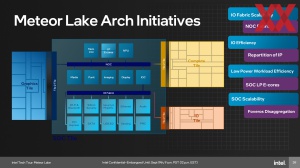

Die Meteor-Lake-Prozessoren für zukünftige Notebooks läuten für Intel eine neue Ära für das CPU-Design der Endkunden-CPUs ein. Erstmals kommen – nachdem diese Umstellung bei den Xeon-Prozessoren mit halber Schrittlänge bereits vollzogen wurde – auch im Client-Segment mehrere Chiplets (Tiles) bei Intel zusammen. Diese sollen dann als Einheit ein System on a Chip (SoC) darstellen. Vier Jahre hat Intel an Meteor Lake gearbeitet, doch die Basisbausteine stehen teilweise schon viel länger bereit. Wir erklären und beschreiben Meteor Lake in all seinen Feinheiten und Details.

Einen offiziellen Marktstart für Meteor Lake gibt es noch nicht. Mit dem heutigen Tag dürften wir über die technischen Aspekte sprechen, aber es gibt noch keine Modellliste oder dergleichen. Und so können wir heute allenfalls über die maximalen Ausbaustufen sprechen, Taktraten oder Power-Limits will Intel später bekanntgeben.

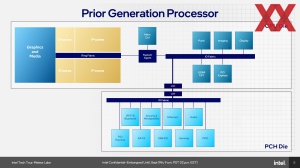

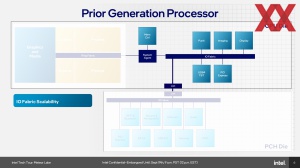

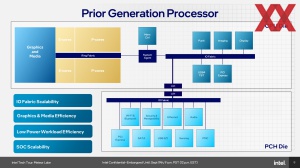

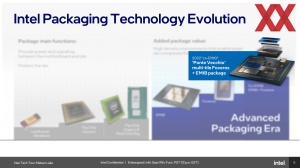

Über Jahre wurden immer mehr Komponenten in den Prozessor integriert. Mehr als ein Kern, Speichercontroller, eine integrierte Grafikeinheit und zuletzt immer mehr I/O-Funktionen, die zuvor über South- und Northbridge realisiert wurden. Nun geht man per Disintegration wieder den anderen Weg. Für mehr Flexibilität in der Fertigung und letztendlich im Produktangebot selbst wird ein Prozessor wieder in seine Bestandteile zerlegt, die dann getrennt voneinander entwickelt und gefertigt werden, um sie abschießend wieder zusammenzubringen.

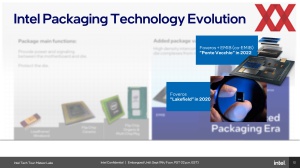

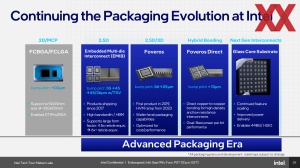

Die Fertigung ist ein wichtiger Faktor, das bisher oftmals vergleichsweise technisch einfache Packaging rückt mehr und mehr in den Fokus. Welchen Stellenwert das Packaging bereits hat und welchen es künftig spielen wird, davon konnten wir uns kürzlich selbst bei Intel in Malaysia einen Eindruck verschaffen.

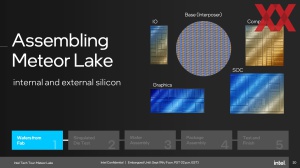

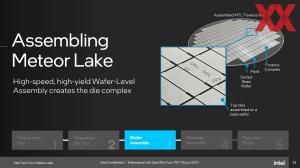

Dort konnten wir bereits sehen, wie die ersten Meteor-Lake-Prozessoren zusammengesetzt werden. Die einzelnen Chips kommen aus Irland und Taiwan, werden in Oregon per Advanced Packaging (für die Massenfertig im US-Bundesstaat New Mexico) verarbeitet und kommen dann für das finale Packaging nach Malaysia.

Ein desintegriertes Design und seine Bausteine

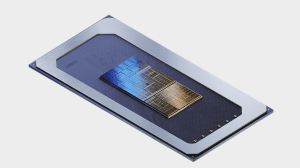

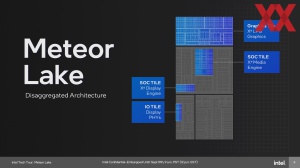

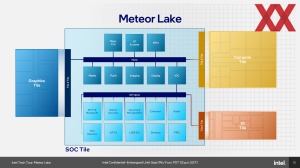

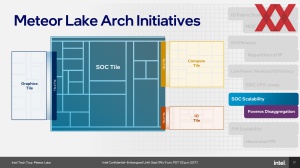

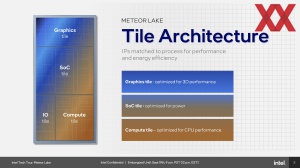

Ein Meteor-Lake-Prozessor besteht aus fünf einzelnen Chips, die per Foveros miteinander verbunden werden:

- Compute-Tile (mit den CPU-Kernen:): Intel 4

- Graphics-Tile: TSMC N5

- SoC-Tile: TSMC N6

- I/O-Tile: TSMC N6

- Base-Tile: Intel 22FFL

Bereits auf den ersten Blick zu erkennen, ist, dass Intel nur den Compute-Tile und das Base-Tile selbst fertigt. Der Rest kommt von TSMC. Mit der Entscheidung, Meteor Lake in der aktuellen Version so auf den Markt zu bringen, entschied sich Intel einige der Tiles bei TSMC fertigen zu lassen. Die Beweggründe waren einfach: TSMC bot die notwendigen Kapazitäten und kann beispielsweise den Graphics-Tile so fertigen, wie er die ideale Charakteristik enthält – Takt, Verbrauch und Chipfläche. Dies gilt in gewisser Weise auch für den SoC- und den I/O-Tile.

Der Compute-Tile beinhaltet die Rechenkerne, aber erstmals verwendet Intel einige E-Cores auch in anderen Tiles – dazu später mehr. Die E-Cores von Meteor Lake basieren auf dem Crestmont-Design. Die P-Cores sind ein Redwood-Cove-Design. Den Compute-Tile kann Intel austauschen – sprich in verschiedenen Konfigurationen anbieten. Sicher ist nur, dass es eine 6P+8E-Konfiguration geben wird.

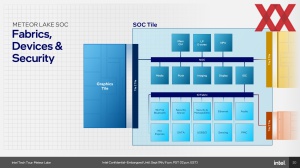

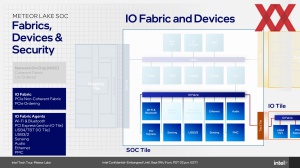

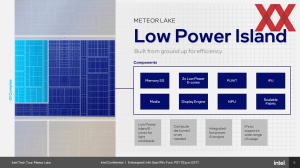

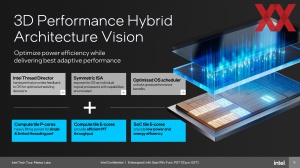

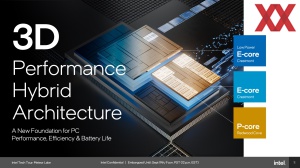

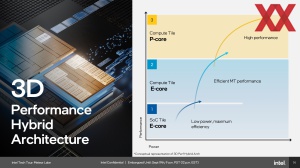

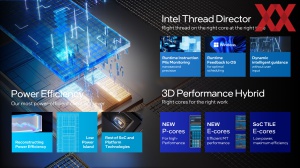

Bestandteile des SoC-Tile sind sogenannte Low-Power-Island E-Cores. Das Design besteht aus P- und E-Cores im Compute-Tile und zusätzlichen Lower-E-Cores im SoC-Tile, was Intel 3D Performance Hybrid Architecture nennt. Hinzu kommen im SoC-Tile eine NPU AI Engine, WiFi 7 & Bluetooth, ein Media-Block für AV1, 8K HDR mit der Möglichkeit, die Display-Signale per HDMI 2.1 und DisplayPort 2.1 auszugeben, sowie der Speichercontroller.

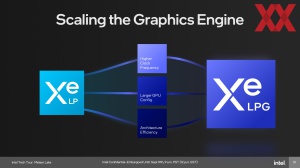

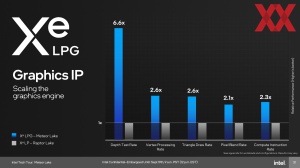

Der Graphics-Tile verwendet die Xe-LPG-Architektur, auf deren Details wir noch etwas genauer eingehen werden. Die Grafikeinheit soll ein um den Faktor 2 besseres Performance-pro-Watt-Verhältnis als Xe-LP, also die bisherige integrierte Grafikeinheit, bieten. Den Graphics-Tile wird es in zwei Ausbaustufen geben.

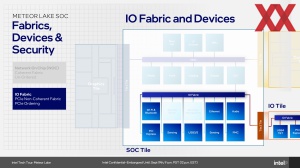

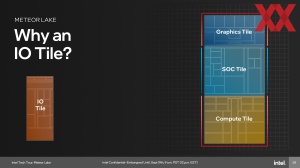

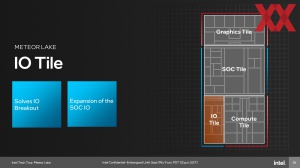

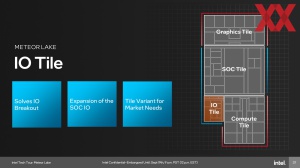

Der I/O-Tile ist für Funktionen wie Thunderbolt und PCI-Express verantwortlich. Auch vom I/O-Tile wird es zwei Varianten geben, die je nach notwendigem I/O-Angebot mal mehr und mal weniger PCI-Express-Lanes zur Verfügung stellen.

Die Desintegration hat aber nicht nur Vorteile hinsichtlich der Fertigung. Aus Sicht der einzelnen Funktionen kann Intel hier gezielter aufteilen, welche dieser Funktionen zusammengefasst werden sollen, weil diese in typischen Anwendungsbereichen ohnehin zusammenarbeiten müssen.

So war der Media-Block bisher ein Bestandteil der integrierten Grafikeinheit. Für ein Decoding von Video mussten immer der Core Complex, inklusive Caches und des Fabrics aufgeweckt und verwendet werden. Der Core Complex mit den Rechenkernen und die Caches hatten mit dem eigentlichen Decoding nichts zu tun und wurden daher unnötig mit Strom versorgt, was den Verbrauch erhöhte.

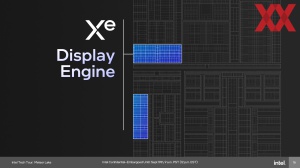

Der Media-Block ist nun Bestandteil des SoC-Tiles und diesem kommt insgesamt eine sehr wichtige Funktion zu – für viele Anwendungsbereiche. Der Core Complex befindet sich im Compute-Tile und der Graphics-Tile beinhaltet nur noch die Shadereinheiten für ein Rendering (und AMX-Einheiten für bestimmte AI-Anwendungen). Die Display Engine befindet sich ebenfalls im SoC-Tile, so dass auch für die Ausgabe keine weiteren Blöcke oder Tiles verwendet werden müssen. An dieser Stelle wird jedoch deutlich, dass Intel durch die Abtrennung des Media-Blocks nur noch den SoC-Tile für ein Decoding von Video-Material benötigt. Der Compute- und Graphics-Tile werden dazu nicht mehr benötigt.

Im SoC-Tile verwendet werden die LP E-Cores. Diese basieren ebenfalls auf dem Crestmont-Design. Maximal zwei Kerne kommen hier zum Einsatz und teilen sich einen 4 MB großen L3-Cache. Im Hinblick auf die Takt/Spannungskurve arbeiten diese E-Kerne natürlich in einem anderen Fenster. Hinzu kommt, dass der SoC-Tile eben von TSMC in N6 gefertigt wird, während die weiteren E- und P-Kerne im Compute-Tile von Intel in Intel 4 gefertigt werden. Die Design-Richtlinien und Charakteristiken im Transistordesign sind an dieser Stelle andere.

P- und E-Kern-Architektur

Performance-Kerne (Redwood Cove)

Die P-Kerne basieren wie gesagt auf dem Redwood-Cove-Design. Die Änderungen zum Vorgänger Golden Cove sind jedoch nicht besonders groß. Genauer gesagt soll die IPC-Leistung im Vergleich zu Golden Cove sogar fast identisch sein, so dass Meteor Lake nur über einen höheren Takt auf mehr Single-Core-Performance kommt, bzw. über mehr Kerne auf eine höhere Multi-Threaded-Leistung.

Die Effizienz lag in der Entwicklung von Redwood Cove im Hinblick auf Meteor Lake offenbar im Fokus. Aber die Redwood-Cove-Kerne werden auch in weiteren Prozessoren zum Einsatz kommen und hier wäre ein IPC-Plus sicherlich sinnvoll gewesen.

Jeden P-Kern stehen 46 kB an Data- und Instruction-L1-Cache sowie 2 MB an privaten L2-Cache zur Verfügung.

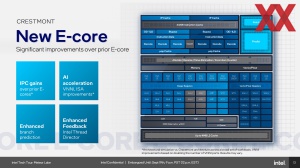

Efficiency-Kerne (Crestmont)

Im Vergleich zur Vorgänger-Architektur Gracemont soll es für die Crestmont-Kerne in Meteor Lake eine Steigerung in der IPC-Leistung von 4 % geben. Jedem Kern stehen 32 kB Data- und 64 kB Instruction-L1-Cache zur Verfügung. Es bleibt in der Anordnung bei 4 MB an L2-Cache über vier E-Kerne hinweg – so wie bei den aktuellen Raptor-Lake-Modellen.

Auf alle Details der neuen P- und E-Kern-Architekturen werden wir zum Start der neuen Prozessoren noch genauer eingehen. An dieser Stelle reichen die Angaben zu eher moderaten IPC-Steigerung als Information aus.

Graphics-Tile mit Xe-LPG

Neben dem Compute-Tile kommt der integrierten Grafikeinheit eine größere Bedeutung zu. Wie bereits erwähnt, soll die Grafik-Einheit der Meteor-Lake-Prozessoren ein um den Faktor 2 bessere Leistung-pro-Watt-Verhältnis aufweisen als der Vorgänger.

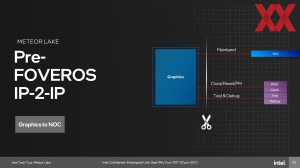

Media- und Display-Engine sowie die eigentlichen Grafikeinheiten finden sich wie gesagt nicht mehr nur an einer Stelle des Chips, bzw. sind auch nicht komplett in einem Tile ausgelagert, sondern so verteilt, dass sie möglichst effizient genutzt werden können. Die Shadereinheiten samt Cache befinden sich im Graphics-Tile. Die Media Engine sitzt im SoC-Tile, genau wie die Display-Engine. Im I/O-Tile befinden sich die Interfaces und PHYs, um die Display-Ausgänge umsetzen zu können.

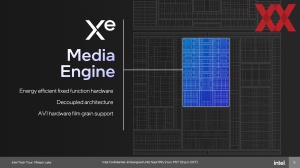

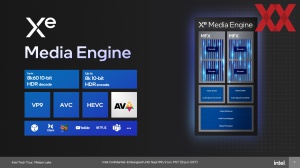

Unterstützt werden die gängigen Video- und Bildformate wie JPEG, MPEG, AV1, VP9 und HEVC. Hinsichtlich der Display-Ausgabe möglich sind 8K@60 in 10 Bit für ein De- und Encoding. In der Media-Engine vorhanden sind zwei MFX-Engines, die wiederum jeweils einen De- und Encoder enthalten. Sämtliche Funktionseinheiten sind Fixed Function Units, was eine hohe Leistung und Effizienz sicherstellen soll. So gehen alle Chiphersteller vor, die dedizierte En- und Decoder in ihren Prozessoren verbauen.

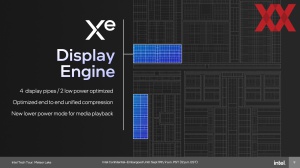

Die Display-Engine kann vier Displays ansteuern. Mit der Nutzung von zwei Ausgaben arbeitet die Display-Engine in ihrem idealen Effizienzfenster. An Standards unterstützt werden HDMI 2.1 und DisplayPort 2.1 – entsprechend eben einmal 8K@60 oder bis zu viermal 4K@60.

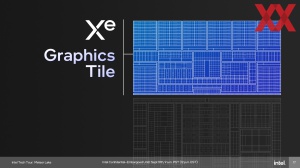

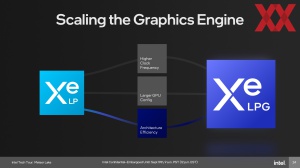

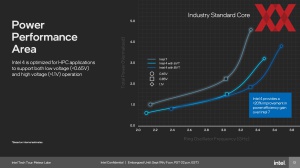

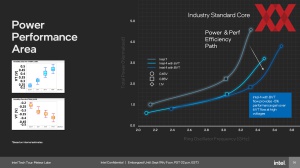

Für den Graphics-Tile zum Einsatz kommt die Xe-LPG-Architektur. Sie basiert grundsätzlich auf der ersten Xe-Architektur (Arc / Xe-HPG), wurde aber angepasst, um für den mobilen Betrieb besser optimiert zu sein. Dazu gehört, dass Intel den Chip bei TSMC in N5 fertigen lässt.

Grundsätzlich ist es mit dem Graphics-Tile möglich, diesen bei einer niedrigeren Spannung und gleichzeitig mit höheren Taktraten zu betreiben. Ein Arc-Chip aus TSMCs N6-Fertigung, wie wir ihn bei den Desktop-Karten sehen, arbeitet in einem anderen Betriebspunkt der Spannungs/Takt-Kurve als dies für den Graphics-Tile von Meteor Lake der Fall ist.

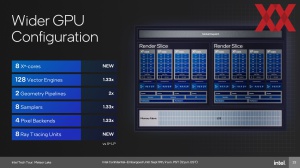

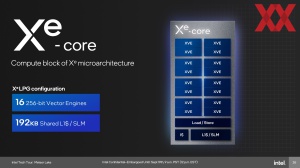

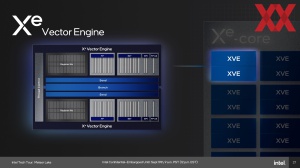

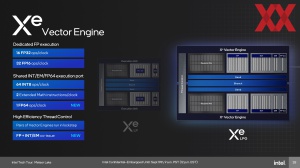

Der Chip verwendet im Maximalausbau acht Xe-Kernen mit 128 Vektor-Einheiten, zwei Geometrie-Pipelines und acht Raytracing-Einheiten. Jeder Xe-Kern besteht aus 16 256 Bit breiten Vektor-Einheiten und zudem 192 kB an L1-Cache.

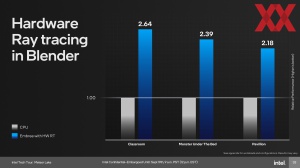

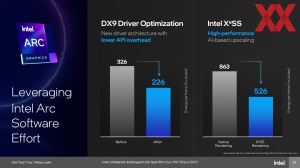

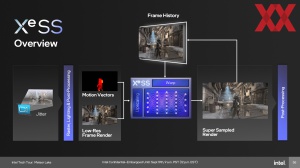

Was die integrierte Grafikeinheit zu leisten im Stande ist, wird sich zeigen müssen, wenn wir den ersten Meteor-Lake-Prozessor in Händen halten. Die Entwicklung des Arc-Treibers in den vergangenen zwölf Monaten soll sich natürlich positiv auswirken. Auch XeSS als Unterstützung – um auf möglichst hohe Bildraten zu kommen – spielt eine wichtige Rolle.

Interessanterweise unterstützt Xe-LPG die doppelte Genauigkeit in Form von FP64, was Xe-HPG bei den aktuellen Arc-Karten verwehrt blieb. Auch hier hat Intel also dazugelernt.

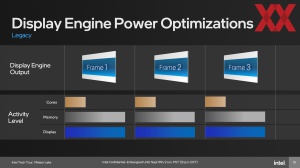

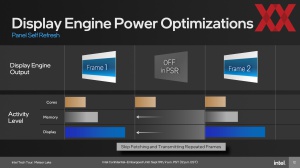

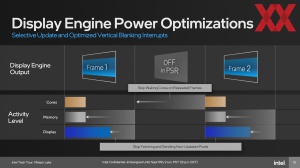

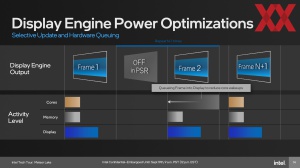

Zwei Techniken verwendet Intel im Zusammenspiel mit der integrierten Grafikeinheit, um die Effizienz zu verbessern. Panel Self Refesh (PSR) ist dabei allerdings keine neue Technik und wird bereits verwendet. Dabei geht es darum, dass ein Display mit sagen wir 60 Hz nicht auch 60 neue Bilder darstellt und diese daher nicht immer wieder neu berechnet werden müssen. Um einen Frame darzustellen, arbeiten die Kerne, Speicher und die Display-Engine zusammen. Bei einem Frame, der per PSR nur aufgefrischt wird, ist es jedoch nicht zwangsläufig notwendig, dass all diese Komponenten arbeiten. Dies soll sich positiv auf die Akkulaufzeit auswirken.

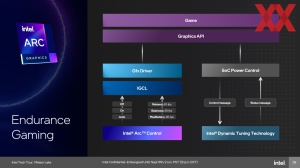

Für ein 3D-Rendering, bzw. für Spiele sieht Intel ebenfalls eine neue Software-Funktion vor. Das Endurance Gaming ermöglicht per Arc Control die Einstellung gewisser Einsparungs-Ziele, bei gleichzeitiger Einhaltung eines FPS-Ziels.

Schnelle und unterschiedliche Interconnects

Werden derart viele unterschiedliche IP-Blöcke und Tiles miteinander verbunden, ist die Wahl der richtigen Interconnect-Technologie von entscheidender Bedeutung. Der Media-Block, Graphics-Tile, die NPU - all diese Blöcke tragen zu einem höheren Datenverkehr bei und müssen entsprechend schnell angebunden sein.

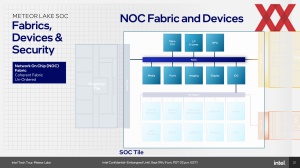

Der I/O Port im SoC-Tile ist beispielsweise eine kritische Komponente, da über ihn alle wichtigen Daten geführt werden. Im bisherigen Chip-Design griff die integrierte Grafikeinheit auf den L3-Cache/LLC (Last Level Cache) des Core Complex zu, was durch einen entsprechenden Ring-Stop im Ring-Interconnect repräsentiert wurde. Der Graphics-Tile verfügt nun über einen eigenen L3-Cache, denn sonst müsste die Grafikeinheit auf den LLC des Core Complex zurückgreifen, der entsprechende Datenverkehr durch den SoC-Tile stattfinden.

Für die Anbindung zwischen SoC- und Compute-Tile setzt Intel einen Scalable Fabric auf Basis eines In-Die Interface ein, das mit verschiedenen Frequenzen arbeiten kann. Die maximale Bandbreite des Scalable Fabric liegt auf Niveau der Anbindung des externen Speichers, denn schließlich müssen die Daten vom Speichercontroller im SoC-Tile in den Core Complex im Compute-Tile.

Ein IOC (I/O-Controller) bindet den I/O-Tile an. Zwischen dem SoC- und dem Graphics-Tile kommt ein iCXL zum Einsatz, das einer PCI-Express-Verbindung nicht unähnlich ist.

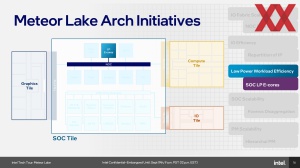

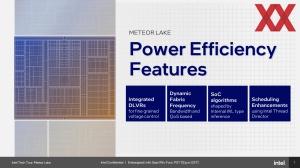

Feinkörniges Power-Management

Zur Effizient gehört aber nicht nur eine Desintegration der einzelnen Komponenten und Neuzuordnung auf den Tiles, sondern außerdem ein möglichst effizientes Power-Management. In jedem Tile befindet sich ein PCM (Power Management Controller). Für eine noch feinkörnigere Ansteuerung besitzt das SoC-Subsystem weitere PMCs, welche sich um die verschiedenen Blöcke im SoC-Tile kümmern. Der I/O- und Compute-Tile sind sogenannte Low Power Islands, die zur Einsparung von Strom komplett abgeschaltet werden können. Theoretisch wäre es möglich, einen Meteor-Lake-Prozessor nur über den SoC-Tile zu betreiben.

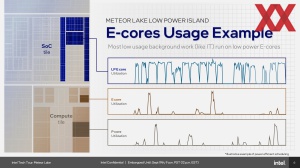

Ein wichtiger Bestanteil der Effizienz kommt den LP-E-Kernen zu, denn sie werden die am häufigsten verwendeten Kerne eines Meteor-Lake-Prozessors sein. Alle Hintergrundaufnahmen werden von ihnen übernommen. Bei Bedarf schalten sich dann die E-Kerne auf dem Compute-Tile hinzu. Die P-Kerne werden nur dann verwendet, wenn deren Leistung wirklich benötig wird.

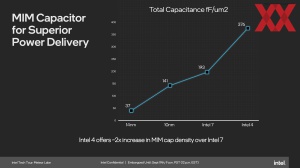

Bereits Bestandteil vorherigen CPU-Designs von Intel, aber nicht immer verwendet, waren für die Spannungsversorgung die DLVRs (Digital Linear Voltage Regulator). Über die DLVR in Meteor Lake können einzelne P- und E-Kerne sowie die IP-Blöcke getrennt voneinander angesteuert werden.

All diese Maßnahmen dienen dazu die Effizienz des Prozessors zu erhöhen – ihn immer im idealen Betriebsfenster für seinen Takt und die notwendige Spannung arbeiten zu lassen. Die Effizienz war mit der wichtigste Punkt in der Auslegung von Meteor Lake – von der Desintegration angefangen, bis zur Mikroarchitektur der Kerne.

Fertigung in Intel 4 - zumindest teilweise

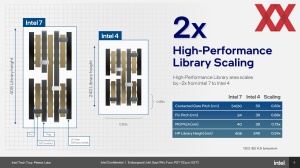

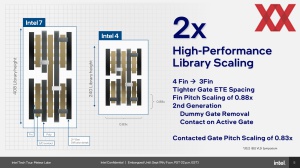

Wie bereits in der Beschreibung der einzelnen Tiles zu Meteor Lake erwähnt, setzt Intel nur für die Fertigung des Compute-Tiles auf eine neue Fertigung aus eigenem Hause: Intel 4.

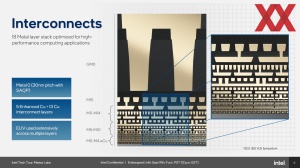

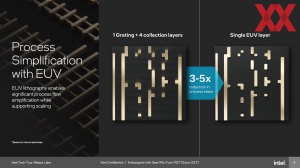

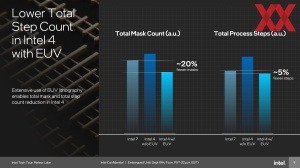

Intel 4 ist der erste Prozess des Chipriesen, in dem EUV (Extreme Ultraviolet) für einige der Belichtungsschritte verwendet wird. Der Einsatz vereinfacht einige Fertigungsschritte bzw. macht es möglich, mit weniger Belichtungen auszukommen. Um den Faktor drei bis fünf weniger Prozessschritte sollen nun notwendig sein.

Eine zu hohe Komplexität im Zusammenspiel der gewählten Belichtungsschritte und Materialien sorgten für die langanhaltenden Probleme mit der Fertigung in 10 nm, die Intel erst nach der Umbenennung zu Intel 7 überwunden hat. Teilweise musste Intel in den Metallagen M0 und M1 in 10 nm 20 Schritte und 20 Masken verwenden, um diese Bereiche korrekt zu belichten. Dies kostet natürlich Zeit und Geld – war somit für eine Massenfertigung nicht tragbar. Mit Intel 4 sollen es nun deutlich weniger sein und insgesamt sind 60 % weniger Masken notwendig als noch mit Intel 7 aktuell.

Insgesamt vorhanden sind 13 Lagen, von denen die ersten fünf ein verbessertes Kupfer (enhanced Copper) verwenden. Für Intel 7 kamen ein Kupfer-Liegerung und pures Kobalt zum Einsatz. Der Pitch in der obersten Metallschicht (M0) liegt bei 30 nm.

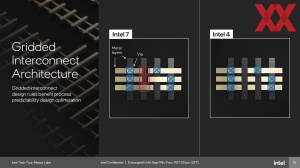

Um das Design der Metalllagen und des gesamten Chips zu vereinfachen, hat Intel aber auch neue Designregeln festgelegt. Die Bereiche, in denen TSVs möglich sind, sind limitiert. Somit können Bereiche ohne die TSVs besser optimiert werden und die Fertigung wird vereinfacht.

Mit Intel 4 spricht Intel von der besten Ausbeute für einen neuen Prozess in den vergangenen 10 Jahren – also in etwa die Spanne, in der man an 10 nm gearbeitet hat, das sei an der Stelle auch gesagt. Intel 3 wird auf Intel 4 aufbauen und ermöglicht eine größere Flexibilität in der VF-Kurve. Intel 3 ist also kein komplett neuer Fertigungsschritt, sondern ein Zwischenschritt, so wie es auch Intel 18A gegenüber Intel 20A sein wird.

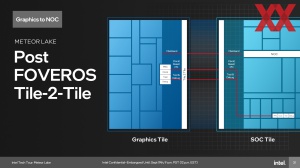

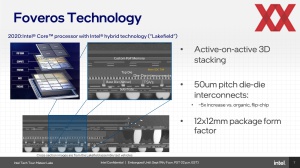

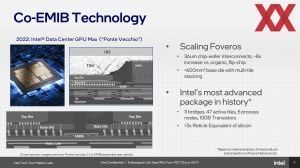

Foveros im Packaging

Für das Package von Meteor Lake zum Einsatz kommt das Foveros-Packaging. Nach Lakefield (im Test) und Ponte Vecchio wird Foveros mit Meteor Lake erstmals für größere Stückzahlen verwendet.

Die Entwicklung von Foveros begann vor etwa sechs Jahren. Dass wir Lakefield bereits Mitte 2020 testen konnten und hier bereits Foveros zum Einsatz kam, zeigt zudem, dass die Packaging-Technologien schon recht früh weitestgehend fertig entwickelt waren, Intel aber an anderer Stelle (vermeintlich der Fertigung der Chips selbst) noch nicht so weit war.

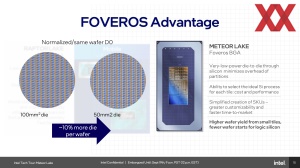

Für Meteor Lake kommt aber nicht die erste Iteration von Foveros mit einem Bumb Pitch von 50 µm zum Einsatz, sondern bereits die verbesserte Version mit 36 µm.

Die Tile-2-Tile-Verbindungen sind allesamt aus physikalischer Sicht identisch. Im Foveros-Chip befinden sich tausende Drähte, die mit unterschiedlichen Protokollen verwendet werden. Aus den unterschiedlichen Protokollen und Taktfrequenzen ergeben sich dann auch unterschiedliche Bandbreiten für diese Tile-2-Tile-Verbindungen. Die Lanzen sind aber immer identisch, da es kein/kaum ein Protokoll-Overhead gibt und die Distanzen ebenfalls identisch sind.

Für Meteor Lake muss man auch zwischen dem Foveros-Package (Foveros Complex) unterscheiden, welches die fünf Tiles enthält, die eben per Foveros miteinander verbunden sind und dem eigentlichen Package, welches dann auf das Logicboard im Notebook aufgesetzt bzw. mit diesem verlötet wird. Im Package-Substrat verwendet Intel ein OPI (On-Package Interconnect). Wir konzentrieren uns hier aber auf die direkten Die-2-Verbindungen.

Im SoC-Tile ist ein NOC (Network on a Chip Fabric) vorhanden, der die LP E-Cores, Speichercontroller, NPU, IPU, Media- und Display-Engine miteinander verbindet. Der NOC ist dabei ein Cache-kohärenter Fabric, das heißt, ein vorhandener Cache steht allen IP-Blöcken zur Verfügung, die darüber angebunden sind. Der I/O-Fabric bindet die weiteren Blöcke an. Der NOC und I/O-Fabric sind über einen I/O-Controller miteinander verbunden.

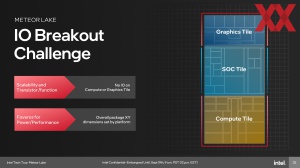

Beim Design des gesamten Package mit bedacht werden muss auch, dass I/O-Verbindungen (die sogenannten I/O Breakouts) nur am SoC- und I/O-Tile möglich sind. Graphics- und Compute-Tile verfügen über keine Verbindungen nach außen hin. Entsprechend wurden der SoC- und vor allem der I/O-Tile auch in ihren Dimensionen geplant, damit ausreichend Fläche für die I/O-Verbindungen zur Verfügung stehen.

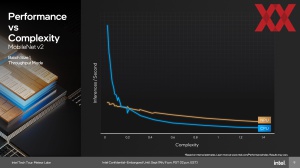

Das Packaging hat aber auch weitere Herausforderungen, denn im Grunde wird die Fertigung der Chips als solches zwar einfacher, das Package aber wird deutlich komplexer. Wir sehen hier also eine Verschiebung in der Komplexität.

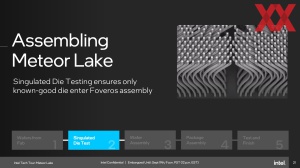

Im Singulated Die Testing wird jeder Chip getestet, bevor er in das Package gebracht wird. Natürlich will man keine defekten Chips auf das Package bringen, denn stellt man dies erst nachher fest, ist das gesamte Package nicht mehr zu gebrauchen. Beprobt werden können Chips mit einem Bump Pitch von 36 µm. So viele defekte Chips wie möglich müssen erkannt und aussortiert werden, denn eine womöglich schlechte Ausbeute potenziert sich bei fünf Chips auf einem Package schnell. Danach werden die einzelnen Tiles auf dem Base-Tile-Die bzw. dem Foveros-Wafer aufgebracht.

Darauf folgt das Package Assembly. Der Foveros Complex wird auf das Package Substrat aufgebracht. Im Testing wird im Nachgang untersucht, ob das Package weiterhin funktionsfähig ist. An dieser Stelle können wir nur noch einmal auf unseren Bericht zum Besuch des Packaging-Werks von Intel in Malaysia verweisen, denn er gibt ein paar Einblicke in das aufwendige Die-Testing und Packaging.

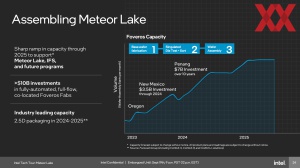

Für die ersten Test-Chips von Meteor Lake wird das Foveros-Packaging noch im US-Bundesstaat Oregon durchgeführt. Für die Massenproduktion wird das Werk in Arizona oder das im Bundesstaat New Mexico herangezogen. Aber Intel will Meteor Lake und die zukünftigen Generationen in Millionenstückzahlen an den Mann und die Frau bringen und insofern benötigt man deutlich höhere Kapazitäten. Bis 2025 sollen diesen um den Faktor vier steigen.

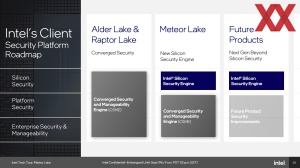

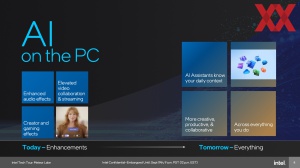

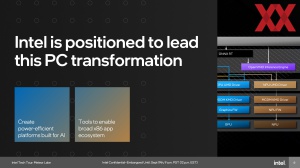

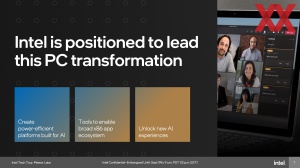

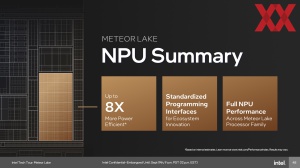

Meteor Lake und AI

Die Notwendigkeit nach dedizierter AI-Hardware sehen fast alle Hersteller – sei es Intel, AMD oder NVIDIA. Während dies in bestimmten Segmenten bereits alltäglich genutzt wird (siehe DLSS von NVIDIA oder Bildanalyse-Software), sollen die Anforderungen in den kommenden Jahren weiter signifikant wachsen.

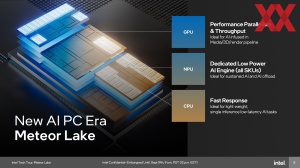

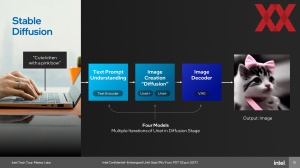

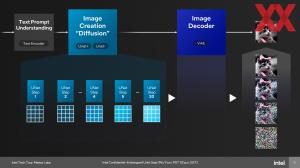

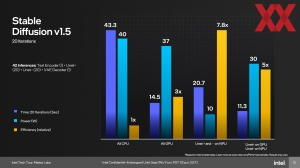

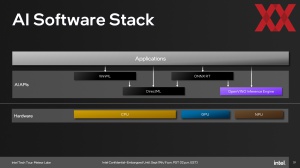

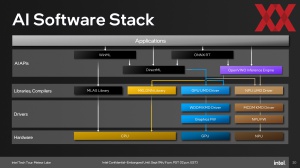

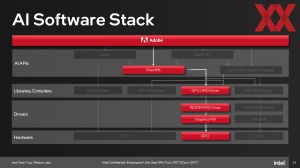

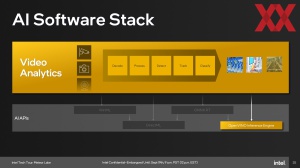

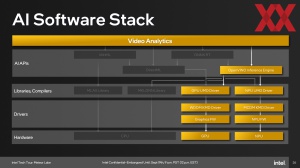

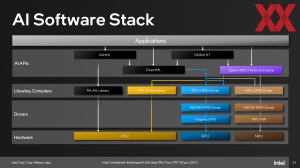

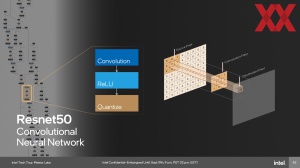

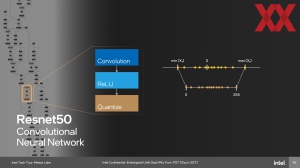

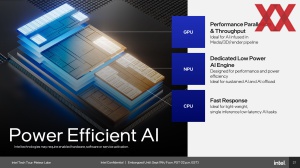

Zukünftig sollen die AI-Workloads auf gleich drei "Beschleuniger" bzw. Ressourcen zurückgreifen können. Die GPU wird weiterhin in der Lage sein, AI-Workloads in parallelisierter Art und Weise auszuführen und erreicht einen hohen Durchsatz. Dies ist ideal für Foto-, Video- und 3D-Inhalte, die per AI unterstützt oder bearbeitet werden.

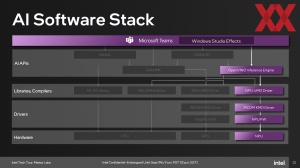

Auch die CPU-Kerne können leichte Inferencing-Aufgaben übernehmen. Die nun integrierte VPU übernimmt AI-Aufgaben, die in gewisser Weise ständig nebenher laufen oder deutlich aufwendiger sind. Dazu gehört auch eine Thread Detection, aber auch das Einblenden eines anderen Hintergrunds in einer Webkonferenz oder die Geräuschunterdrückung.

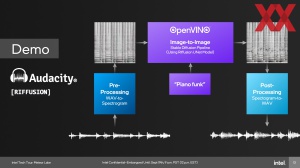

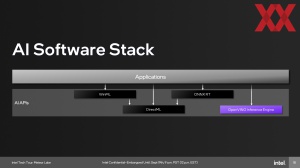

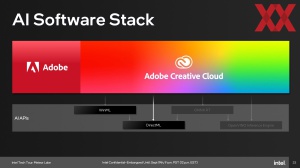

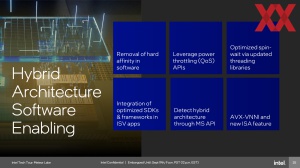

Welche Hardware schneller oder effizienter ist, hängt auch von der jeweiligen Anwendung ab. Am Beispiel von Stable Diffusion zeigt sich, dass die GPU schneller ist, aber eine höhere Leistungsaufnahme benötigt. Auf der NPU läuft die Verarbeitung nicht ganz so schnell, dafür aber deutlich effizienter. Theoretisch können die Anwendungen auf alle Ressourcen zugreifen. Dies wird für Meteor Lake aber noch nicht der Fall sein. Software-Entwickler können per ONNX, OpenVINO, W3C und DirectML als Schnittstelle bzw. Framework auf die Hardware zugreifen. Software von Adobe, Zoom, Blackmagic, Avid und viele mehr soll dann auf die dedizierte AI-Hardwarebeschleunigung zurückgreifen können. Aber die Zuordnung der Hardware erfolgt fix, ein Wechsel von der GPU in die NPU auf dynamischer Ebene ist nicht vorgesehen.

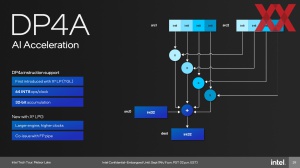

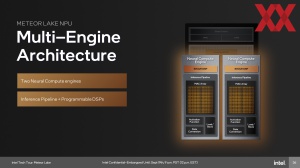

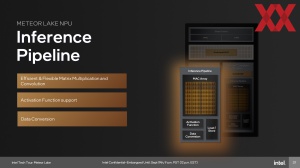

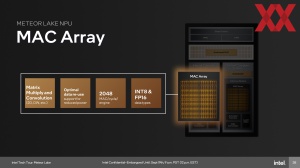

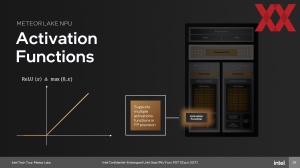

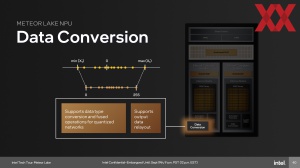

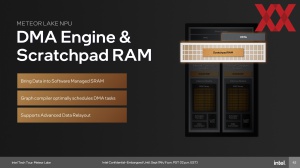

In Meteor Lake wird die dritte Generation der NPU IP verwendet. Die NPU besteht aus einem Scratchpad SRAM, der als Speicher der Daten verwendet wird, die in der NPU verarbeitet werden. Die NPU ist Cache kohärent mit dem Systemspeicher. Zwei Cluster aus MAC-Arrays (Neural Engine Engines) übernehmen die Berechnungen und sind einfach Matrix-Einheiten, wie wir sie von den MXM-Einheiten der Xe-Architektur bereits kennen.

Die Rechenleitung liegt bei 2.048 MAC (Multiply-Accumulate-Operation) pro Taktzyklus pro Engine bei INT8. Bei doppelter Genauigkeit (FP16) sind es noch 1.024 MAC pro Taktzyklus.

Die beiden Neural Engine Engines können an einer Aufgabe arbeiten oder teilen sich auf zwei Aufgaben auf – je nachdem, welche Anwendungen ausgeführt werden und was die Anforderungen sind.

3D Performance Hybrid Architecture und die Herausforderungen

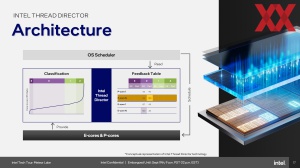

Der mit den Alder-Lake-Prozessoren eingeführte, hybride Aufbau durch den Einsatz von E- und P-Kernen sorgte mit der Ankündigung für viele Bedenken, ob denn das Betriebssysteme mit diesen unterschiedlichen Klassen an Kernen denn auch zurechtkommt. Tatsächlich gab es zum Start ein paar Probleme, vor allem bei Spielen, die anstatt den P- auf den E-Kernen liefen, aber das Scheduling per Thread Director und der entsprechenden Integration in Windows verlief dann schlussendlich besser als gedacht.

Mit den Meteor-Lake-Prozessoren führt Intel nun eine weitere Klasse an E-Kernen ein. Die LP E-Kerne sollen sämtliche Hintergrundaufgaben übernehmen und werden daher auch am häufigsten verwendet. Für die Multi-Threaded-Leistung bei möglichst hoher Effizienz sind die klassischen E-Kerne verantwortlich. Die P-Kerne stehen für besonders rechenintensive Aufgaben bereit.

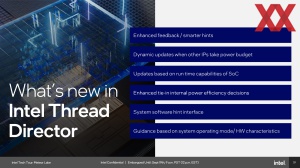

Der Thread Director wird entsprechend angepasst, um die neue LP E-Kerne mit einzubeziehen. Das bisherige Verfahren sah unter anderem vor, dass die Threads periodisch von den E- auf die P-Kerne geschoben, um sie immer wieder zu reklassifizieren. Jetzt mit den Meteor-Lake-Prozessoren wird versucht, den Thread auf den LP E-Cores des SoC-Tiles zu belassen. Wenn das nicht möglich ist, wird er auf die E-Kerne des Compute Tile verschoben. Allerdings ist dies nicht ganz trivial, da auch die Daten in den Caches ausgetauscht werden müssen. Dieser Prozess des Verschiebens ist also vergleichsweise teuer und sollte wenn möglich vermieden werden.

Erste Notebooks zum Jahreswechsel

So viel zur Theorie rund um Meteor Lake. Was wir bereits aus eigenen Quellen und Aussagen von Intel wissen ist, dass es die Meteor-Lake-Prozessoren in unterschiedlichen Konfigurationen geben wird. Den Compute-Tile wird es in einer 6P+8E-Kernen und mit 2P+4E-Kernen geben. Beim Graphics-Tile sind ebenfalls zwei Konfigurationen mit vier und acht Xe-Kernen vorgesehen. Zudem erwähnte Intel bereits, dass es zwei I/O-Tiles gibt. In welchen Kombinationen die Meteor-Lake-Prozessoren aber letztendlich auf den Markt kommen werden ist noch nicht bekannt.

Einen kompletten Tag lang verkündete Intel gegenüber den Pressevertretern die Neuigkeiten rund um Meteor Lake. Dazu gehörte auch, dass man gemeinsam mit seinen Notebook-Partnern an neuen Kühl-Konzepten und dergleichen gearbeitet hat. Das Design-Ziel, einen möglichst effizienten Prozessoren herzustellen spürt man in jedem der Aspekte, den wir in diesem Artikel angesprochen haben. Was sich zunächst noch zeigen wird, sind die Praxis-Ergebnisse und Erfahrungsberichte in dieser Hinsicht. Auch was die AI-Funktionen in Form der NPU und VPU letztendlich in der Praxis bringen werden, hängt wohl auch davon ab, wie schnell die Software diese vollständig verwendet.

Neben der Tatsache, dass wir heute noch keine konkreten Modelle der Meteor-Lake-Prozessoren nennen können, kennen wir nun zumindest den offiziellen Starttermin. Der 14. Dezember soll es sein, aber unklar ist, ob wir dann auch schon die ersten Notebooks mit Meteor Lake im Handel sehen werden. Dies wird wohl eher Anfang kommenden Jahres der Fall sein. Die CES in Las Vegas Anfang Januar dürfte demnach zur Plattform des Starts werden.