Werbung

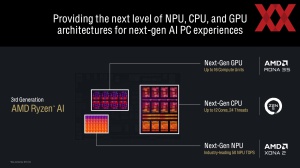

Auf seinem Tech Day in Los Angeles erläuterte AMD die Details zur Zen-5-Architektur, welche die Basis der Ryzen-AI-300- und Ryzen-9000-Prozessoren ist, die beide noch im Juli auf den Markt kommen werden. Gleich zu Beginn wollen wir dabei die Katze aus dem Sack lassen: Die Ryzen-9000-Prozessoren werden ab dem 31. Juli verfügbar sein. Preise nennt AMD zum jetzigen Zeitpunkt aber noch nicht.

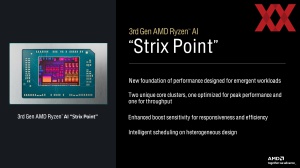

Ende Juli sollen auch die ersten Notebooks mit Ryzen-AI-300-Prozessore verfügbar sein. Auch zu diesen Prozessoren mit Codenamen Strix Point verriet AMD einige weitere Details, die Thema in diesem Artikel sein werden.

AMD beschäftigt insgesamt 20.000 Ingenieure, von deinen gleich mehrere Teams auch an der Entwicklung der Zen-5-Architektur beteiligt waren. Die sogenannten Base-Design-Teams sitzen in Santa Clara und Austin mit einer Unterstützung in der Entwicklung aus dem einem Office an der Ostküste in Boston. Hier entstehen die grundsätzlichen Designs einer Architektur und des SoC-Designs. Nach dem Tape-Out, also der Fertigung der ersten Chips, findet eine Verifikation in Folsom statt.

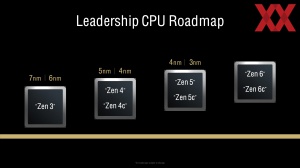

Für Zen 5 stand genau wie bei Zen 4 gleich von Anfang an die Auslegung auf einen klassischen Zen-Kern (Zen 5) und den kompakten Zen-5c-Kern auf dem Plan. Diese kommen, genau wie in der vorherigen Generation, aber nur bei den APUs (Ryzen AI 300) und später auch bei den EPYC-Prozessoren zum Einsatz.

Die Zen-5-Architektur

Bevor wir aber zur Zen-5-Architektur kommen, wollte AMD auf Nachfrage aber auch ein paar Worte zur Unterstützung von SMT (Simultaneous Multithreading) verlieren, denn Intel wird zumindest für Lunar Lake und bei der Lion-Cove-Architektur darauf verzichten. Die beiden Kern-Typen, also sowohl Zen 5 als auch Zen 5c, machen weiterhin keinerlei Unterschied und AMD sieht SMT als beste Funktion die Effizienz hochzuhalten. Die Umsetzung von SMT benötigt zwar rund 5-10 % Fläche im Kern, aber je nach Anwendung kann damit auch eine deutlich höhere Leistung erreicht werden. AMD verweist zudem darauf, dass SMT einfach abgeschaltet werden kann, was man für einige Produkte auch tut.

Auch zur aufkommenden Konkurrenz von ARM wollte man ein paar Worte verlieren: 1996 entwickelte man mit dem K5 den ersten eigenen x86-Prozessor. Seither habe sich die x86-Technik stetig weiterentwickelt. Mike Clark arbeitet als Vater der Zen-Architektur nun seit 31 Jahren an x86-Designs. Prozessoren auf Basis von x86-Instruktionen sollen laut AMD aber auch deutlich flexibler sein, als dies auf den ersten Blick den Anschein macht. Arm hat mit RISC sogenannte Fixed Length Instructions, während x86 in dieser Hinsicht flexibler ist. Aber alles habe eben Vor- und Nachteile. AMD sieht aber keine offensichtlichen Nachteile von x86 gegenüber ARM in diesem Segment.

Einige Details zur Zen-5-Architektur stellte AMD bereits zur Computex 2024 Anfang Juni vor. Nun aber gibt es ein paar weitere Informationen.

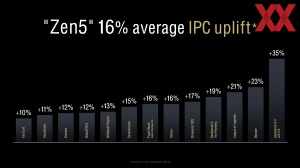

Zen 5 sollte mehr Instruktionen pro Taktzyklus ausführen können. Dazu waren verschiedene Maßnahmen notwendig. Unter anderem hat man die Dispatch- und Ausführungseinheiten verbreitert bzw. deren Anzahl erhöht. Die Sprungvorhersage macht pro Taktzyklus mehr Vorhersagen und soll auch eine höhere Genauigkeit erreichen. Dies erhöht den Durchsatz in der Sprungvorhersage.

Die Bandbreite des L1-Instruction-Cache wird verdoppelt und die Latenz verringert. Die Decode-Einheit ist zwar weiterhin 4-Way breit, wird aber verdoppelt. Auf Seiten der Ausführungseinheiten gibt es nun sechs ALUs statt wie bei Zen 4 bisher derer 4. Hinzu kommen drei Multiply-Einheiten.

Der L1-Data-Cache ist nun 48 kB groß und umfasst bei der Zen-4-Architektur 32 kB). Die größere Kapazität geht mit einer Verbreiterung auf 12-Way einher, wobei man die Load-Latenz mit vier Taktzyklen beibehalten konnte. Der L1D-Cache kann vier Lese- und zwei Schreibzugriffe ausführen.

Der L2-Cache ist weiterhin 1 MB pro Kern groß, erreicht aber mit einer Breite von 16-Way aber die doppelte Bandbreite. In der Cache-Hierarchie verdoppelt AMD demnach die Bandbreite vom L2-Cache bis in die Fließkomma-Einheiten hinein.

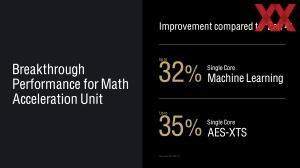

Die Fließkomma-Einheiten haben nun einen Datenpfad, der die vollen 512 Bit breit ist. Damit kann AMD nativ AVX-512-Befehlssätze ausführen und dabei bei vollem Takt.

RDNA-3.5-Architektur

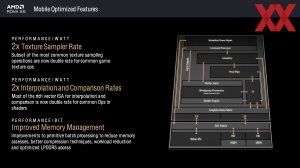

Erstmals kommt in einem AMD-Chip bzw. in einer APU wie der Ryzen-AI-300-Serie die RDNA-3-Architektur zum Einsatz. Die Ryzen-9000-Prozessoren verbleiben hingegen bei der integrierten RDNA-2-Grafikeinheit, was für den Einsatzbereich dieser aber auch vollkommen ausreichend ist. Bei den Desktop-Prozessoren geht es nur darum, rudimentäre Grafik-Fähigkeiten zu liefern. Bei den Strix-Point-Prozessoren sieht dies schon anders aus.

Im Vergleich zur Desktop-Implementierung der RDNA-3-Architektur hat AMD für RDNA 3.5 ein paar kleinere Änderungen vorgenommen, die sich aber vor allem darauf fokussieren, dass sie hier in einem mobilen Prozessor zum Einsatz kommt. Laut AMD hat man hier von der Zusammenarbeit mit Samsung profitiert bzw. der südkoreanische Chiphersteller hat sich eine entsprechende Lizenz bei AMD besorgt und die RDNA-Grafik in seine SoCs verpflanzt.

Die Änderungen, die man vorgenommen hat, beziehen sich auf eine Verdopplung der Texture-Samplerate sowie ebenfalls eine Verdopplung der Interpolation und Comparison Rates. Damit nimmt man einige Anpassungen vor, die wir auch mit der RDNA-4-Architektur wiedersehen werden und sich den Limits von RDNA 3 annehmen.

Zudem ist der Speichercontroller der RDNA-3.5-Architektur auf die Zusammenarbeit mit LPDDR5 ausgelegt und es gibt Optimierungen im Bereich der Cache-Zugriffe. AMD versucht hier so wenige Zugriffe wie möglich über den Arbeitsspeicher laufen zu lassen und die notwendigen Daten im Cache zu behalten.

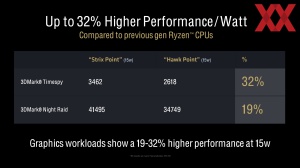

Wie wir im Abschnitt zu den Ryzen-AI-300-Prozessoren bereits gesehen haben, misst AMD eine um 19 bis 32 % höhere Leistung im Vergleich zur integrierten Grafik auf Basis von RDNA 2 (Hawk Point) bei 15 W.

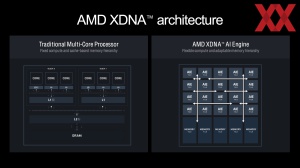

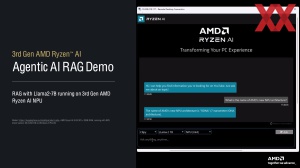

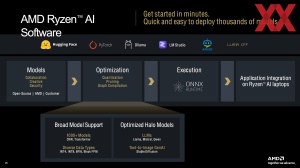

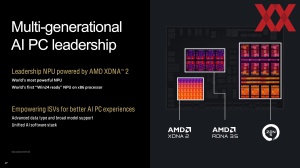

XDNA-2-NPU mit 50 TOPS

Nachdem AMD mit den Ryzen-7040-Prozessoren alias Phoenix bereits eine NPU einführte, diese aber aufgrund der fehlenden Software-Unterstützung nicht zum Einsatz kam und aufgrund eines Fehlers auch nicht so schnell wie geplant war (dieser Fehler wurde erst mit Hawk Point korrigiert), führt AMD mit Strix Point nun eine NPU auf Basis der XDNA-2-Architektur ein, die mit 50 TOPS sogar schneller als die in Intels Lunar-Lake-CPU sein soll und auch Qualcomms Snapdragon X Elite schlägt.

| Gesamtleistung | NPU | CPU | GPU | |

| Intel Lunar Lake | 120 TOPS | 48 TOPS | 5 TOPS | 67 TOPS |

| Intel Meteor Lake | 32,2 TOPS | 10,6 TOPS | 2,82 TOPS | 18,8 TOPS |

| Qualcomm Snapdragon X Elite | - | 45 TOPS | - | - |

| Ryzen-7040-Serie (Phoenix) | 33 TOPS | 10 TOPS | - | - |

| Ryzen-8040-Serie (Hawk Point) | 39 TOPS | 16 TOPS | - | - |

| Ryzen AI 300 (Strix Point) | - | 50 TOPS | - | - |

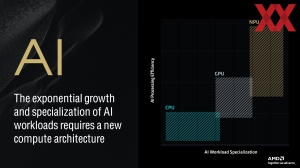

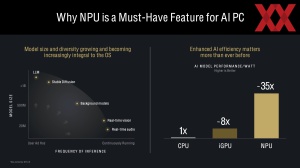

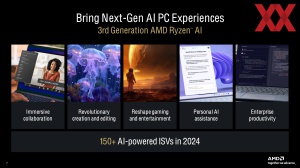

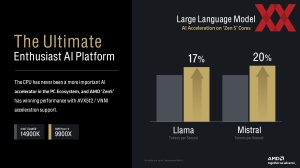

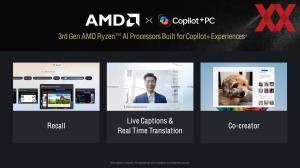

Das es in 2024 und darüber hinaus eine NPU im Chip benötigt, daran lässt AMD keinen Zweifel. Das diese dann ausgerechnet bei den Ryzen-9000-Prozessoren fehlt steht dabei wieder auf einem anderen Blatt. Aktuell liegt der Fokus vollständig auf den Notebooks mit Copilot+ – bei allen drei CPU-Herstellern.

Die NPU wird aber auch bei AMD nicht alle Aufgaben übernehmen, wenngleich die NPU sich auch für größere KI-Aufgaben eignen könnte und auch dazu eingesetzt werden wird. Es geht aber vorerst darum, die Hintergrundaufgaben im Audio- und Videobereich (Video-Konferenzen) zu übernehmen. Größere Inferencing-Aufgaben wir die KI-Bildgenerierung wird dann aber beispielsweise die GPU übernehmen.

Laut AMD hat man für die XDNA-2-Architektur einen anderen Ansatz gewählt, als dies bei Intel und Qualcomm der Fall sein soll. Verglichen wird die grundsätzliche Funktionsweise von AMD aber mit CPU-Kernen, was sicherlich auch nicht dem entspricht, wie die NPUs anderer Hersteller funktionieren.

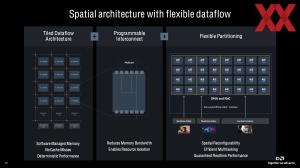

Einer der Punkte in der Beschreibung der XDNA-2-Architektur ist die Tatsache, dass AMD eine Custom-Compute-Hierarchie für die AI-Engines (AIE) entwickelt hat, die unter anderen auf programmierbare Interconnects setzt. KI-Berechnungen können auf einer gewissen Anzahl an AIEs ausgeführt werden. Dies können alle oder nur eine gewisse Anzahl an Spalten sein. AMD nennt dies spatiale Partitionierung, sodass gleichzeitig unterschiedliche Anwendungen auf der NPU laufen können – beispielsweise Realtime Audio/Video und ein LLM. Es ist aber auch weiterhin möglich, über eine temporale Partitionierung unterschiedliche Anwendungen nacheinander auszuführen, so wie dies auf anderen NPUs auch der Fall ist.

Damit die notwendigen Daten nicht zu jeder einzelnen AIE übertragen werden müssen, gibt es an den Knotenpunkten Switches im Interconnect, die mehrfach benötigten Daten kopieren können, so dass kein zweiter Speicherzugriff notwendig ist. Die AIEs können in Echtzeit auf anderen Aufgaben ausgelegt werden, sollte die vorherige abgeschlossen sein.

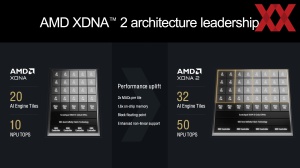

Um die höhere Rechenleistung zu erreichen, hat AMD aber auch die Anzahl der AIEs von 20 auf 32 erhöht. Zudem bekommt die NPU 60 % mehr Cache, zwei MACs pro AIE und weitere Verbesserungen. So steigt die Leistung von Phoenix mit 10 TOPS, über Hawk Point mit 16 TOPS auf nunmehr 50 TOPS. Um die Effizienz zu verbessern, können einzelne AIE-Spalter und sogar einzelne AIEs per Power Gating abgeschaltet werden.

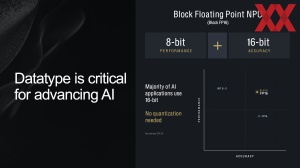

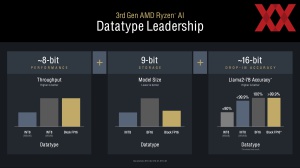

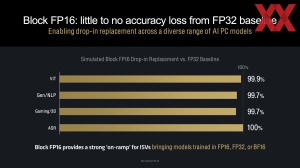

Ein wichtiger Baustein in der XDNA-2-Architektur ist auch ein neuer Datentyp, den AMD einführt. Block FP16 soll ab dem dritten Quartal als Drop-In-Möglichkeit für die Softwareentwickler zur Verfügung stehen. Der Vorteil in der Nutzung von Block FP16 besteht darin, dass dieser Datentyp die Leistung eines 8-Bit-Datentype (FP8, INT8) vorzuweisen hat, dabei aber fast die gleiche Genauigkeit wie ein 16-Bit-Datentyp (FP16, INT16) erreichen soll.

Fertigung in 4 und 3 nm

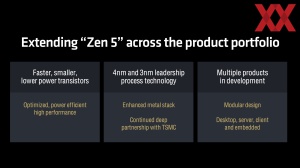

Die Zen-5-Architektur wird in den Ryzen-AI-300-, Ryzen-9000- und EPYC-Prozessoren zum Einsatz kommen. Bei den Ryzen-AI-300-Prozessoren geschieht dies in Form eines monolithischen Designs, während die Ryzen- und EPYC-Prozessoren wie gewohnt auf ein Chiplet-Design setzen.

Sowohl für die Ryzen-AI-300- wie auch Ryzen-9000-Prozessoren setzt AMD dabei auf eine Fertigung in 4 nm bei TSMC (N4P). Erwähnt wurden zudem einige Verbesserungen im Metall-Stack, wenngleich die Taktraten zumindest bei den Ryzen-9000-Prozessoren nicht groß ansteigen.

Interessant an dieser Stelle ist, dass AMD auch von Zen-5-Prozessoren in einer Fertigung in 3 nm spricht. Welche Chips dies sein werden, führte man aber nicht genauer aus. Möglich wäre, dass AMD für die CCDs mit Zen-5c-Kernen auf 3 nm setzt. Aber auch ein Custom-Design mit Zen-5-Kernen soll es geben. Aber auch dazu gab es auf dem Tech Day keinerlei weitere Informationen.

Ryzen-9000-Serie alias Granite Ridge

Eines der für Endkunden und vor allem unsere Leser sind sicherlich die Ryzen-9000-Prozessoren das wichtigste neue Produkt. Diese wurden bereits zur Computex vorgestellt. An den Basisdaten ändert sich nichts.

| Modell | Kerne / Threads | CCDs | max. Takt | L2-Cache | L3-Cache | Speicher | TDP |

|---|---|---|---|---|---|---|---|

| Ryzen 9 9950X | 16 / 32 | 2 | 5,7 GHz | 16x 1 MB | 2x 32 MB | DDR5-5600 | 170 W |

| Ryzen 9 9900X | 12 / 24 | 2 | 5,6 GHz | 12x 1 MB | 2x 32 MB | DDR5-5600 | 120 W |

| Ryzen 7 9700X | 8 / 16 | 1 | 5,5 GHz | 8x 1 MB | 32 MB | DDR5-5600 | 65 W |

| Ryzen 5 9600X | 6 / 12 | 1 | 5,4 GHz | 6x 1 MB | 32 MB | DDR5-5600 | 65 W |

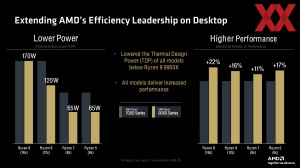

Das Gerücht, der Ryzen 7 9700X könnte von 65 auf 120 W heraufgestuft werden, hat sich nicht bestätigt. Im Grunde könnte man auch sagen, dass AMD den Eco-Mode nun für einige Modelle standardmäßig verwendet. Wie bereits in der Einführung erwähnt, werden die Ryzen-9000-Prozessoren am 31. Juli erscheinen. Einen Preis nennt AMD zum aktuellen Zeitpunkt aber immer noch nicht.

Ein paar weitere Details offenbarte AMD aber dennoch. So sollen die Ryzen-9000-Prozessoren über einen um 15 % geringeren Wärmewiderstand und 7 °C niedrigere Temperaturen bei gleicher TDP verfügen. Erreicht wird dies aber nicht durch Änderungen am Heatspreader oder dem Aufbau des Package, sondern über Änderungen am Floor Plan bzw. der Positioniert der Kerne um Hotspots zu vermeiden sowie eine bessere Positionierung der Temperatursensoren.

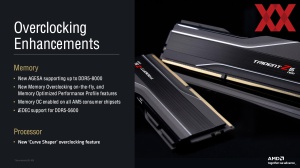

Zusammen mit den neuen Prozessoren erscheint auch eine neue AGESA-Version, die von den Mainboardherstellern größtenteils bereits ausgeliefert wurde. Mit dieser sollen unter anderem Speicher-Taktraten von bis zu 8.000 MT/s möglich sein.

Für das Overclocking der Prozessoren bleibt grundsätzlich alles beim Alten. Aber es gibt neue Speicherfunktionen, wie ein Speicher-Overclocking on-the-fly, so wie Intel dies auch bereits möglich macht. Über den Ryzen Master kann der Nutzer zwischen mehreren Profilen wechseln. Für Spiele beispielsweise niedrige Timings priorisieren und für Anwendungen die von hoher Speicherbandbreite eben einen höheren Takt. Abgelegt werden die Angaben in den Memory Optimized Performance Profilen. Theoretisch könnte AMD diese Funktion auch für die Ryzen-7000-Prozessoren möglich machen – es handelt sich um eine kleine Änderung in der Firmware. Ob AMD die Memory Optimized Performance Profiles nachreichen wird, ist nicht bekannt. Man sammelt nach eigenen Angaben noch Feedback.

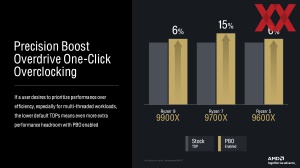

Eine neue Overclocking-Funktion ist der Curve Shaper. Dabei handelt es sich um eine Funktion, in der die Spannungs-Takt-Kurve besser angepasst werden kann. Auch PBO (Pression Boost Overdrive) kommt mit weiteren Verbesserungen. Für den Curve Shaper gilt genau wie bei den Memory Optimized Performance Profilen: Nur die Ryzen-9000-Prozessoren bieten zum Start Support, theoretisch könnte dies auch für den Vorgänger möglich machen.

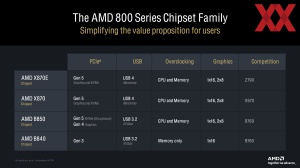

Die im September erwarteten Mainboards der 800-Serie und vor allem die mit X870E- und X870-Chipsatz sollen über ein verbessertes Routing der Leiterbahnen vom Sockel zu den DIMM-Steckplätzen verfügen. Damit sollen auch nochmals höhere Speichertakten möglich sein.

Die Mainboards mit B850-Chipsatz sind sozusagen die bessere Alternative zu den vorherigen A620-Boards. Auch hier ist ein CPU- und Speicher-Overclocking möglich. Bei Mainboards mit B840-Chipsatz bleibt nur noch das Speicher-OC übrig.

Bereits mehrfach wurde betont, dass AMD den Sockel AM5 bis mindestens 2027 unterstützen wird. Konkret sprach AMD auf dem Tech Day zu Zen 5 davon, dass die Zen-Generationen Zen 4, Zen 5, Zen 6 und Zen 7 unterstützen wird. Nach der Ryzen-9000-Serie werden also noch mindestens zwei Generationen folgen.

Entsprechend will AMD den AM5 auch für eine entsprechende Weiterentwicklung im Bereich des DDR-Speichers sowie der PCI-Express-Lanes ausgelegt haben.

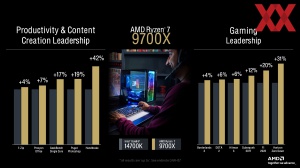

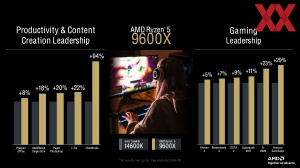

Kommen wir noch zu einigen Hersteller-Benchmarks: Am oder vor dem 31. Juli wird es dann die unabhängigen Tests geben. In den von AMD gezeigten Diagrammen liegt der Ryzen 9 9900X in Anwendungs- und Spiele-Leistung vor dem Core i9-14900K. Die Unterstützung von AVX-512 bietet vor allem in Anwendungen die davon Gebrauch machen, einen deutlichen Vorteil. Interessanterweise führt AMD hier "nur" den Ryzen 9 9900X an, der Ryzen 9 9950X dürfte noch einmal etwas schneller sein.

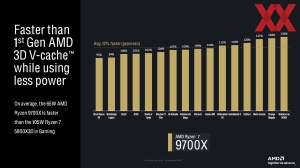

Für die weiteren Modelle gilt: Der Ryzen 7 9700X ist dem Core i7-14700K überlegen, der Ryzen 5 9600X dem Core i5-14600K. Einen seltsamen Vergleich macht AMD noch mit dem Ryzen 7 9700X, der gegenüber dem Ryzen 7 5800X3D im Schnitt 12 % schneller ist, es gibt aber wieder auch Spiele, die langsamer sind auf dem neuen Modell. Der Fokus seitens AMD liegt hier beim Umstand, dass der Ryzen 5 9700X mit 65 W auskommt, während es beim Ryzen 7 5800X3D 105 W sind.

Ryzen-AI-300-Serie alias Strix Point

Auch die Ryzen-AI-300-Prozessoren stellte AMD bereits zur Computex vor. Ein paar wenige weitere Details gibt es zum Zen 5 Tech Day.

| Modell | Kerne / Threads | Kern-Typ | Basis-Takt | Boost-Takt | Cache | TDP | cTDP | CUs |

|---|---|---|---|---|---|---|---|---|

| Ryzen AI 9 HX 370 | 12 / 24 | 4x Zen 5 8x Zen 5c | 2,0 GHz | 5,1 GHz | 36 MB | 28 W | 15 - 54 W | 16 |

| Ryzen AI 9 365 | 10 / 20 | 4x Zen 5 6x Zen 5c | 2,0 GHz | 5,0 GHz | 32 MB | 28 W | 15 - 54 W | 12 |

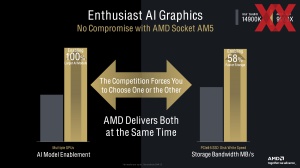

Strix Point besitzt als Zen-5- und Zen-5c-Kerne, die AMD in ein klassisches und kompaktes Cluster packt. AMD sprach auf dem Tech Day viel über AI – so wie aktuell wohl jedes Hard- und/oder Software-Unternehmen.

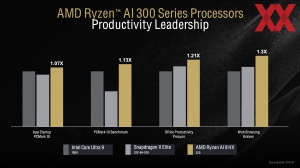

Aus diesem Grund sah sich AMD offenbar auch genötigt zu betonen, dass die CPU-Leistung nicht durch die AI-Leistung beeinflusst werden wird. Wie wir bereits in herstellereigenen Benchmarks und ersten Leaks gesehen haben, liegt die Leistung der integrierten GPU deutlich über der der Konkurrenz und auch dem eigenen Vorgänger.

Um die Effizienz weiter zu verbessern, wurde das Power Management Framework angepasst. Phoenix und Hawk Point waren noch mehr auf den höchstmöglichen Takt ausgelegt, während Strix Point hier anders herangeht. Es gibt mehr C-States (Active Power Down C-States C8 und C11), aber nicht zwangsläufig wird häufiger zwischen diesen gewechselt, denn ein Wechsel bedeutet auch immer, dass Ressourcen aufgewendet werden müssen.

Die NPU kann (sogar in weiteren Sub-Bereichen) abgeschaltet werden, ebenso einzelne CPU-Kerne und auch die Interconnects verbrauchen im Idle-Betrieb viel Strom, was man durch ein intelligentes Power-Management optimieren konnte. Weitere Details bleibt man allerdings auch hier schuldig.

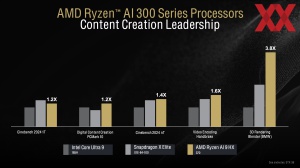

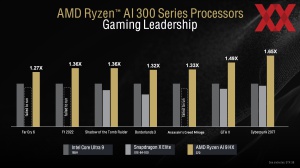

Auch zu den Ryzen-AI-300-Prozessoren liefert AMD eigene Benchmarks, die nur in Teilbereichen gegenüber den auf der Computex gezeigten Werten verändert wurde bzw. andere Hardware verwenden. Das Update auf nun bis zu zwölf Kerne hilft AMD natürlich in der Multi-Threaded-Leistung. Dank starker Zen-5-Architektur ist die Single-Threaded-Leistung ebenfalls auf hohem Niveau. Bereits angedeutet hat sich, dass die XDNA-3.5-Architektur in der Radeon 890M

AI sollte nicht alles sein ...

Dominiert wurde der Tech Day von einem Thema: AI. Groß verwundert hat uns das nicht, aber es war einmal mehr schade, wie weit die weiteren Themen in den Hintergrund gerückt sind. Vielmehr noch konnte man das Gefühl bekommen, selbst die Ryzen-9000-Prozessoren sind im Vergleich zur Ryzen-AI-300-Serie in den Hintergrund geschoben worden – dabei handelt es sich dabei um das Flaggschiff-Produkt in diesem Jahr, zumindest bis die X3D-Modelle erscheinen.

All das, was wir oben zur Zen-5- und RDNA-3.5-Architektur sowie den weiteren Details findet, ist keine Auswahl dessen, was AMD an Informationen geboten hat, sondern mehr gab es einfach nicht zu berichten. Bis zum Erscheinen der Ryzen-9000-Prozessoren erwarten wir uns bis auf den Preis auch keine weiteren Details. Zumindest aber können wir dann eigene Erkenntnisse gewinnen, wie zum Beispiel das Verhalten mit schnellem Arbeitsspeicher sein wird und welche Auswirkungen die neue TDP-Klassifizierung auf den Vergleich zu Intel hat.