Werbung

Auf dem Technology Symposium in Nordamerika (via Anandtech) hat TSMC über die aktuelle Entwicklung und die Pläne hinsichtlich seiner N2-Familie, also der Fertigung in 2 nm, gesprochen. Die Varianten der N2-Fertigung sollen 2025 bzw. 2026 die ersten fertigen Chips abwerfen. Bisher hatte TSMC nur seine N3-Familie detaillierter ausgeführt, während die Fertigung in N2 noch mehr oder weniger nur ein Ausblick war.

Für die gesamte N2-Familie versprach TSMC bereits vor einem Jahr deutliche Verbesserungen in der Leistung und dem Stromverbrauch. N2 wird auch der erste Fertigungsschritt sein, der auf Gate-All-Around-Transistoren (GAAFET) setzt, die bei TSMC als Nanosheet bezeichnet werden.

Die Ziele für die Fertigung in N2 wurden bereits letztes Jahr genannt und können zum aktuellen Zeitpunkt auch eingehalten werden. Bei gleicher Leistungsaufnahme soll ein Chip um 10 bis 15 % schneller werden im Vergleich zu N3E-Fertigung. Bei gleicher Leistung soll die Leistungsaufnahme um 25 bis 30 % geringer ausfallen und die Transistordichte steigt um etwa 15 %.

Testchips erreichen aktuell 80 % oder mehr der anvisierten Leistung. 256 MB SRAM-Testchips haben eine Ausbeute von 50 % oder mehr. Laut diesen Daten soll die Fertigung in N2 bereit für die Massenproduktion in 2025 sein.

Neben der Nennung einiger wichtiger Parameter für die N2-Familie gibt TSMC auch erste Details zu den verschiedenen Varianten bekannt, die es auch innerhalb der N7-, N5- und N3-Familie gab, gibt und geben wird. Mit der Fertigung in N2 steht für TSMC der Schritt hin zu den GAA-Transistoren an. N2P wird zudem die Backside Power Delivery (BPD) erhalten. Damit sollen die Bereiche der Strom- und Spannungsversorgung der Transistoren von den Bereichen der Signalleitungen getrennt werden. Bei Intel wird dieser Schritt mit Intel 20A erfolgen und nennt sich dort PowerVia. Die geringeren Interferenzen sollen einerseits zu einer höheren Leistung der Transistoren sorgen und andererseits auch deren Leistungsaufnahme durch die dedizierte Versorgung erhöhen.

Neben diesen Vorteilen soll die Neupositionierung der Power Delivery Networks (PDN) auf die Rückseite auch dabei helfen, die Tranistordichte weiter zu erhöhen. Die Fertigung in N2P soll ab 2026 zur Verfügung stehen.

Für zukünftige HPC-Chips sieht TSMC erneut eine spezielle Fertigung vor. Die Fertigung in N2X soll ebenfalls ab 2026 zur Verfügung stehen und richtet sich an Chips bzw. Auftraggeber, deren Chips hohe Spannungen und ebenso hohe Frequenzen verkraften können sollen. Genau wie zu N2P gibt es auch zu N2X noch keiner weiteren Details.

Aktuell ist TSMC der führende Auftragsfertiger, der für die meisten Produktkategorien und gerade in den kleineren Fertigungsschritten die Nase vorne hat. Alle großen Chiphersteller lassen ihre Chips bei TSMC fertigen, selbst Intel tut dies für seine GPUs und auch einige der aktuellen und zukünftigen Chiplets. Diese Vorreiterrolle will man sicherlich auch behalten und entsprechend ambitioniert sind die Pläne.

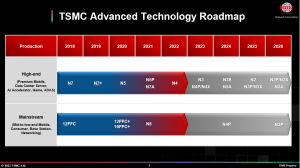

Die Roadmap für Mainstream- und High-End-Produkte ist prall gefüllt und scheinbar ist man sehr gut aufgestellt – wenn die Pläne denn auch so aufgehen, wie man sich das vorstellt.

Brand in Packaging-Fabrik

Nicht mit dem Symposium verknüpft, aber sicherlich auch nicht ohne Auswirkungen auf die Auslieferungen bei TSMC ist ein Brand in einer Packaging-Fabrik (Advanced Chip Packaging & Testing Plant (No. 6) im Zhunan Science Park), wie Yahoo in Taiwan (via Dan Nystedt) meldet. Verletzte soll es keine gegen haben, aber 300 m² an Fabrikfläche sollen durch das Feuer beschädigt worden sein.

In solchen Fabriken bringt TSMC die Chips in ihre Packages, was im Falle einer GH100-GPU oder sonstiger High-End-Chips ein aufwendiger Prozess ist. Wie viele Chips bzw. deren Auslieferung vom Feuer betroffen sind, ist nicht bekannt. Die Auswirkungen bei der aktuell hohen Nachfrage an AI-Chips sind nicht bekannt.