Werbung

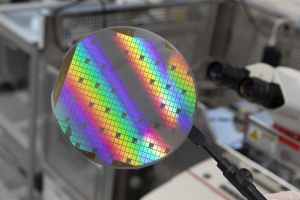

Der taiwanesische Halbleiterhersteller United Microelectronics Corporation (UMC) kündigt für das kommende Jahr ein neues Packaging-Verfahren an, mit dem man ein Stück des aktuellen Bedarfs nach Packaging-Kapazitäten abhaben möchte. Bei W2W 3D IC handelt es sich um ein Wafer-auf-Wafer-Verfahren, bei dem mehrere Chips übereinander gestapelt werden können. Partner sind Winbond, Faraday, ASE und Cadence.

Zielmarkt für UMC dürften Produkte sein, bei denen ein oder mehrere Speicherchip auf einem Prozessor oder SoC aufgebracht werden. Mit Cadence hat man einen IP-Partner dazu gefunden, ASE ist ein Dienstleister für die Vereinzelung der Chips.

Marktführer in Packaging-Technologien ist TSMC. Hier ist auch einer der größten Flaschenhälse zu suchen, der aktuell in der Chipfertigung vorhanden ist. Alle großen KI-Beschleuniger werden aktuell bei TSMC gefertigt und/oder das Packaging findet hier statt. Ausnahmen sind Intels Ponte-Vecchio-Beschleuniger. Entsprechend baut TSMC seine Kapazitäten weiter aus. Auch Intel sieht im Packaging einen gigantischen Markt und baut seine größeren Kapazitäten für die eigenen Produkte und zukünftig auch Foundry-Kunden gerade aus.