Werbung

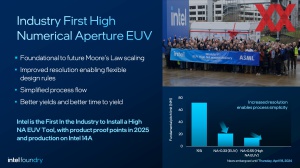

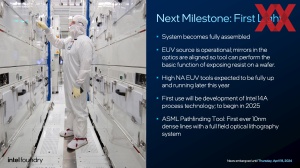

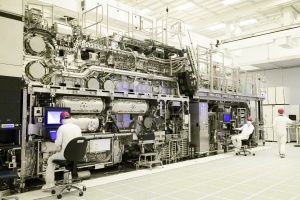

Im Dezember hat Intel den ersten High-NA-EUV-Scanner von ASML erhalten. Dieser steht nun in der Fab D1X im US-Bundesstaat Oregon und wird in den kommenden Monaten vom niederländischen Unternehmen so eingerichtet, dass Intel damit Anfang 2025 damit beginnen kann, die eigenen Prozesse darauf abzubilden. Im Verlaufe des kommenden Jahres will man dann die wichtigsten Prüfpunkte erreichen, die eine Massenproduktion am 2026 zulassen.

In Oregon werden die neuen Technologien entwickelt und dann in die weltweiten Fabs überführt – seien es die Fertigung der Wafer oder Techniken für das Packaging. Zuletzt geschah dies mit Intel 4 in der Fab 34 in Irland. So geht Intel mit allen neuen Technologien vor, denn in Hillsboro in Oregon sitzt das DT-Team (Technology Development). Die ersten Meteor-Lake-Prozessoren wurden noch in Oregon per Foveros auf ein entsprechendes Packaging gebracht, die Chips selbst kamen ebenfalls aus Oregon und Irland sowie Taiwan. Inzwischen dürften die Chips in der neuen Fab in New Mexico als Foveros-Package verarbeitet werden. Das finale Packaging findet dann in Malaysia statt.

High-NA EUV (eine genaue Erläuterung, was sich dahinter verbirgt, folgt noch) ist seit mehr als zehn Jahren bei Intel in der Entwicklung. Vor 26 Jahren wurde die Möglichkeit der technischen Umsetzung einer solchen Belichtungstechnik erstmals erwähnt. Man erkennt hier also recht schnell, auf welchem Level der technischen Entwicklung sich die beteiligten Unternehmen bewegen.

Für Intel wird High-NA EUV ab 2025/26 ein wichtiger Baustein in der Fertigung sein. Intel 14A wird als erster Prozess darauf setzen, alle darauffolgenden Prozesse ebenso. Aber wie auch schon bei 0,33 NA EUV wird es einen fließenden Übergang geben. Von den 15 Metalllayern, die beispielsweise für eine Fertigung in Intel 4 zum Einsatz kommen, werden nur die untersten vier bis fünf Lagen überhaupt mittels EUV belichtet. Für den Rest kommt weiterhin DUV zum Einsatz. Ähnlich wird es sich mit High-NA EUV verhalten. Auch hier wird Intel nicht alle Layer in der neuen Technik belichten, sondern sich zunächst auf die wichtigsten Layer konzentrieren, was auch ein Mittel der Risikominimierung ist.

Ein wichtiger Faktor beim Einsatz von High-NA EUV werden die Kosten sein. Die Scanner sind extrem teuer und kosten mehrere hundert Millionen Euro. Um die Kosten zumindest etwas im Rahmen zu halten, können die Scanner teilweise Komponenten der vorherigen Generation verwenden. So ist die Lichtquelle mit dem ultravioletten Licht mit einer Wellenlänge von 13,5 nm weiterhin identisch.

Dabei ist die technische Umsetzung einer solchen Lichtquelle bereits ein technologisches Wunderwerk. Das Licht mit einer Wellenlänge von 13,5 nm wird nicht einfach durch eine Lichtquelle erzeugt, sondern mittels eines Lasers, der Tropfen aus flüssigem Zinn jeweils zweimal beschießt – einmal, um aus der Tropfenform eine flache Scheibe zu machen, und einen zweiten Schuss, um das Zinn zu ionisieren – aus dem dann ein Plasma entsteht. Dies geschieht 50.000 mal pro Sekunde. Ein Kollektorspiegel fängt die vom Plasma in alle Richtungen emittierte EUV-Strahlung ein, bündelt sie und übergibt sie schließlich an das Lithografiesystem (wie den Twinscan von ASML) zur Belichtung des Wafers. Die verwendeten Laser kommen von TRUMPF aus Deutschland.

Wiederum eine Neuentwicklung sind die Spiegel in den High-NA-Scannern. Er bedarf einer besonderen Güte. Der von ZEISS entwickelte Spiegel hat einen Durchmesser von 1 m. Die maximale Rauheit von 20 pm (Pikometer, 1012) darf dabei nicht überschritten werden. Die höchste Erhebung auf dem Spiegel ist damit auf die Größe der Erde hochgerechnet so, als seien die höchsten Berge nicht einmal einen Meter hoch.

Dies sind nur zwei Punkte, welche die technischen Herausforderungen in der Belichtung von Halbleiterbauelementen unterstreichen sollen.

Die ersten Versuchsanlagen laufen unter dem Produktnamen TWINSCAN NXE:5000. Die Produktivsysteme werden dann als TWINSCAN NXE:5200 vermutlich einen Wafer-Output von 220 Wafer pro Stunde haben, was auf Niveau dessen liegt, was auch die schnellsten 0,33-NA-EUV-Scanner wie der neue TWINSCAN NXE:3800E liefern können. Die Effizienz wird also deutlich höher sein, als dies damals beim Wechsel auf 0,33 NA EUV der Fall war.

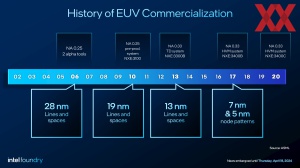

Von den ersten Alpha-Tools bis zur heutigen Fertigung mittels EUV sind mehr als 15 Jahre vergangen. In dieser Zeit hat sich die Produktivität und Effizienz der EUV-Systeme deutlich verbessert. Für High-NA EUV erwartet Intel einen schnelleren und flüssigeren Übergang – auch weil einige Komponenten der Scanner übernommen werden können und damit bereits ausreichend erprobt sind.

Mit dieser heutigen Ankündigung seitens Intel sei auch noch einmal auf die gestrige Meldung verwiesen, in der ASML die erfolgreiche Belichtung von dichten Strukturen mit einem Abstand von 10 nm verkündet hat. Die Belichtung erfolgte, nachdem Optik, Sensoren und Tische auf denen die Wafer bewegt werden, grob kalibriert worden waren. In den weiteren Schritten wird das System nun immer weiter kalibriert und optimiert, bis auch Logikstrukturen belichtet werden können.

Vor- und Nachteile von High-NA EUV

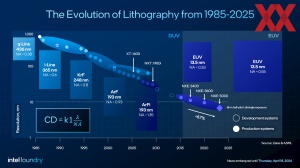

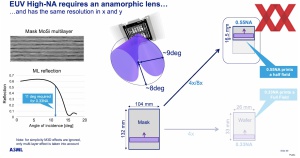

High-NA steht für High Numerical Aperture und diese numerische Apertur wiederum ist ein Indikator für den Öffnungswinkel des optischen Systems sowie des Brechungsindex des Mediums. Je größer die numerische Apertur, desto mehr Licht kann über eine Projektion abgegeben werden und desto höher das erzielbare Auflösungsvermögen. Die ersten EUV-Systeme setzten auf eine numerisch Aperture von 0,25, dann erfolgte der Wechsel auf die aktuell verwendeten 0,33. High-NA ist gleichbedeutend mit einer numerischen Aperture von 0,55.

Der Einsatz von High-NA EUV wird also vor allem notwendig, weil sich damit kleinere Strukturen abbilden lassen. Für 0,33 NA EUV ist bei etwa 10 nm das Ende der Fahnenstange erreicht. Nur noch über ein Multi-Patterning (Wikipedia dazu), können kleinere Strukturen realisiert werden. Mit High-NA EUV sollen nun 8 nm mit einer Belichtung möglich sein.

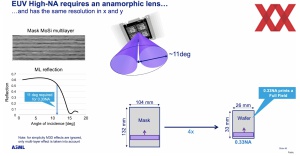

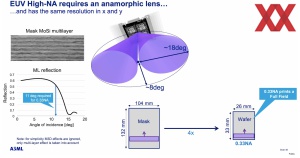

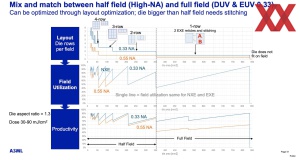

Die hohe numerische Aperture sorgt aber auch dafür, dass die Fläche pro Belichtungsvorgang halbiert wird. Begründet ist dies durch den Aufbau der Belichtungs-Masken. Jede EUV-Maske besteht aus einem mehrschichtigen Stapel an Schichten (MoSI, Monosilizium-Multilayer) und diese verursachen Reflexionen. Diese sind je nach Einfallswinkel unterschiedlich groß. Ein Einfallswinkel von mehr als 10° ist bei 0,33 NA nicht möglich. Wenn die Blende für HighNA nun vergrößert wird, ist dies mit der sonst üblichen vollen Abdeckung nicht möglich, da der Einfallswinkel 18° betragen würde. Also hat ASML zusammen mit Zeiss eine anamorphe Linse entwickelt, die es erlaubt, unter 10° zu bleiben. Dies hat dann jedoch zur Folge, dass man für die typischen 6"-Masken keine Vollfeld-Belichtung (Full Field) mehr vornehmen kann, sondern auf halbe Felder (Half Field) gehen muss.

Das unten via Twitter eingebettete Video zeigt wie schnell das Wafer-Modul sich für eine Halbfeld-Belichtung bewegen muss um 220 Wafer pro Stunde einhalten zu können.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Das Rectile-Limit, also die maximale Größe der Chips, die gefertigt werden können, wird damit von 26 x 33 mm (858 mm²) auf 26 x 16,5 mm (429 mm²) halbiert. Soll ein Chip größer als diese 429 mm² sein, muss ein sogenanntes Stiching angewendet werden. Dabei werden die beiden Hälften des Chips getrennt voneinander belichtet und sozusagen zusammengesetzt. Das Stiching kann aber fehleranfällig sein und reduziert die Ausbeute.

Die technischen Voraussetzungen für eine Fertigung mittels High-NA EUV liegen nun wie oben beschrieben vor. Nun liegt es an Intel, daraus einen oder mehrere funktionierende Prozesse zu entwickeln. Ein Großteil der Fertigung wird aber noch eine lange Zeit mittels 0,33 NA erfolgen, was auch für den Umstand gilt, dass vor allem Logikelemente im Chip von der Skalierung der Auflösung profitieren, während dies für analoge Komponenten und Speicher nicht der Fall ist. In den kommenden Jahren werden die DRAM-Hersteller erst damit beginnen EUV für ihre Fertigung einzusetzen. High-NA EUV wird den fortschrittlichsten Fertigungsprozessen vorbehalten bleiben.

In den Forschungs- und Entwicklungsabteilungen der Unternehmen und Institute wird schon über das gesprochen, was nach High-NA EUV kommen soll: Hyper-NA mit 0,75 NA. Bei ZEISS zeigt man sich zuversichtlich, dass die Herausforderungen hinsichtlich der Optiken gemeistert werden können. Das was man bei 0,55 NA gelernt hat, soll auch bei 0,75 NA zum Einsatz kommen. Es werden aber noch mindestens zehn Jahre vergehen, bis Hyper-NA EUV zu einem spruchreifen Thema wird.