Werbung

Fertigung der Chips, der HBM, der Interposer und das Packaging – all dies sind aktuell mögliche Bremsklötze in der Fertigung der KI-Beschleuniger. Während am Ausbau der Kapazitäten für die Chips, den HBM und das Packaging gearbeitet wird, scheint die Verfügbarkeit an ausreichenden Interposer-Stückzahlen nun zum Problem zu werden.

Die Herstellung der Interposer klingt auf den ersten Blick trivial, da sie recht einfach strukturiert sind. Die Größe ist jedoch das Problem, denn inzwischen werden bei mehreren Compute-Chiplets und den dazugehörigen HBM-Chips Flächen von 2.000 bis 3.000 mm² erreicht. Da auch der Interposer klassisch auf einem Wafer hergestellt wird, ergeben sich bei einer Größe von 40 x 50 mm und bis zu 50 x 60 mm vielleicht zwei Dutzend Interposer pro 300-mm-Wafer, in Richtung 3.000 mm² sogar nur 12 bis 16 Interposer pro Wafer. Von den eigentlichen Chips mit einer maximalen Größe von 26 x 33 mm (858 mm² sind zugleich das Reticle Limit) können per perfekter Ausbeute etwa 62 Chips pro Wafer hergestellt werden. Einen perfekten Prozess gibt es allerdings nicht und so ergibt sich aus Fehlern in der Fertigung eine geringere Ausbeute – sowohl bei den Chips als auch dem Interposer.

Einer der größten Hersteller für Interposer ist das taiwanesische Unternehmen UMC (United Microelectronics Corporation). Auch TSMC greift auf diese Kapazitäten zurück, wird aber auch selbst Interposer fertigen. Laut den Kollegen von Computerbase lagert TSMC einen Teil seiner Interpower- und Packaging-Kapazitäten für CoWoS (Chips on Wafer on Substrat) an UMC, Amkor und SPLI aus.

Die Kollegen verweisen zudem darauf, dass UMC im letzten Jahr 3.000 Wafern im Monat für Silicon Interposer herstellen konnte. Zu Jahresbeginn soll die Kapazität auf 6.000 Wafer pro Monat verdoppelt worden sein. Bis Jahresende sollen es 10.000 Wafer im Monat werden. Ob dies ausreichen wird, um den Bedarf zu decken, ist nicht bekannt.

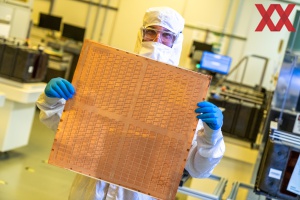

Die Fertigung großer rechteckiger Chips auf einem runden Wafer hat zudem das Problem, dass im Randbereich der Verschnitt immer größer wird. Wie Nikkei Asia nun erfahren haben will, arbeitet TSMC an neuen Trägermaterialien zur Herstellung der Silicon Interposer. Die Rede ist von ersten Studien dazu, man ist also noch weit davon entfernt, hier einen fertigen Prozess verwenden zu können. Rechteckigen Substratträger mit Abmessungen von 510 x 515 mm sollen zum Einsatz kommen – deutlich größer als die heute üblichen runden Wafer mit einem Durchmesser von 300 mm. Auf den größeren rechteckigen Substraten ließen sich nicht nur mehr, sondern auch größere Interposer herstellen.

Wie aber TSMC ein rechteckiges Trägermaterial für Interposer fertigen will, ist nicht bekannt. Für die Wafer-Herstellung wird der Einkristall gezüchtet und ist daher rund. Hier fehlt es einfach an weiteren Details. Das Format erinnert an die Glassubstrate, die Intel vor einem halben Jahr erstmals zeigte (siehe Bild oben). Auch diese werden auf einem rechteckigen Träger hergestellt.

Klar ist nur eines: Die Chiplet-Designs benötigen einen Interposer, auf dem die Chips aufgebracht werden können. Mit immer größeren Compute-Chiplets nebst HBM müssen auch die Interposer wachsen. Die Blackwell-GPU setzt beispielsweise auf zwei Compute-Chiplets und acht HBM-Chips. Über den Daumen benötigen diese Chips eine Fläche von 2x 800 mm² + 8x 100 mm² für den HBM – sprich 2.400 mm². In Zukunft dürften die Interposer noch weitaus größer werden.

Warum keine Wafer mit 450 mm Durchmesser?

Geforscht wurde außerdem an Wafern mit einem größeren Durchmesser. 450 mm sollen es dann sein. Die Anzahl der Chips pro Wafer würde sich dramatisch erhöhen, ohne Frage.

Das Problem ist aber, dass sämtliches aktuelles Equipment umgestellt werden muss. Dies beginnt bei der Herstellung der Silizium-Kristalle, über deren Verarbeitung zum Wafer, bis hin zu den Belichtungsmaschinen in der Fertigung. Nach der Belichtung muss der Wafer ebenfalls noch verarbeitet werden können, um die Chips zu vereinzeln. Die Technik zum Transport der Wafer, sowohl innerhalb als auch außerhalb der Fabriken, ist ebenso nicht auf größere Wafer ausgelegt. In anderen Bereichen, wie den Chips für Leistungselektronik, arbeitet man sogar mit Wafern mit einem Durchmesser von nur 200 mm.

So einfach auf 450 mm zu gehen, ist also nicht möglich. Die Lieferkette müsste von A bis Z umgestellt werden. Auch technische Hürden wie ein verändertes mechanisches Verhalten der größerem Wafer gibt es.