News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Interposer

-

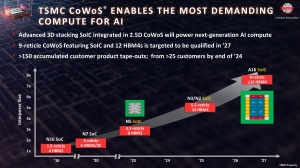

Interposer mit 12x HBM4: TSMC CoWoS soll ab 2027 riesige Packages ermöglichen

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann. In... [mehr]

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann. In... [mehr] -

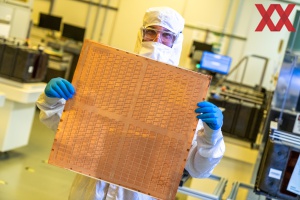

Immer größere Interposer: TSMC soll an rechteckigen Substrat-Trägern arbeiten

Fertigung der Chips, der HBM, der Interposer und das Packaging – all dies sind aktuell mögliche Bremsklötze in der Fertigung der KI-Beschleuniger. Während am Ausbau der Kapazitäten für die Chips, den HBM und das Packaging gearbeitet wird, scheint die Verfügbarkeit an ausreichenden Interposer-Stückzahlen nun zum Problem zu werden. Die Herstellung der Interposer klingt auf den ersten Blick trivial, da sie recht einfach strukturiert sind. Die... [mehr]

Fertigung der Chips, der HBM, der Interposer und das Packaging – all dies sind aktuell mögliche Bremsklötze in der Fertigung der KI-Beschleuniger. Während am Ausbau der Kapazitäten für die Chips, den HBM und das Packaging gearbeitet wird, scheint die Verfügbarkeit an ausreichenden Interposer-Stückzahlen nun zum Problem zu werden. Die Herstellung der Interposer klingt auf den ersten Blick trivial, da sie recht einfach strukturiert sind. Die... [mehr] -

Die-Shots der GP100-GPU, dem Interposer und HBM2

Bereits 2016 präsentierte uns FritzchenFritz Die-Shots der Fiji-GPU von AMD – mitsamt Interposer und HBM. Eine defekte Tesla P100 sorgt nun dafür, dass wir die entsprechende GP100-GPU ebenfalls in schicken Bildern präsentiert bekommen. Die in 16 nm bei TSMC gefertigte GPU kommt auf 3.840 Shadereinheiten und misst 22,499 x 27,471 mm = 618,070 mm². Der Interposer, auf dem die GPU sitzt, verbindet die GPU mit den vier HBM2-Chips –... [mehr]

Bereits 2016 präsentierte uns FritzchenFritz Die-Shots der Fiji-GPU von AMD – mitsamt Interposer und HBM. Eine defekte Tesla P100 sorgt nun dafür, dass wir die entsprechende GP100-GPU ebenfalls in schicken Bildern präsentiert bekommen. Die in 16 nm bei TSMC gefertigte GPU kommt auf 3.840 Shadereinheiten und misst 22,499 x 27,471 mm = 618,070 mm². Der Interposer, auf dem die GPU sitzt, verbindet die GPU mit den vier HBM2-Chips –... [mehr] -

Samsung I-Cube4: Chiplets auf dünnem Interposer werden effizienter

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an. Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von... [mehr]

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an. Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von... [mehr] -

CoWoS: TSMCs 1.700-mm²-Interposer nimmt 5-nm-Chips auf

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM... [mehr]

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM... [mehr] -

AMD forscht an aktivem Interposer als EMIB-Gegenstück

Große monolithische Chips sind aufgrund der komplizierten Fertigung zunehmend ein Problem für die Hersteller. AMD hat seine Zen-Architektur auf einzelne Zeppelin-Dies ausgelegt, die einfach mehrfach verwendet werden können - ein Die für die Ryzen-Prozessoren, zwei und bald vier aktive Dies für Ryzen Threadripper und vier Dies für die EPYC-Prozessoren. Intel hat mit der Embedded Multi-die Interconnect Bridge (EMIB) eine Technik in... [mehr]

Große monolithische Chips sind aufgrund der komplizierten Fertigung zunehmend ein Problem für die Hersteller. AMD hat seine Zen-Architektur auf einzelne Zeppelin-Dies ausgelegt, die einfach mehrfach verwendet werden können - ein Die für die Ryzen-Prozessoren, zwei und bald vier aktive Dies für Ryzen Threadripper und vier Dies für die EPYC-Prozessoren. Intel hat mit der Embedded Multi-die Interconnect Bridge (EMIB) eine Technik in... [mehr] -

AMD verwendet unterschiede GPU-Packages für Radeon RX Vega (Update)

Neben der noch immer anhaltenden Diskussion rund um die Leistung der Radeon RX Vega 64 und Vega 56 sowie um die derzeitige Preissituation gibt es weitere technische Erkenntnisse, die offenbar keinerlei Auswirkungen auf die Karten selbst haben, aber aus technischer Sicht interessant sind. Hardware.info aus den Niederlanden hat herausgefunden, dass es zwei unterschiedliche Ausführungen der Vega-10-GPU auf den beiden Karten gibt. Diese... [mehr]

Neben der noch immer anhaltenden Diskussion rund um die Leistung der Radeon RX Vega 64 und Vega 56 sowie um die derzeitige Preissituation gibt es weitere technische Erkenntnisse, die offenbar keinerlei Auswirkungen auf die Karten selbst haben, aber aus technischer Sicht interessant sind. Hardware.info aus den Niederlanden hat herausgefunden, dass es zwei unterschiedliche Ausführungen der Vega-10-GPU auf den beiden Karten gibt. Diese... [mehr]