Werbung

Im Vorfeld der Direct Connect 2025 Ende April und der Vision 2025 in wenigen Tagen, auf der Lip-Bu Tan als neuer CEO erstmals eine Keynote abhalten wird, hat Intel erneut seine Bereitschaft bekräftigt, für externe Kunden ein Advanced System Assembly & Test übernehmen zu können. Das Foundry-Segment von Intel wird seit Monaten und Jahren nicht müde, immer wieder darauf zu verweisen, dass man offen für externe Kunden sei. Die Auftrennung in Intel Products und Intel Foundry soll sicherstellen, dass mögliche Kunden dabei keinerlei Technologietransfer zu befürchten haben und dies soll auch einen Interessenskonflikt für Intel vermeiden.

Im vergangenen Frühjahr zeichnete Intel ein relativ komplettes Bild im Foundry-Bereich: Unter anderem der Erfolg der Fertigung in Intel 18A schwebt wie ein Damoklesschwert über der Zukunft des Chipriesen, dessen Aufteilung und teilweise Verkauf seit Monaten immer wieder gehandelt wird. Mit Lip-Bu Tan will Intel nun jedoch zunächst einmal für eine gewisse Beständigkeit sorgen.

Die Hauptargumente für die Beurteilung einer Chipfertigung sind sicherlich PPA (Performance, Power, Area) sowie die Kosten. Hinzu kommt in den vergangenen Jahren zunehmend eine geopolitische Diversität, die sichere Lieferketten ermöglichen soll. Diese Diversität sorgt unter anderem dafür, dass TSMC insgesamt 165 Milliarden US-Dollar in den Fab-21-Komplex im US-Bundesstaat Arizona stecken möchte. Intel hingegen will Ohio One als bisher größtes Einzelprojekt in der Chipfertigung bei Intel mit 2030 deutlich verzögert angehen.

Advanced Packaging rückt in den Fokus

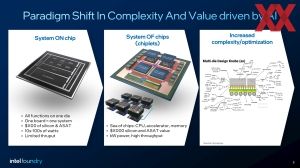

Doch auch wenn sich vieles immer wieder auf die Chipfertigung selbst konzentriert, so kommt dem Advanced Packaging eine immer wichtigere Rolle zu und das nicht erst in den vergangenen Monaten. Nicht nur technische eine Herausforderung, sondern auch in den Stückzahlen limitiert ist ein Wafer-Level Adanced Packaging, wie es TSMC als CoWoS anbietet. Hier kommt nun Intel ins Spiel.

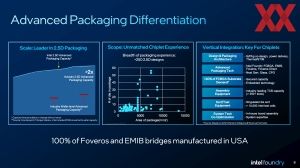

Intel wendet die eigenen Packaging-Kapazitäten für die eigenen Produkte an. Mit FCBGA 2D und FCBGA 2D+ sind Verfahren, in denen Intel mit fast 40 % der weltweiten Kapazität führend ist. Eben diese Formen des "einfachen" Packaging werden für die breite Mase an Chips verwendet – sowohl im Endkunden- als auch im Server-Segment.

EMIB und Foveros sind die fortschrittlicheren Verfahren, für die Intel in den vergangenen Jahren Kapazitäten aufgebaut und die man selbst seit 2017 ab Kaby Lake-G zum Einsatz gebracht hat. Lakefield, Sapphire Rapids, Meteor Lake, Arrow Lake, Sierra Forest, Granite Rapids und viele darauffolgende sowie aktuelle Prozessoren verwenden EMIB und Foveros in den verschiedenen Ausbaustufen.

In Anbetracht der Komplexität der kommenden KI-Beschleuniger rücken EMIB 3.5D und Foveros Direct 3D in den Fokus. Hier sind Intel das größte Potential ein attraktiver Auftragsfertiger für externe Kunden zu sein.

Aktuell aber noch setzen die meisten Hersteller der KI-Beschleuniger auf ein theoretisch relativ einfaches Verfahren, bzw. auf eine geringe Komplexitätsdichte. Ein oder zwei GPUs werden mit bis zu acht HBM-Stacks kombiniert. Hierzu sieht Intel EMIB 2.5D vor, während AMD und NVIDIA bei TSMC auf ein CoWoS-Verfahren setzen. Das Verfahren der Silicon Interposer, Fan-Out Bridge, RDL Interposer – oder wie auch immer man es bezeichnen möchte – ist laut Intel kostspielig, hat beträchtliche Laufzeiten in der Fertigung, Nachteile in der Ausbeute sowie weitere Negativaspekte.

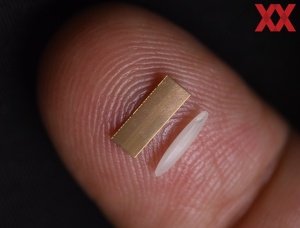

In zwei Bereiche aufgeschlüsselt bedeutet dies: Die EMIB-Bridge ist ein je nach Ausführung ein etwa Reiskorn großer Chip, von dem sich hunderte, wenn nicht tausende auf einem Wafer produzieren lassen. Die Wafer- und Chipausbeute ist dabei extrem hoch. Anders sieht dies bei einem Silicon Interposer aus, da die Fläche etwas größer sein muss, als die Summe der Chips, die man miteinander verbinden will. Ein Interposer mit 5.000 mm² oder mehr reduziert die nutzbare Fläche des Wafers natürlich deutlich. Dies wirkt sich vor allem auf die Kosten aus.

Zudem ist ein Wafer Level Assembly notwendig. Der Wafer mit den Compute-Chips und der Wafer mit dem Silicon Interposer müssen zusammengebracht werden. Dieser Schritt in der Fertigung ist aufwändig und fehleranfällig. TSMC hat den Prozess inzwischen im Griff und kann eine hohe Ausbeute garantieren, dennoch handelt es sich um einen zusätzlichen Fertigungsschritt.

Neben der Expertise, den notwendigen Kapazitäten und dem Kostenvorteil sieht Intel aber auch einen Vorteil durch die Tatsache, dass das Packaging mittels EMIB wie auch Foveros zu 100 % in den USA erfolgt. TSMC mag Chips mit einer Strukturbreite von 4 nm in den USA fertigen können, das Packaging findet jedoch weiterhin in Taiwan statt. Somit könnten geopolitische Herausforderungen noch immer dazu führen, dass NVIDIA zwar in den USA seine Blackwell-Chips bei TSMC herstellen lassen kann (was teilweise bereits der Fall ist), für das Packaging müssen diese Chips allerdings weitehrin nach Taiwan reisen. TSMC will mit dem Erhalt der neusten Fertigungstechniken im Heimatland sicherstellen, dass das Silicon Shield weiterhin Bestand hat.

Die Sort als weitere Stärke

Aber auch in einem weiteren Punkt sieht sich Intel gut aufgestellt. Bevor ein Chip mit anderen zusammengebracht wird, muss sichergestellt werden, dass diese all ihre Funktion erfüllen. Ist dies auch nur für einen der Chips in einem Package nicht der Fall, kann dieses entweder komplett ausfallen oder nicht im vollem Umfang genutzt werden. Dann sind selbst die intakten Chips im schlimmsten Fall wertlos.

Die Sort ist hier das Stichwort und bei unserem Besuch der Packaging-Werke von Intel in Malaysia haben wir einen Eindruck davon bekommen, was Intel hier leisten kann.

Nach der Vereinzelung der Chips vom Wafer kommen diese in einen SDX-Tester, wo jeder einzelne Chip auf eine Probing Card gesetzt wird. Diese besitzt bis zu 20.000 feine Probing-Nadeln, die Kontakt mit dem Chip aufnehmen. Die Abstände der Nadeln können durchaus ein Niveau erreichen, welches für die Abstände der Interconnects infrage kommt.

In der Sortieranlage findet noch kein Binning statt. Über das Testen jedes einzelnen Chips stellt Intel bereits an dieser Stelle sicher, dass nur funktionsfähige und solche, die alle vorher definierten Spezifikationen erfüllen, in das Packaging gehen. Auch dies sieht Intel als Stärke des eigenen Foundry-Angebotes.

Allerdings ist Intel nicht das einzige Unternehmen, welches ein OSAT (Outsourced Semiconductor Assembly and Test) zur Verfügung stellen kann. Wie sich die Angebote im Umfang genau unterscheiden, können wir nicht abschätzen. Das Testing bei Intel scheint auf einem recht hohen Niveau zu sein, wenngleich modernste Chips von NVIDIA und Apple, die bei TSMC vom Band gelaufen sind, bei TSMC selbst und eventuell auch externen OSAT-Unternehmen ebenfalls bis aufs Detail geprüft werden. Bei einem Wafer Level Assembly sind die Voraussetzungen natürlich andere.

Intel macht sich an potenzielle Kunden

Intel will externe Kunden für sich gewinnen – nicht nur für die Fertigung der Chips selbst, sondern auch für das Packaging. Dies wurde bereits im vergangenen Jahr deutlich und wird nun von Intel abermals bestärkt. Die Sort, EMIB, Foveros, große Packages, Co-Designs verschiedener Chipfertiger – Intel ist im Grunde für alles offen.

Dabei sieht sich Intel nicht nur technisch in einer führenden Position, sondern auch im Hinblick auf die Kosten, Kapazität und den Schutz der IP seiner Kunden.

Das, was Intel noch fehlt, sind die großen Kunden – sowohl in der Fertigung, wie auch dem Packaging. Seit Ankündigung des Foundry-Modells hat man zwar bereits verkündet, dass man Kunden für die Fertigung in Intel 18A und für das Packaging habe, offiziell vorgestellt wurden bisher allerdings nur AWS für vermutlich ein Custom-Xeon-Modell sowie Cisco. Beides dürfte in den Stückzahlen bei weitem nicht an das heranreichen, was TSMC alleine für NVIDIA Monat für Monat durch seine Fabs schiebt. Dabei war NVIDIA bereits im vergangenen Jahr als möglicher Kunde für das Packaging im Gespräch.

Zuletzt wurde NVIDIA auf der GTC auf eine mögliche Alternative zu TSMC angesprochen und bestätigte daraufhin nur, dass man regelmäßig eine alternative Fertigung evaluieren und dies auch künftig tun werde. Intel wäre mit Intel 18A und dem Advanced Packaging sicherlich eine denkbare Alternative. Auch Apple ist als Kunde immer wieder im Gespräch. Einen solchen für sich zu gewinnen, wäre sicherlich ein Prestigeprojekt für Intel Foundry.

Zuletzt machte Intel Foundry bei einem Umsatz von 4,5 Milliarden US-Dollar einen Verlust in Höhe von 2,3 Milliarden US-Dollar. Für das zweite Halbjahr 2025 soll Intel 18A in die Massenproduktion gehen. Ab dann soll Intel Foundry in Richtung positiver Quartalszahlen kommen. Eine ausgeglichene Bilanz erwartet Intel bis Ende 2027. Die enormen Kosten wieder hereinzuholen, wird sicherlich nur mit einem oder mehreren Großkunden gelingen. Mit Intel 18A will Intel die Fertigung der eigenen Produkte wieder größtenteils auf die eigenen Füße stellen. Clearwater Forest und Panther Lake sind hier die prominentesten Beispiele. Intel Foundry muss nun aber auch gegenüber Intel Products wettbewerbsfähig sein und bleiben. Ein Selbstläufer ist dies alles nicht, zumal der Heilsbringer Intel 18A noch nicht durch erhältliche Produkte glänzen konnte.