Werbung

Auf seinem Analyst Day 2024 hat Marvell eine Initiative vorgestellt, welche Custom-HBM-Chips für den Einsatz auf Beschleunigern vorsieht, sodass einige der Nachteile der Standard-Varianten beseitigt werden. Marvell hat zusammen mit Micron, Samsung und SK hynix, den drei großen HBM-Herstellern, an dieser Lösung gearbeitet.

Nahezu alle KI- und HPC-Beschleuniger nutzen aktuell High Bandwidth Memory oder kurz HBM. Der aktuell verwendete HBM3E kommt dabei über ein 1.024 Bit breites Speicherinterface auf eine Speicherbandbreite von 1.229 GB/s pro Chip. Mit HBM4 sollen ab 2025 auf den neuen Beschleunigern 1.638 GB/s erreicht werden.

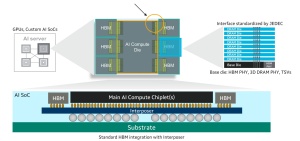

Ein JEDEC-Standard für HBM soll sicherstellen, dass der Speicher, egal von welchem Hersteller, gewisse Vorgaben einhält und damit herstellerübergreifend verwendet werden kann. Dennoch muss hier natürlich eine Verifikation stattfinden. Doch Standards sind auch immer gewissen Kompromissen unterworfen und genau diese will Marvell mit einem Custom-HBM (cHBM) angehen. So gibt es Vorgaben bzw. einen Standard für das Interface für den HBM auf dem Host-Chip. Dieses belegt relativ viel Platz im Randbereich eines Chips.

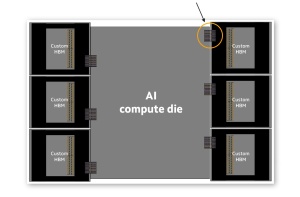

Durch eine Modifikation des Interface will Marvell die Leistungsaufnahme des Speicherinterface um 70 % reduzieren können und zugleich wird 25 % an Platz auf dem Host-Chip eingespart, was wiederum 33 % mehr HBM-Stacks möglich macht, die an den Chip angebunden werden. Mit beispielsweise 8x 1.024 Bit gegenüber 6x 1.024 Bit steigt damit auch die Speicherbandbreite des gesamten Speicherinterface.

Noch ist nicht bekannt, wie genau Marvell den cHBM umsetzen will und in welchen Bereichen es Abweichungen von der JEDEC-Norm geben wird. HBM4 wird beispielsweise die Anzahl der Pins auf der Unterseite des Chips von aktuell etwas mehr als 1.000 auf über 2.000 erhöhen. Auch diese größere Komplexität könnte cHBM angehen.

Auf den von Marvell veröffentlichen Darstellungen (via ServeTheHome) ist vor allem die Chipfläche ein Thema.

Aber neben den physischen Modifikationen könnte es auch Änderungen am Protokoll geben. Benutzerdefinierte Lösung können einen Teil des Overheads im Protokoll beseitigen, da keinerlei Kompatibilitätsprobleme zu erwarten sind. Der PHY, das physikalische Interface zwischen Host-Chip und HBM, kann ebenfalls mit anderen Tx/Rx-Spezifikationen umgesetzt werden. Diese können für eine höhere Bandbreite und/oder geringere Leistungsaufnahme sorgen. Die Effizienz in der Übertragung pro Bit (angegeben in pJ/Bit) ist eine maßgebliche Größe in diesem Bereich.

Modifikationen am HBM-Speicher sind bereits häufiger geplant gewesen. Sk hynix und Samsung arbeiten seit geraumer Zeit an HBM mit integrierten KI-Kernen, so dass bestimmte Berechnungen bereits im Speicher und direkt an den Daten durchgeführt werden können.