Werbung

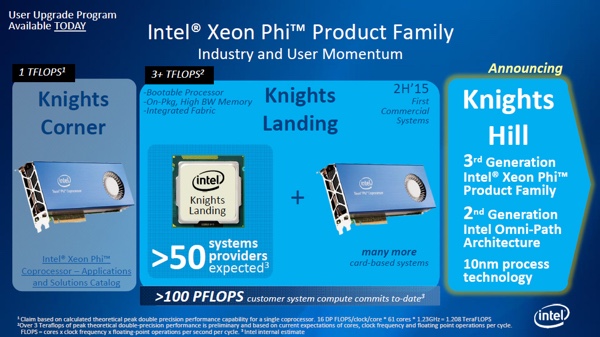

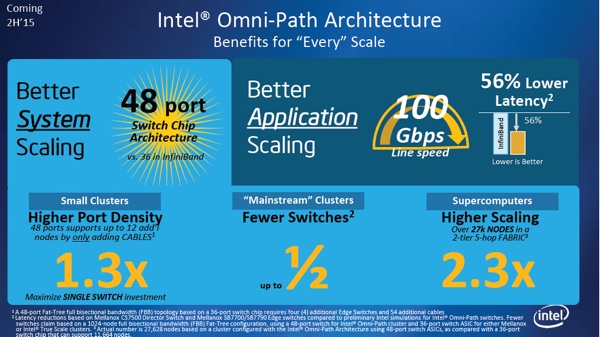

Auf der diesjährigen Supercomputing Conference (SC14) in New Orleans gab Intel Details über die kommende dritte Generation seiner Xeon-Phi-Prozessoren (Codename "Knights Hill") bekannt. Diese werden im 10-nm-Verfahren gefertigt und beinhalten Intels "Omni-Path Fabric"-Architektur. Die neue Technologie ermöglicht eine Geschwindigkeit von 100 Gigabit pro Sekunde sowie eine um bis zu 56 Prozent niedrigere Latenzzeit im Vergleich zu InfiniBand-basierten Clustern. Damit folgt Intel auch in dieser Hinsicht dem aktuellen Trend nach immer schnelleren Übertragungstechniken - ähnlich wie NVIDIAs NVLink Technologie, die in Zusammenarbeit mit IBM eingesetzt werden soll.

Zunächst einmal macht die Ankündigung von "Knights Hill" deutlich, dass Intel weiterhin an seinen Plänen festhält, in der zweiten Jahreshälfte 2015 die zweite Generation "Knights Landing" einzuführen. Dabei handelt es sich um Beschleunigerkarten mit in 14 nm gefertigten "Silvermont"-Kernen und dem neuen Stacked Memory. Während es zu "Knights Landing" also bereits viele technischen Daten gibt, hält sich Intel mit diesen in der Ankündigung zu "Knights Hill" noch zurück. Entsprechend dem 10-nm-Prozess ist mit ersten Produkten aber nicht vor 2017 zu rechnen.

Technischer Hintergrund "Knights Landing"

"Knight Landing" wird, wie angesprochen, auf bis zu 72 "Silvermont"-Kernen basieren. Diese bauen auf der klassischen x86-Architektur auf und können pro Kern vier Threads bearbeiten. Daneben besitzen sie noch AVX512-Einheiten. Insgesamt sollen die neuen Xeon-Phi-Beschleuniger auf 3 TFLOPS Double-Precision-Performance kommen. Zum Vergleich: AMDs FirePro W9100 kommt auf 2,62 TFLOPS und NVIDIAs Tesla K80 erreicht 2,91 TFLOPS. Wichtig ist aber auch der lokal verfügbare Speicher, der 16 GB groß sein soll. Intel spricht von einer fünffach höheren Bandbreite im Vergleich zu DDR4. Intel und Micron haben dafür den Einsatz von Hybrid Memory Cube (HMC) in "Knights Landing" bestätigt. Dieser sogenannte Stacked Memory soll sich wie L2- oder L3-Cache verhalten, der sich direkt auf dem Chip befindet. Dementsprechend soll auch die Speicherbandbreite dieses Speichertyps mit einem klassischem Cache vergleichbar sein.

Ein paar Besonderheiten bei den verwendeten Rechenkernen gibt es auch noch. So werden diese auf den aktuellen "Silvermont"-Kernen basieren, wie sie zum Beispiel in der "Bay Trail"-Plattform zum Einsatz kommen. In technischer Hinsicht nimmt Intel aber einige Änderungen vor, um die Kerne auf die Gegebenheiten auf Xeon-Phi-Karten anzupassen. Dazu zählt eine andere Cache-Hierarchie und die Tatsache, dass mehr als nur vier Threads pro Kern verarbeitet werden können. Eine höhere Pack-Dichte im Server will Intel durch die Sockelbarkeit der neuen "Knights Landing"-Xeon-Phi erreichen. Letztendlich sollen sich pro 1U-Einheit mehr Beschleuniger unterbringen lassen, als dies aktuell möglich ist.

Intel Omni-Path Fabric Architektur

Wichtiger Bestandteil eines jeden Xeon-Phi-Beschleunigers ist der Omni-Path. Darin will man nicht nur die Geschwindigkeit auf bis zu 100 GBit pro Sekunde hochschrauben, sondern auch die Latenzen verringern sowie die Anzahl der Switches in einem solchen Netzwerk reduzieren. Intel positioniert Omni-Path direkt gegen die etablierte InfiniBand-Technik, die aktuell in den meisten derartigen Systemen zum Einsatz kommt.