Werbung

Vor etwa zwei Jahren begannen Samsung und SK Hynix mit der Risc-Production von High Bandwidth Memory der zweiten Generation. Seit Sommer wird dieser in der Massenfertigung produziert und NVIDIA verbaut diesen auf der Tesla P100, Quadro GP100, Tesla V100 und Titan V. Im Endkunden-Bereich ist AMD mit der Radeon RX Vega 56 und 64 der bisher einzige Abnehmer.

Vor einigen Wochen kündigte Samsung die 2. Generation des HBM2 namens Aquabolt an. Dieser soll bei gleicher Leistungsaufnahme eine Bandbreite von 2,4 GBit/s pro Pin erreichen. Damit erreicht Samsung eine Speicherbandbreite von 307 GB/s für einen einzelnen 8-GB-Speicherstack und einem Speicherinterface von 1.024 Bit. Nach eigenen Angaben hat Samsung das SV-Design (Through Silicon Via’s) verbessert und setzt Thermal Bumbs ein, um die Abwärme besser abführen zu können.

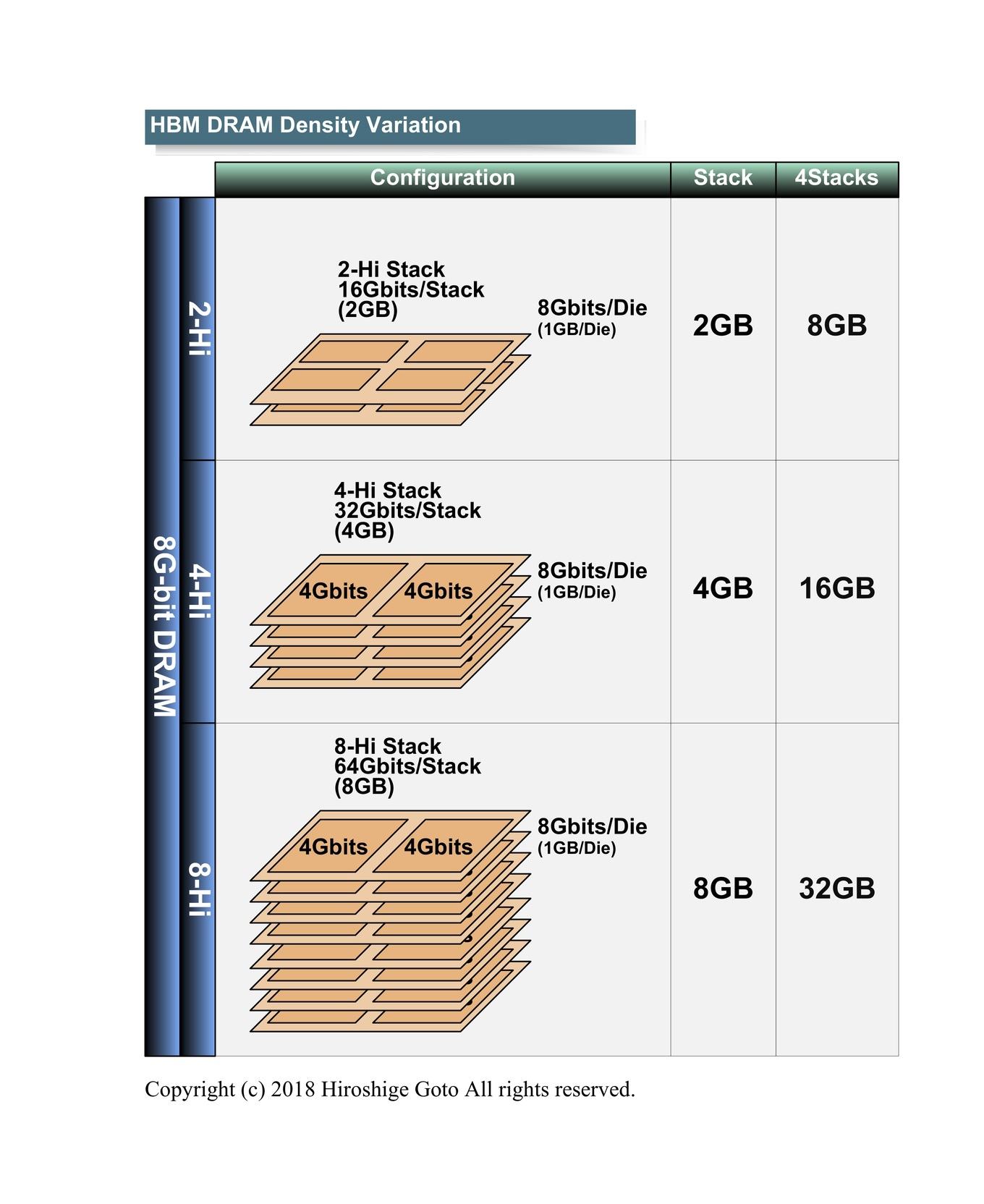

Die japanischen Kollegen von PC Watch haben sich die Änderungen in der 2. Generation des HBM2 nun etwas genauer angeschaut und führen dies am Beispiel des Speichers von SK Hynix an. HBM2 ist für eine maximale Bandbreite von 2 GBit/s pro Pin bei einer Chip-Speicherbandbreite von 256 GB/s konzipiert worden. Bei einer 4-Stack-Konfiguration (4Hi) ergibt sich daraus eine Speicherbandbreite von 1 TB/s bei einer Kapazität von 4 GB pro HBM2-Chip. Maximal geplant ist eine Ausbaustufe mit 8-Stacks (8Hi) für eine Speicherkapazität von 32 GB.

Wie sich in der Praxis aber zeigt, sind diese Ziele noch lange nicht erreicht worden. Von der geplanten Speicherbandbreite von 1 TB/s sind die aktuellen Produkte noch weit entfernt. Die NVIDIA Tesla V100 kommt auf 720 GB/s, AMDs Radeon Vega auf 484 GB/s und NVIDIAs Titan V auf 652,8 GB/s. Grund hierfür sind offenbar technische Schwierigkeiten bei der Fertigung bzw. Umsetzung von HBM2. NVIDIA wollte schon bei der Tesla P100 mit HBM2 darauf nicht genauer eingehen, zeigte sich aber recht unzufrieden aufgrund der Tatsache, dass die gewünschten Werte nicht erreicht werden konnten. Für Samsung und SK Hynix war die 1. Generation von HBM2 mehr oder weniger ein Kompromiss aus Speicherkapazität und Speicherbandbreite. Aus diesem Grund hat Samsung die Bandbreite pro Pin auf 2,4 GBit/s erhöht – geplant waren wie gesagt einmal maximal 2 GBit/s.

Mit der 2. Generation des HBM2 haben Samsung und SK Hynix offenbar grundlegende Änderungen am Design vorgenommen. Dies betrifft die Topologie der Verbindungen mittels TSVs in den DRAM-Stacks zur Logic-Die. In den Dieshots der Vega-10-GPU wurden auch der HBM2 in seine einzelnen Schichten zerlegt und darin sind die DRAM-Stacks und Logic-Die schön zu erkennen.

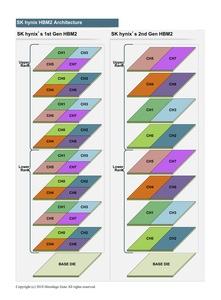

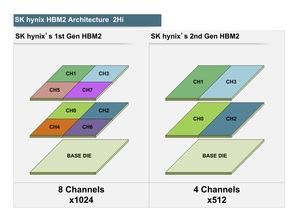

In der 1. Generation des HBM2 wurden die oberen Stacks durch die darunterliegenden Stacks durchgeschleift. Es gab keine direkten Verbindungen zwischen den oberen Stacks und dem Logic-Die. Die 2. Generation verwendet nun direkte Verbindungen. Darauf verweist auch Samsung mit dem verbesserten SV-Design des Aquabolt-HBM2. Um die Bandbreite möglichst hoch zu halten wurde jeder DRAM-Stack mit vier Kanälen angebunden – für zwei Stacks wurden jeweils acht Kanäle verwendet. Per Lower- und Upper-Rank konnte dies von vier auf acht Stacks erweitert werden.

Die 2. Generation des HBM2 von SK Hynix verwendet nun nur noch zwei Channel pro DRAM-Stack. Offenbar bot Samsung auch in der 1. Generation Varianten an, die zwischen zwei und vier Kanälen konfigurierbar waren. Durch die geringere Anzahl an Kanälen pro DRAM-Stack können jeweils direkte Verbindungen zum Logic-Die erstellt werden. Ein Durchschleifen ist nicht mehr notwendig.

Dies bedeutet aber auch, dass nur noch mit HBM2 mit mehr als vier DRAM-Stacks die maximale Bandbreite erreicht werden kann. Ein insgesamt 1.024 Bit breites Speicherinterface wird durch die Anbindung der zwei DRAM-Stacks intern zu 4x 128 Bit also nur 512 Bit. Erst ab vier Stacks können die vollen 8x 128 Bit also 1.024 Bit angebunden werden.

Die Umtellung der Kanal-Konfiguration zeigt eine Verschiebung hinsichtlich der Ansprüche des Marktes. Für die 1. Generation des HBM2 ging es darum eine möglichst hohe Bandbreite zu liefern – wenngleich auch dies nicht immer erreicht wurde. Dazu mussten die GPU-Hersteller gewisse Einschränkungen bei der Gesamtkapazität hinnehmen. Für die 2. Generation des HBM2 gilt dieser Kompromiss nur noch für eine 2-Stack-Konfiguration, ab 4Hi und bis 8Hi sind Kapazität und Speicherbandbreite nicht mehr kompromissbehaftet.

Samsung und SK Hynix wollen in Kürze mit der Massenproduktion der 2. Generation des HBM2 beginnen bzw. haben dies schon getan. Wann die ersten Partner mit dem neuen Speicher beliefert werden, ist derzeit nicht bekannt. In Frage kommen hier natürlich neben AMD und NVIDIA auch noch weitere Hardware-Hersteller, die spezielle Beschleunigerkarten mit HBM2 auf dem Markt haben. Als Beispiel zu nennen wären hier Intel mit dem Stratix 10 MX, Google mit der Tensor Processing Unit, NEC mit den SX Aurora TSUBASA und viele mehr.