Werbung

Derzeit deutet alles daraufhin, dass die Zukunft der Prozessoren und GPUs in einem modularen Chiplet-Design zu suchen ist. Intel hatte in der Vergangenheit bereits einige Ansätze in dieser Richtung aufgezeigt, AMD hat sie mit den Ryzen-, Ryzen-Threadripper- und EPYC-Prozessoren in vollem Umfang umgesetzt. Die Erfahrungen, die AMD bei den Zen-Prozessoren gemacht hat, will man in zukünftigen RDNA-Architekturen für die Grafikkarten offenbar ebenfalls umsetzen.

Bereits 2017 veröffentlichte NVIDIA ein Forschungspapier zu einer möglichen Umsetzung von Multi-Chip-Modulen für GPU. Anstatt eines monolithischen Chips sollten hier mehrere Module verwendet werden. Das was Intel bisher zur Xe-Architektur gezeigt hat, spricht ebenfalls für einen modularen Aufbau des Chips.

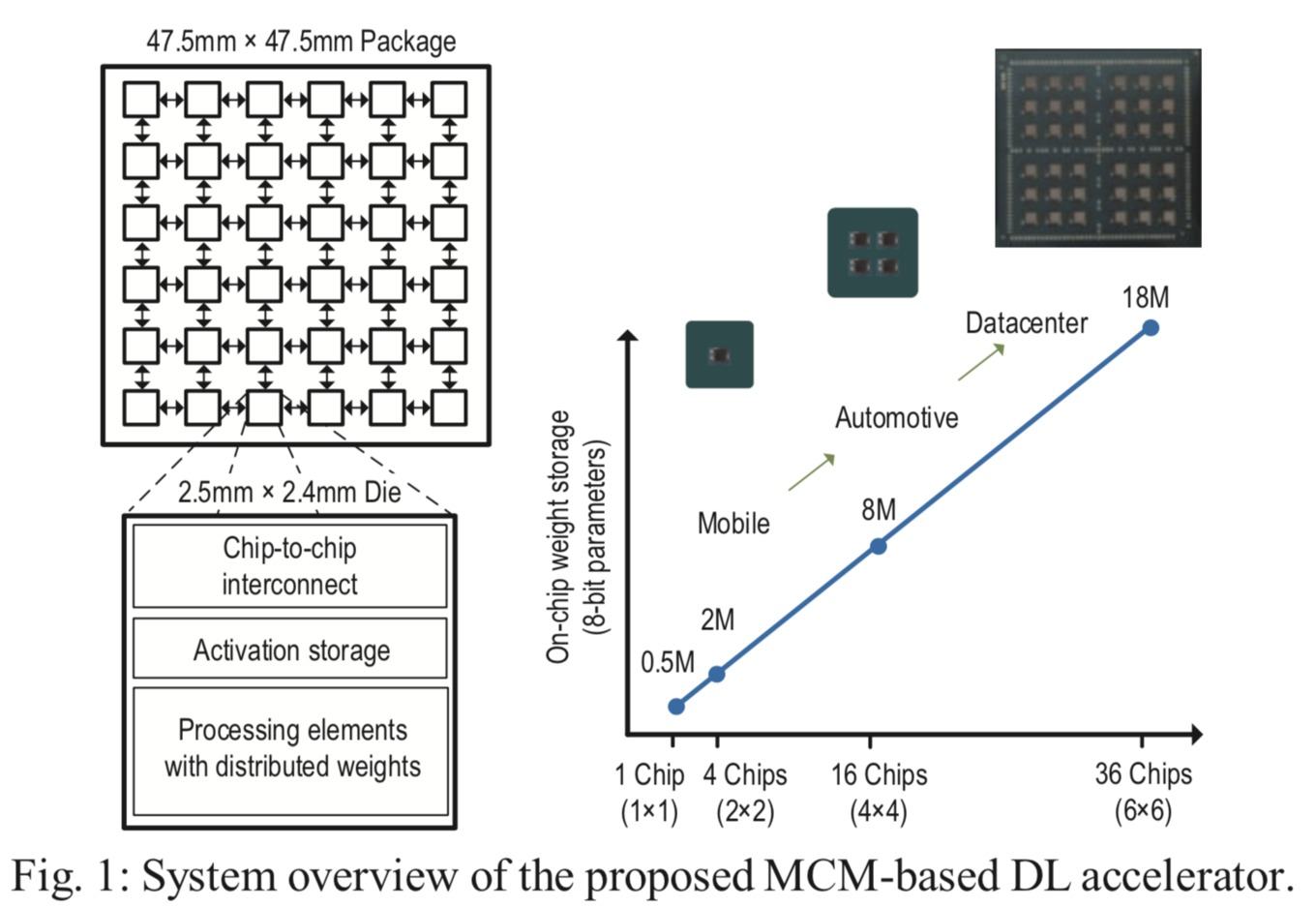

Das nun von NVIDIA veröffentlichte Forschungspapier (PDF) spricht von einem Scalable Multi-Chip-Module-based Deep Neural Network Accelerator mit Ground-Reference Signaling, der in 16 nm gefertigt werden soll. Skalieren soll das Design über eine Rechenleistung von 0,32 bis 128 TOPS, also 0,32 bis 128 Billionen Rechenoperationen pro Sekunde für Berechnungen mit niedriger Genauigkeit. Zum Vergleich: NVIDIAs Tesla V100 kommt in der Datacenter-Variante ebenfalls auf etwa 125 TOPS, benötigt dazu aber ein Vielfaches der elektrischen Leistung im Vergleich zum von NVIDIA erforschten Chip.

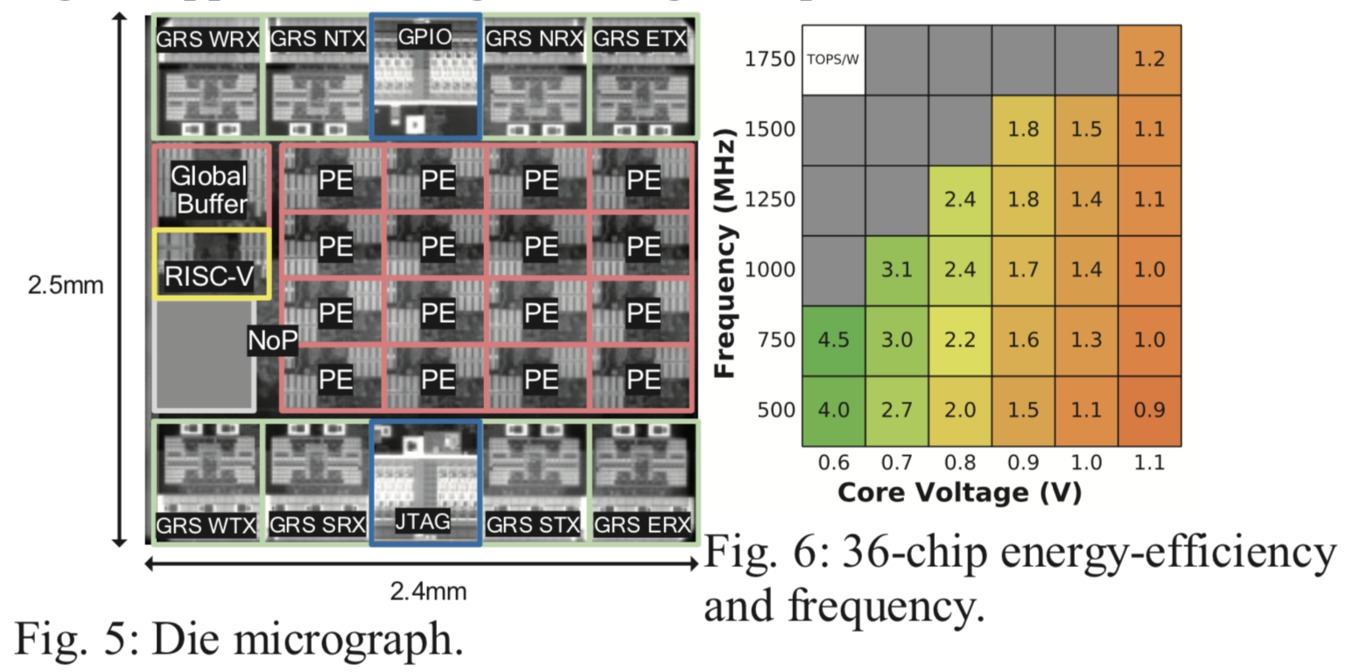

Dieser ist aber nicht mehr nur reine Theorie, sondern wurde in 16 nm auch schon gefertigt. Erreicht wurden mit diesem Chip 1,29 TOPS/mm² oder eine Effizienz von 0,11 pJ/OP. Der Chip kann in verschiedenen Ausbaustufen des MCM-Designs gebaut werden. Die Variante mit einem Processing Elements (PE) erreicht dabei 4,01 TOPS Peak-Rechenleistung. Die Variante mit 36 PEs 127,8 TOPS. NVIDIA sieht die Variante mit 1x1- bzw. 2x2-PEs für den mobilen Einsatz vor. Im Automotive-Segment sind 4x4-PEs vorgesehen. Im Datacenter wäre die Einsatz von 6x6-PEs denkbar.

Ein solcher AI-Chip lässt sich natürlich nicht mehr mit einer klassischen GPU vergleichen. Die PEs arbeiten nicht wie klassische Shader, sondern sind auf andere Rechenoperationen ausgelegt. Maßgeblich für die Rechenleistung verantwortlich sind jeweils acht Vektoreinheiten für Multiply-Accumulate-Einheiten (MAC).

Eine große Bedeutung kommt dem Interconnect zu. Neben den bis zu 36 PEs ist auch noch ein RISC-V-Prozessor vorhanden. Um den Interconnect zu verwalten, gibt es einen Packet-Switched Network-on-Chip (NoC) und einen Network-on-Package-(NoP)-Router. Hinzu kommt ein globaler Puffer (Global Buffer, GB). Der Interconnect ist in einer Mesh-Topologie aufgebaut. Eine Besonderheit ist das Ground-Referenced-Signaling (GRS), welches nicht nur als physikalische Übertragungsebene für den Interconnect eingesetzt wird, sondern das auch zwischen mehreren Packages verwendet werden kann.

Auf einer Besonderheit eines MCM-Designs geht NVIDIA ebenfalls noch ein. So wird die Effizienz auch dadurch erreicht, dass die einzelnen Module mit unterschiedlichen Taktraten und Spannungen betrieben werden können. Wird der AI-Chip mit 36 PEs also nicht vollständig ausgelastet, werden nur die auch wirklich verwendeten PEs mit dem vollen Takt und der entsprechenden Spannung betrieben.

Bei großen monolithischen Chips wird dies über ein sogenanntes Power Gating realisiert. Nicht verwendete Bereiche des Chips werden dabei weitestgehend abgeschaltet und sparen damit Strom.

Chiplets sind wohl der Weg in die Zukunft

Es wird mehr und mehr deutlich, dass kaum ein Hersteller ohne Chiplet-Design auskommen wird. AMD, Intel und NVIDIA arbeiten in verschiedenen Entwicklungsstufen daran. Während AMD diesen Ansatz bei den Ryzen-Prozessoren der dritten Generation und bei den EPYC-Prozessoren der zweiten Generation in diesem Jahr konkret umsetzen wird, ist Intel wohl inzwischen auch zur Erkenntnis gelangt, dass man ohne nicht mehr weit kommen wird.

Dabei kann man sich natürlich darüber unterhalten, was genau nun ein MCM- oder Chiplet-Design ist und ob wir dies nicht schon mehrfach gesehen haben. Die von AMD gewählte Form mit CPU-Dies aus der 7-nm-Fertigung und dem I/O-Die aus der 12-nm-Fertigung ist wohl die erste konkrete Umsetzung, die als Chiplet-Design bezeichnet werden kann. Funktion und Fertigung können voneinander getrennt entwickelt und gefertigt werden – am Ende werden sie in einem Package untergebracht.

Wenn auch noch nicht in der nächsten Generation der GeForce-Grafikkarten, früher oder später wird NVIDIA hier wohl auf ein Chiplet- oder MCM-Design wechseln. Wohl als erstes wird man diesen Schritt für bestimmte Datacenter-Produkte gehen. Das Forschungspapier für einen AI-Beschleuniger zeigt dies recht deutlich.