Werbung

Neben immer schnelleren Interconnects spielt möglichst schnell angebundener Speicher für GPGPUs, ASICs und FPAGs eine immer wichtigeren Rolle. Für Unternehmen, die keine eigene Intellectual Property (IP) für einen HBM2E-Speichercontroller und den dazugehörigen PHY (die physikalische Anbindung) entwickeln wollen oder können, stellt Rambus diesen bereit.

Die Standardisierungsbehörde JEDEC spezifizierte HBM2E bereits auf bis zu 3,2 GBit/s, SK Hynix und Samsung haben bereits angekündigt, bald entsprechende Speicherchips liefern zu können. TSMC hat gemeinsam mit Broadcom bereits einen konkreten Einsatz von HBM2E angekündigt. NVIDIA und AMD gelten ebenfalls als heiße Kandidaten für den baldigen Einsatz von HBM2E.

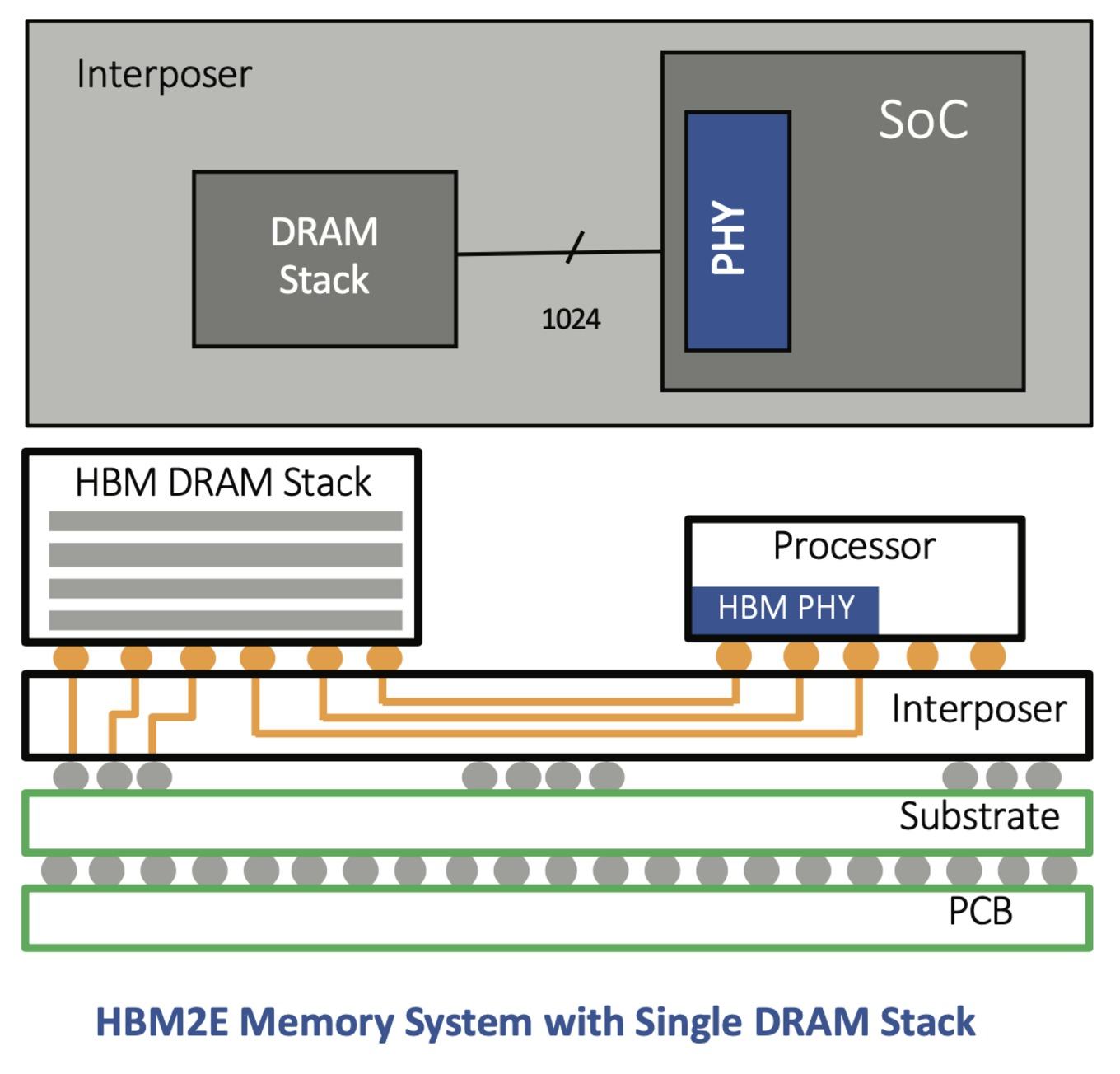

Die von Rambus vorgestellte Lösung bindet HBM2E-Speicher mit 1.024 Bit und 3,2 GBit/s pro Chip (bzw. pro Pin) an. Unterstützt werden Speicherstaks mit bis zu zwölf Layern.

Daneben unterstützt der Speichercontroller acht Kanäle und 16 Pseudo-Kanäle. Zwar bietet Rambus einen Controller und PHY an, es ist aber auch möglich, nur den Controller von Rambus und eine eigene PHY-Lösung zu verwenden (PHY Independent Mode). In der sogenannten East-West Orientation kann der PHY in den Ecken des Chips platziert werden.

Rambus bietet interessierten Unternehmen für den Einsatz des HBM2E alle erdenkliche Unterstützung für die Integration der Technologie. Dies schließt die Software für den Speichercontroller mit ein.