Werbung

Im Rahmen der gestrigen Präsentation der Neuausrichtung in der Fertigung hat Intel auch weitere Details zum Xe-HPC-Chip Ponte Vecchio verkündet. Anfang Januar vermeldete Intel, dass die ersten Chips aus der Fertigung zurückgekehrt sind und in den Laboren getestet werden. Das Packaging von Ponte Vecchio (Foveros und EMIB) spielt eine zentrale Rolle für Intels zukünftigen GPUs und Prozessoren – nicht nur für Ponte Vecchio.

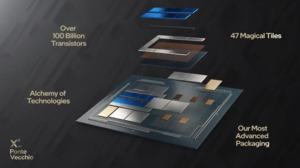

Intel bestätigte gestern, dass ein Xe-HPC-Chip aus 47 Tiles (so nennt Intel seine Chiplets) besteht. Vor einigen Wochen nannte Raja Koduri 41 Chiplets/Tiles. Wie diese Diskrepanz zu verstehen ist und ob Koduri nur die aktiven Komponenten meinte, während Intel gestern alle Chiplets (auch die passiven) aufführte, ist nicht bekannt. Zudem bestätigte Intel, dass alle Tiles zusammengenommen auf über 100 Milliarden Transistoren kommen. Zum Vergleich: NVIDIAs GA100-GPU, die in 7 nm gefertigt wird, kommt auf 54 Milliarden Transistoren bei einer Fläche von 826 mm² – besteht allerdings auch aus einem monolithischen Design.

In einem Video (siehe eingebetteten Tweet am Ende dieser Meldung) ist zudem zu erkennen, wie gleich mehrere Xe-HPC-Chips in einer Fertigungsstraße "vom Band laufen". Außerdem gibt es das riesige Package noch mehrfach zu sehen.

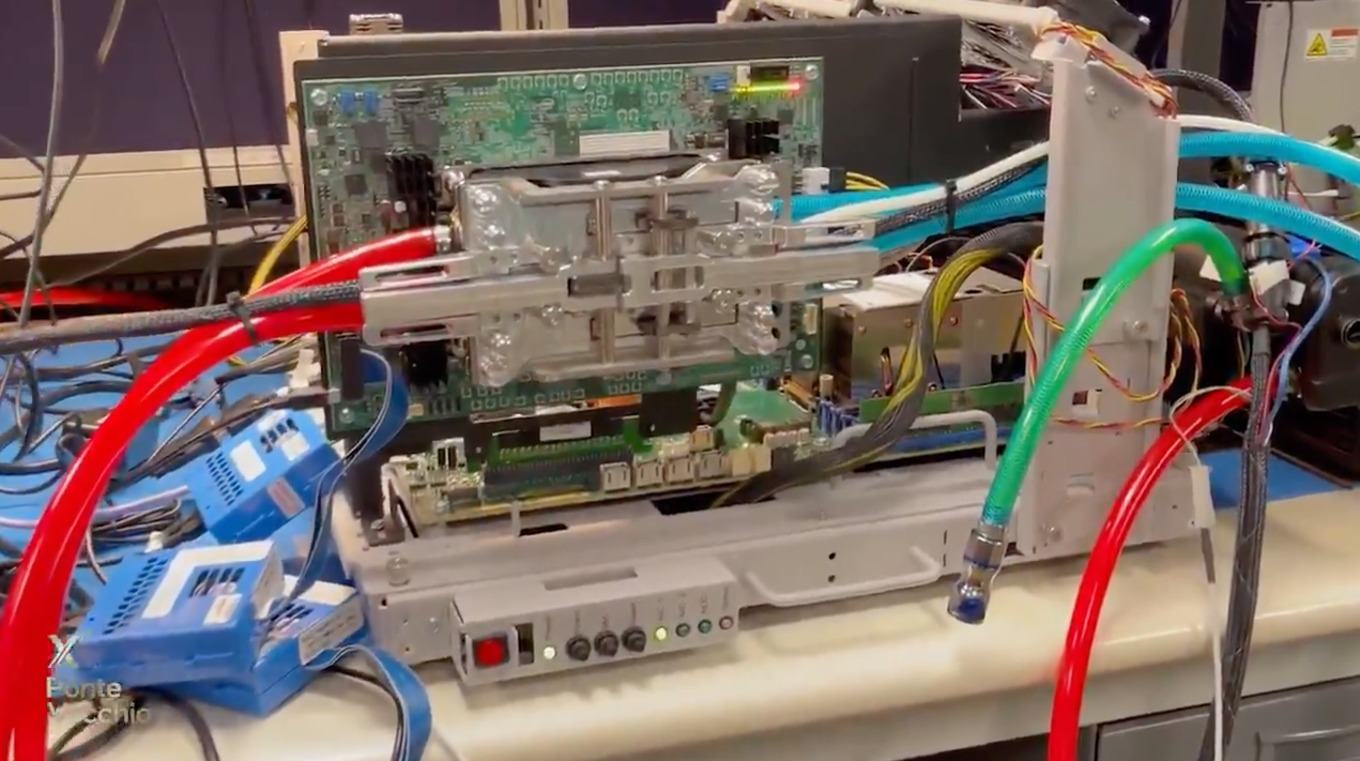

Schlussendlich gewährt Intel noch einen interessanten Blick in das Labor in Folsom. Hier gibt es Xe-HPC Ponte Vecchio im Einsatz zu sehen. Die Entwicklungs-Hardware wird wassergekühlt. Das Entwicklunsboard, auf dem der Chip sitzt, besitzt zudem zwei EPS-Anschlüsse. Laut Kommandozeile wurde die Xe-HPC-Karten auf Systemen mit Sapphire Rapids (SPR), also der übernächsten Xeon-Generation, betrieben. Sapphire Rapids wird aus bis zu vier Chiplets bestehen, PCI-Express 5.0 (auf Basis dessen Compute Express Link) und DDR5 unterstützen.

Intel will zusammen mit dem U.S. Department of Energy (DOE) in der Nähe von Chicago das erste ExaFLOPS-System in den USA aufbauen. Betrieben werden soll das System vom Argonne National Laboratory. Das Besondere am Aurora-Supercomputer: Alle wichtigen Komponenten sollten von Intel stammen. Dies betrifft besonders die Prozessoren (Xeon Scalable der 4. Generation, Sapphire Rapids) und die GPU-Beschleuniger (Ponte Vecchio, Xe-HPC). Auch Intels Optane DC Persistent Memory soll zum Einsatz kommen.

Ursprünglich sollte der Supercomputer 2021 aufgebaut werden. Doch aufgrund der Probleme in der Fertigung und der allgemeinen Lage dürfte dieser Termin nicht zu halten sein.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Update: Intel klärt auf

Auf Nachfrage hat uns Raja Koduri, seines Zeichens Senior Vice President der neuen Grafiksparte "Core and Visual Computing" bei Intel, die Frage nach der Anzahl der Tiles beantwortet. Demnach sind bei der Angabe der 41 Tiles aus dem Januar die HBM-Chips nicht mitgezählt worden.

Zudem schlüsselt Koduri die einzelnen Tiles mit der Fertigung noch einmal auf:

- 16x Xe HPC (interne und externe Fertigung)

- 8x Rambo (interne Fertigung)

- 2x Xe Base (interne Fertigung)

- 11x EMIB (interne Fertigung)

- 2x Xe Link (externe Fertigung)

- 8x HBM (externe Fertigung)

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen