Werbung

Im November des vergangenen Jahres stellte AMD die erste GPU auf Basis einer CDNA-Architektur vor. Die Radeon Instinct MI100 kann in Teilen mit NVIDIAs A100 mithalten, fällt inzwischen aber vor allem durch den nur 32 GB großen HBM etwas hinter dem 80-GB-Modell von NVIDIA zurück. Aber diese erste Generation der CDNA-Architektur ist noch ein Derivat der GCN-Architektur, mit CDNA 2 will AMD die Mikroarchitektur dann komplett auf das Computing ausgelegt haben. Eine Vorstellung wird noch in diesem Jahr erwartet.

Im Rahmen der ISC-HPC hielt Ugo Varetto, CTO des Pawsey Supercomputing Centre in Perth, Australien, einen Vortrag zum System, welches aufgebaut werden soll, um die Daten des Square Kilometre Array (SKA) zu verarbeiten. Mehrere hundert Einzelspiegel in Australien und Südafrika und mehrere tausend Breitbandantennen bilden an zwei Standorten eine Sammelfläche für das Radioteleskop.

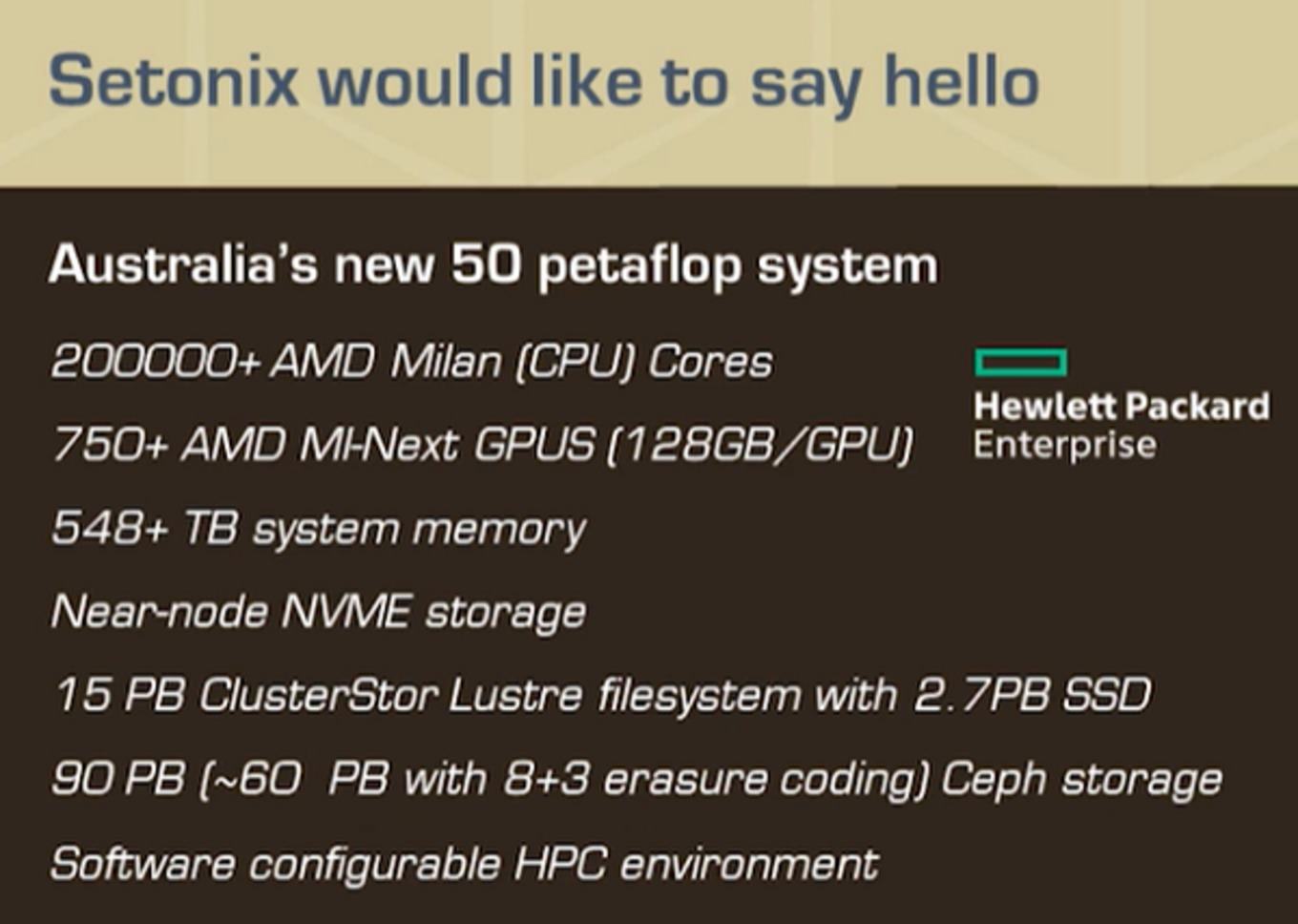

Der Setonix getaufte Supercomputer soll eine Rechenleistung von 50 PFLOPS erreichen. Bereits bekannt war, dass EPYC-Prozessoren eingesetzt werden sollen, wenngleich bisher nicht bekannt war, um welche es sich hier handelt. Hinzu kommen 750+ GPUs, die ebenfalls noch nicht genauer spezifiziert waren. Den Prozessoren und GPUs zur Seite steht ein aufwendiges Speichersystem. Ein HPE Lustre-Cluster umfasst 15 PB. Dieser Speicher besteht aus NVMe-SSDs, die als Near-Node-Speicher besonders schnell angebunden sind. Hinzu kommen noch 90 PB an weiterem Speicher, der die Daten vorhalten soll. Das sogenannte Erasure Coding beschreibt ein Verhältnis von Originaldaten und Codierdaten. Im Falle eines 8+3 Codings werden acht Teile der Daten mit drei Teilen der Codierungsdaten angelegt und diese dann auf 11 (8 + 3) Platten verteilt.

Im Vortrag sprach Varetto nun von 200.000 Milan-CPU-Kernen, was bei den EPYC-Modellen mit 64 Kernen genau 3.125 Prozessoren entsprechen würde. Hinzu kommen besagte 750+ GPUs, die nur als MI-Next benannt wurden. Dabei wird es sich um die Radeon Instinct MI200 handeln. Pro GPU sollen 128 GB an Speicher zur Verfügung stehen. Da HBM2E zum Einsatz kommen sollte und dieser pro Chip ein Speicherinterface von 1.024 Bit benötigt, kommen für 128 GB also acht HBM2E-Chips zum Einsatz – insgesamt also 8.192 Bit. Für den Einsatz von acht HBM2E-Chips ergibt sich eine Gesamtspeicherbandbreite von 3,28 TB/s. Zum Vergleich: Die Radeon Instinct MI100 kommt auf 1,23 TB/s und NVIDIAs schnellste A100-Variante auf 2 TB/s.

Die Aldebaran getaufte GPU auf Basis der CDNA-2-Architektur soll ein MCM-Design sein, welches aus zwei Chiplets besteht. Die beiden identisch aufgebauten Chiplets sind über einen Interconnect miteinander verbunden und bieten jeweils 4x 1.024 Bit Speicheranbindung für den HBM2E sowie die eigentlichen Recheneinheiten, zu denen aber noch nur sehr wenig bekannt ist. 2x 128 Compute Units und damit 16.384 Shadereinheiten sollen es sein, wenngleich diese auf FP64-Berechnungen ausgelegt sein sollen und natürlich auch die geringeren Genauigkeiten beherrschen. Für die GeForce- und Radeon-GPUs sind FP32, INT32 und FP16 wichtig.

Noch in diesem Jahr sollte AMD die Radeon Instinct MI200 und damit verbunden auch die CDNA-2-Architektur vorstellen. Spannend wird zu beobachten sein, ob AMD mit seinen GPU-Beschleunigern die notwendige Durchschlagkraft erreicht. Während die Top500 der Supercomputer mehr neue Systeme mit EPYC- anstatt der Xeon-Prozessoren aufzuweisen hat, wird der Markt bei den GPU-Beschleunigern ganz klar von NVIDIA dominiert. Genauer gesagt gab es ausschließlich neue Systeme mit A100-Beschleunigern. Andere Hersteller spielten keine Rolle. Ein System mit Radeon-Instinct-MI100-Karten sucht man daher vergebens und auch am Markt sind diese Karten nicht zu finden. Große Stückzahlen der ersten CDNA-Generation dürfte AMD also nicht abgesetzt haben.

Mit dem Frontier-Supercomputer ist allerdings ein System angekündigt worden, welches sowohl EPYC-Prozessoren (Custom Milan) als auch Radeon-Instinct-Beschleuniger einsetzen soll. 1,5 EFLOPS soll das System erreichen und setzt pro Node auf einen EPYC-Prozessor und vier Radeon-Instinct-Beschleuniger. Dies dürfte der erste Supercomputer sein, der mit dieser Hardware in der obersten Liga mitspielt. Der Start des Aufbaus war ursprünglich für 2021 geplant.