Werbung

Bisher wird der Markt für KI-Beschleuniger fast ausschließlich von NVIDIA besetzt und hier verdient man auch sehr gut daran. Aber natürlich wollen Hersteller wie Intel und AMD diesen Markt nicht komplett dem aktuellen Branchenprimus überlassen und so präsentierte man im Falle von AMD bereits im Januar des vergangenen Jahres die ersten Details zur Instinct-MI300-Familie. Zusammen mit den weiteren Varianten der EPYC-Familie gab es zur Mitte des Jahres weitere Details. Doch auch wenn die ersten Partner die Chips bereits in ihren Laboren betreiben, der offizielle Startschuss ist noch nicht gefallen.

Am heutigen Tage ist es nun endlich soweit und die Instinct-MI300-Familie wird in allen Details vorgestellt und soll endlich für Konkurrenz in diesem Marktsegment sorgen.

Bereits bekannt war, dass die Instinct-MI300-Familie aus zwei Beschleuniger-Varianten bestehen wird: Einem Instinct MI300X mit ausschließlich Beschleuniger-Chips auf Basis der CDNA-3-Architektur und einem Instinct MI300A, bei dem einige Chiplets aus den CCDs mit Zen-4-Kernen bestehen. Der Instinct MI300A adressiert den HPC-Markt, der Instinct MI300X ist dediziert als KI-Beschleuniger gedacht.

Die einzelnen Bausteine in Form des CCDs (CPU Complex Die) mit den Zen-4-Kernen, des XCDs (Accelerator Complex Die) mit CDNA-3-Architektur und dem IOD (I/O Die) mit den notwendigen Interfaces werden wir uns nun genauer anschauen. Das Package ist extrem aufwendig und bekommt daher auch seinen eigenen Fokus in diesem Bericht, denn AMD verwendet hier mehrere unterschiedliche Packaging-Technologien.

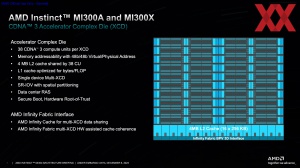

XCD: Accelerator Complex Die

Bereits für die Instinct-MI200-Beschleuniger verwendete AMD ein MCM-Design (Multi Chip Module) mit zwei GPUs, die zusammenarbeiten konnten. Es handelte sich aber um zwei Chips, die auch eigenständig ihre Funktion erfüllen. Für die XCDs wählt AMD nun einen neuen Ansatz und lässt mehrere XCDs so aussehen, als wären sie eine große GPU.

Dies hat Vorteile, denn AMD kann für die XCDs vieles auf das eigentliche Computing hin auslegen, während andere Funktionen in den IOD übertragen werden können. Damit kann AMD die Fertigung auch dahingehend spezialisieren und die XCDs entsprechend fertigen lassen. Jeder XCD besteht aus 38 Compute Units (CUs) auf Basis der CDNA-3-Architektur. Physikalisch vorhanden sind 40 CUs, aber um die Ausbeute besser steuern zu können, sind jeweils 38 CUs aktiv. Den 38 CUs stehen 4 MB an L2-Cache zur Verfügung.

Den XCDs steht der insgesamt 256 MB große Infinity Cache der IODs zur Verfügung. Zum IOD kommen wir im nächsten Abschnitt des Artikels noch genauer. Die Kommunikation zwischen den XCDs erfolgt per Infinity Fabric. Die physikalischen Verbindungen zwischen den XCDs und den IODs erfolgt über ein 3D Bond Pad (BPV). Da die XCDs über den IODs gestapelt werden, bietet es sich auch diese Verbindungen vertikal auszuführen.

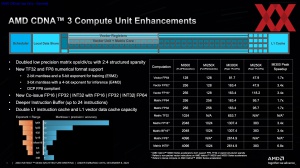

Die Unterschiede zwischen der CDNA-2- und CDNA-3-Architektur stellen sich im Wesentlichen wie folgt dar: Um die Rechenleistung bei niedriger Genauigkeit zu erhöhen, unterstützen die Vektor- und Matrix-Einheiten neue Datenformate wie TF32 und FP8 (E5M2 und E4M3, also 2 Bit Matisse mit 5 Bit Exponent und 3 Bit Matisse mit 4 Bit Exponent) und per Sparsity (dem Ausblenden von Daten in einer dünn- oder schwachbesetzte Matrix) wird ein Ops/Takt/CU-Verhältnis von 2:4 erreicht, was die Rechenleitung in gewissen Datenformaten im Vergleich zur CDNA-2-Architektur um den Faktor 3,4 anhebt.

FP32- oder INT32-Operationen können parallel zu FP32- oder FP64-Operationen ausgeführt werden. Der Instruction Buffer wird vergrößert und kann nun bis zu 24 Instruktionen fassen. Der L1-Instruction-Cache wird verdoppelt und Vector-Data-Cache größer ausgelegt.

Je nach Datenformat steigt die Rechenleistung für Vektor- und Matrix-Datensätze von halber Genauigkeit (FP8) bis doppelter Genauigkeit (FP64) um den Faktor 1,7 bis 6,8.

IOD: I/O Die

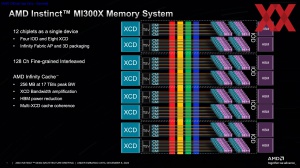

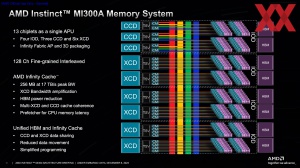

Die beiden Varianten der Beschleuniger der Instinct-MI300-Familie verwenden beide gleich vier IODs. Diese sitzen direkt nebeneinander und stellen die Basis dar, auf der sich dann die XCDs und CCDs befinden. Die vier IODs bieten unter anderem 256 MB an Infinity Cache und binden den HBM3 über insgesamt 128 Speicherkanäle mit einer aggregierte Speicherbandbreite von 17 TB/s an.

Zudem bieten die IODs 4x 16 PCI-Express-5.0 oder 4x 16 Links für den Infinity Fabric an, mit dem die IODs untereinander, aber auch die einzelnen CCDs und XCDs verbunden sind. Hinzu kommen 4x 16 dedizierte Infinity-Fabric-Links. Insgesamt bieten die vier also IODs 128 SerDes-Endpunkte (Serialisierer/Deserialisierer), um darüber dann PCI-Express oder Infinity Fabric auf Protokollebene anzubieten. Neu ist, dass die IODs der Instinct-MI300-Familie die Möglichkeit haben hier einige Links entweder als PCI-Express oder Infinity Fabric anzubieten.

Neu ist für die IODs auch die Möglichkeit diese miteinander zu verbinden. Bei den EPYC- und Ryzen-Prozessoren war bisher immer nur ein IOD vorhanden. Um die IODs miteinander zu verbinden, hat AMD einen neuen Interconnect entworfen, der als Infinity Fabric AP (Advanced Package) Interconnect bezeichnet wird.

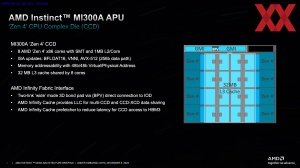

CCD: CPU Complex Die

Die in der Instinct-MI300-Serie verwendeten CCDs mit den Zen-4-Kernen sind identisch zu denen, wie sie auch für den EPYC- und Ryzen-Prozessoren zum Einsatz kommen. Die ISA ist identisch, ein SMT unterstützen diese Kerne natürlich auch. Einen Unterschied aber gibt es in der Umsetzung dessen, wie diese CCDs per Interconnect mit dem IOD verbunden werden.

Bei den EPYC- und Ryzen-Prozessoren befinden sich die CCDs neben dem IOD und werden daher auf planarer Ebene mit diesem verbunden. Für die Instinct-MI300-Serie sitzen die CCDs auf den IODs und daher kommt hier ein 3D Bond Pad (BPV) zum Einsatz, welches in abgewandelter Form auch für den 3D V-Cache auf den CCDs verwendet wird. Die zwei GMI-PHYs (Global Memory Interface) werden hier also nicht verwendet.

Ein weiterer Unterschied besteht darin, in welchem Adressraum die CCDs mit dem Speicher kommunizieren. Damit dies zwischen den CCDs und XCDs identisch ist, können die CCDs für den Instinct-MI300A-Beschleuniger einen virtuellen und physikalischen Adressraum mit 48 Bit ansprechen, während es bei den EPYC- und Ryzen-Prozessoren ein 32 Bit breiter Adressraum ist. Dies hat Auswirkungen auf Funktionen wie die Secure Memory Encryption (SME) und auch einige Virtualisierungsfunktionen, die hier dann nicht verfügbar sind.

Für die CCDs ebenfalls neu ist das Vorhandensein eines Infinity Cache, der als Last Level Cache umgesetzt wird und den CCDs sowie den XCDs und CCDs in der Kommunikation untereinander zur Verfügung steht. Genau wie bei den GPUs mit Infinity Cache dient dieser auch als Prefetcher und reduziert die Zugriffe auf den HBM3, da wichtige und häufig verwendete Daten hier abgelegt werden können.

Layout und das Speicher-Subsystem

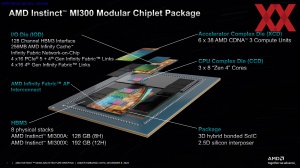

Mit dem Instinct MI300X und Instinct MI300A gibt es zwei Varianten des KI-Beschleunigers:

| Instinct MI300X | Instinct MI300A | |

| IODs | 4 | 4 |

| XCDs | 8 | 6 |

| CCDs | - | 3 |

| Anzahl der Transistoren | 153 Milliarden | 146 Milliarden |

| Stream-Prozessoren | 19.456 | 14.592 |

| Matrix-Kerne | 1.216 | 912 |

| Zen-4-Kerne | - | 24 |

| Infinity Cache | 256 MB | 256 MB |

| HBM3 | 192 GB | 128 GB |

| Speicherbandbreite | 5,3 TB/s | 5,3 TB/s |

| TDP | bis zu 750 W | bis zu 760 W |

Immer vorhanden sind vier IODs. Für den Instinct MI300X zum Einsatz kommen acht XCDs. Zwei XCDs können aber auch durch drei CCDs ersetzt werden und so kommen wir für den Instinct MI300A auf sechs XCDs und drei CCDs. Der Speicher des Instinct MI300X ist 192 GB groß und wird mittels 12-Hi HBM3 umgesetzt, beim Instinct MI300A sind es 8-Hi Stacks HBM3 und somit 128 GB an Gesamtkapazität.

DDR-Speicher verwenden weder der Instinct MI300X noch der Instinct MI300A. Entsprechend leer ist der Bereich rings um den Sockel, der nur noch die Spannungsversorgung vorsieht. Darüber hinaus führt AMD einige PCI-Express- und Ethernet-Verbindungen nach Außen.

Das zwei XCDs durch drei CCDs ersetzt werden können, hat aber nicht nur Platzgründe, sondern ist auch mit der möglichen Interconnect-Bandbreite begründet.

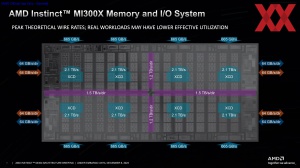

Bereits erwähnt haben wir, dass die vier IODs die CCDs und XCDs anbinden, aber auch untereinander verbunden sind. Jeder IOD bindet zwei HBM3-Chips mit jeweils 665 GB/s an. Die angesprochenen 17 TB/s an maximaler Bandbreite des Infinity Fabric ergeben sich aus 8x 2,1 TB/s die jeder XCD zum IOD erreichen kann. Nach Außen hin bieten die IODs die ebenfalls bereits erwähnten 4x 16 Links für PCI-Express 5.0 oder Infinity Fabric sowie dediziert 4x 16 Links ausschließlich für den Infinity Fabric mit jeweils 64 GB/s bidirektional.

Die IODs untereinander sind je nach physikalischer Länge der Kontaktfläche (horizontaler oder vertikaler Cut) mit 3 TB/s und 2,4 TB/s angebunden. Die 2,4 TB/s sind ausschließlich für den Datentransfer zu den Speichercontrollern ausgelegt, während die 3 TB/s noch Kapazität enthalten, die zur I/O-Kommunikation innerhalb der IODs vorgesehen sind.

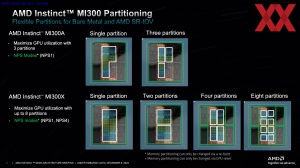

Der Instinct MI300X und Instinct MI300A können in verschiedene Compute-Partitionen unterteilt werden, was im Hinblick auf eine Single Root Input/Output Virtualisierung (SR-IOV) auch notwendig ist. Hinsichtlich der NUMA Nodes pro Sockel kann der Instinct MI300A nur im NPS1-Modus betrieben werden. Der Instinct MI300X hingegen kann neben NPS1- auch im NPS4-Modus arbeiten und teilt den Speicher dann in vier NUMA-Domänen auf. Es kann aber nur ebensoviele NUMA-Nodes wie Compute-Partitionen geben.

Der Instinct MI300A kann dabei als singuläre Entität oder unterteilt in drei Partitionen betrieben werden. Grundsätzlich stellen die 3x zwei XCDs hier auch die drei Partitionen dar und mittels dieser Unterteilung ist ist auch die maximale GPU-Leistung zu erreichen.

Der Instinct MI300X hingegen kann in eine, zwei, vier und acht Partitionen unterteilt werden, wobei die Blöcke aus jeweils zwei XCDs jeweils den kleinsten Baustein dieser Aufteilung darstellen. Auch hier wird die maximale GPU-Auslastung bei acht Partitionen erreicht.

"3.5D" Advanced Packaging

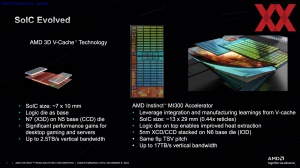

Das Stapeln der XCDs und CCDs auf den IODs sind dem Stapeln des SRAM-Chips als 3D V-Cache recht ähnlich und bedeuten gleichzeitig, dass dem Packaging in der Instinct-MI300-Serie eine wesentliche Bedeutung zukommt. Es gibt aber auch eine Weiterentwicklung in der SoIC-Technologie (Silicon over Integrated Circuit):

| AMD 3D V-Cache | Instinct MI300 | |

| SoIC-Größe | 7 x 10 mm / 70 mm² | 13 x 29 mm / 377 mm² |

| kombinierte Fertigungstechnologien | N7 auf N5 | N5 auf N6 |

| TSV-Abstände | 9 µm | 9 µm |

| maximale Bandbreite | 2,5 TB/s | 17 TB/s |

Bei der 3D-V-Cache-Technik setzt AMD einen kleinen SRAM-Chip auf den 7 x 10 mm messenden CCD. Der SRAM-Chip wird in 7 nm bei TSMC gefertigt, der CCD stammt aus der 5-nm-Fertigung. Die Abstände der TSVs liegen bei 9 µm und der 3D V-Cache erreicht eine Bandbreite von 2,5 TB/s.

Für die Instinct-MI300-Familie können die CCDs oder XCDs auf den IOD, der 13 x 29 mm misst, gesetzt werden. Das CCD mit Zen-4-Kernen hat eine Fläche von 70 mm² und ist damit doppelt so groß wie ein SRAM-Chip mit 36 mm². Die CCDs und XCDs werden in 5 nm gefertigt, die IODs in 6 nm. Die TSV-Abstände sind mit 9 µm identisch. Zusammengenommen erreichen die acht XCDs des Instinct MI300X eine Bandbreite von 17 TB/s in dieser vertikalen Integration.

Die Stapelreihenfolge wird auch geändert. Der Speicher sitzt nun im IOD unter dem CCD oder XCD, die ihre Abwärme damit auch deutlich besser abgeben können.

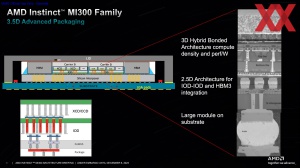

Der Aufbau eines Chips der Instinct-MI300-Familie sieht nun wie folgt aus:

Das Substrat (organisches Package) stellt die unterste Ebene dar. Darauf sitzt der passive Silicon Interposer als Chip on Wafer on Substrate (CoWoS). Auf dem Silicon Interposer sitzen einerseits die IODs, auf denen sich wiederum die XCDs und CCDs befinden und die HBM3-Speicherchips. Dummy-Chips neben den XCDs und CCDs füllen die Lücken, ein sogenanntes Carrier Silicon bringt die Chips auf die gleiche Höhe wie die HBM3-Speicherchips und alles wird mit einem Heatspreader abgedeckt.

AMD kombiniert hier also ein 2.5D-Packaging für den HBM3 mit dem 3D-Hybrid-Packaging um die XCDs und CCDs auf dem IOD aufzubringen und nennt dies im Marketing ein 3.5D-Stacking, wenngleich es diese halbe vierte Dimension natürlich eigentlich nicht gibt.

Die CCDs mit Zen-4-Kernen kommen bereits seit dem vergangenen Jahr in den EPYC-Prozessoren der vierten Generation alias Genoa zum Einsatz. Diese sind nun für den Instinct MI300A identisch und verwenden doch eine andere Anbindung für den Interconnect. AMD hat den Zen-4-CCD also von Beginn an so geplant, dass dieser eine vertikale Integration mittels 3D Bond Pad (BPV) ermöglicht. Ähnlich ist man auch vorgegangen, in dem man die Zen-3- und Zen-4-CCDs auf den Einsatz von 3D V-Cache vorbereitet hat. Zwischen den GMI-PHYs war ausreichend Platz, um hier das 3D Bond Pad unterzubringen.

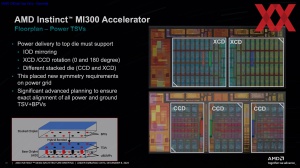

Mehr Komplexität in der Fertigung

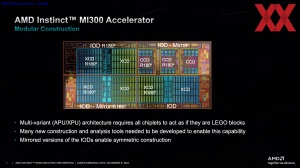

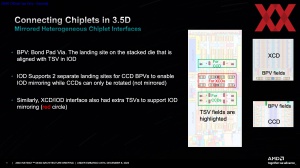

Für das Layout der vier IODs sowie der bis zu acht XCDs und drei CCDs muss AMD diese entsprechend ausrichten, damit die Interfaces für die Interconnects zwischen den IODs und die 3D Bond Pad entsprechend ausgerichtet sind.

Die IODs werden einmal in der Standard-Ausführung und gespiegelt gefertigt. Über eine Rotation der Standard und gespiegelten Ausführung liegen die IODs in einem 2x2 Layout so, dass sie untereinander angebunden werden können.

Die XCDs fertigt AMD in nur einer Ausführung, setzt jeweils zwei zueinander ausgerichtet zusammen auf den IOD, dazu wird ein XCD rotiert. Auch den CCD fertigt man nur in einer Ausführung und rotiert diesen. Zwei rotierte und ein normal ausgerichteter CCDs sitzen auf dem IOD.

Etwas komplexer ist das Layout der 3D Bond Pads.

Jeder IOD sieht in der Mitte zwei Bereiche mit 3D Bond Pads vor, die für die XCDs in normaler und rotierter Ausrichtung vorgesehen sind. Für die CCDs gibt es drei Bereiche mit jeweils zwei Pads auf den IODs.

Neben den TSVs für den Datenaustausch muss es natürlich auch eine Durchkontaktierung für die Strom- und Spannungsversorgung geben. Dazu gibt es drei Pads für den Einsatz von drei CCDs auf einem IOD, von denen im Falle von zwei XCDs auf einem IOD aber nur zwei genutzt werden. Wichtig ist dabei eine entsprechende Auslegung des Power Grids, damit die darunter liegenden Metallschichten weiterhin für eine gleichmäßige Spannungsversorgung sorgen können.

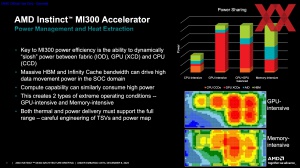

Je nach Workload sind die Anforderungen an das Power Management und die Kühlung höchst unterschiedlich. CPU-intensive Anwendungen belasten im Instinct MI300A nur die CCDs, aber kaum das Speichersystem und nur im geringen Umfang den HBM3. Schon anders sieht dies für GPU-intensive Anwendungen aus, in denen beiden Beschleuniger-Varianten auf ihre 750 W kommen können. Gleiches gilt auch für CPU+GPU-Anwendungen, in denen es eine gewisse Balance zwischen den CCDs und XCDs gibt – im Verhältnis zu deren Anzahl natürlich.

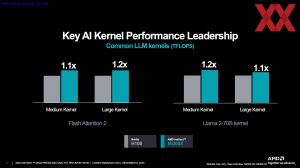

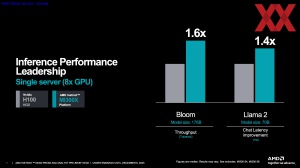

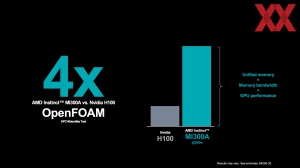

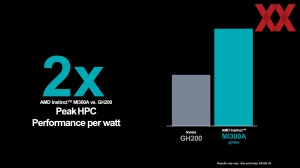

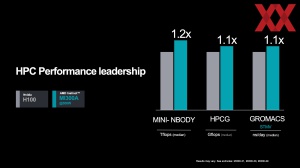

AMDs eigene Benchmarks

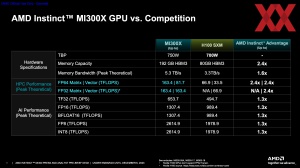

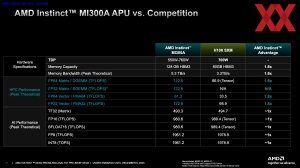

Natürlich präsentierte AMD auch erste, eigene Benchmarks zur Leistung des Instinct MI300X und Instinct MI300A. Zum Vergleich herangezogen, wird vor allem NVIDIAs H100-Beschleuniger, aber auch der Grace Hopper Superchip auf Basis der verfügbaren theoretischen Werte von NVIDIA.

Zunächst verglichen wird die theoretische Rechenleistung. Der große Vorteil der Instinct-MI300-Serie aber ist der Speicherausbau mit 128 GB (Instinct MI300A) und 192 GB (Instinct MI300X). NVIDIA kommt beim H100-Beschleuniger auf 80 GB. Für den 2024 erwarteten H200 sind es 141 GB.

Für die Rechenleistung des Instinct MI300A sieht sich AMD mit einer um 80 % höheren HPC-Rechenleistung im Vorteil. Für den Instinct MI300X sind es eine um 30 % höhere AI-Rechenleistung und eine um den Faktor 2,4 höhere HPC-Rechenleistung mit Unterstützung von Matrix-Operationen.

In einigen Anwendungsbenchmarks vergleicht AMD die Leistung eines Instinct-MI300X-Systems mit acht Beschleunigern gegen ein entsprechen H100-HGX-Server mit ebenfalls acht Beschleunigern. Durch den mehr als doppelt so großen Speicher können KI-Anwendungen sogar um den Faktor 1,6 schneller ausgeführt werden. Nicht mehr nur einen Gleichstand, sondern eine Führungsposition in der Leistung will AMD also erreicht haben.

Der Instinct MI300A zielt eher auf HPC-Anwendungen ab. Auch in diesem Segment sieht man sich zumindest gleichauf, kommen die Speichergröße und Bandbreite zur Rechenleistung hinzu, sollen bestimmte Anwendungen sogar um den Faktor vier schneller bearbeitet werden können. Das Leistung/Watt-Verhältnis will AMD ebenfalls deutlich für sich gewinnen.

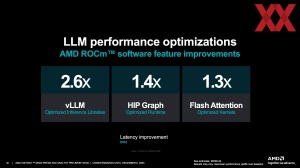

ROCm 6 sorgt für Beschleunigung

Bei der Hardware erreicht AMD immer wieder beeindruckende Lösungen, bei der Software hat sich NVIDIA über Jahre ein Ökosystem aufgebaut, an das die Konkurrenten wie Intel und AMD bisher nicht heranreichen können. Aber natürlich hat man auch hier erkannt, dass eine gute und effiziente Softwareunterstützung ebenso wichtig ist, wie die Hardware selbst.

Zusammen mit der Instinct-MI300-Familie kündigt AMD auch die Einführung von ROCm 6 an. Der dazugehörige Software-Stack soll später im Dezember verfügbar sein und AMD hob einmal mehr hervor, dass ROCm Open-Source ist, während NVIDIAs CUDA zumindest größtenteils auf propritärer Technik beruht. An dieser Stelle sei aber auch erwähnt, dass Intels OneAPI ebenfalls den Open-Source-Ansatz verfolgt.

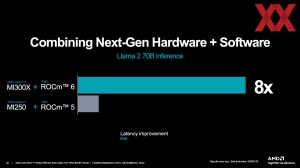

Durch Optimierungen im Software-Stack erreicht AMD mit ROCm 6 ein Leistungsplus um den Faktor 2,6 in optimierten Large Language Models (2,6fach geringerer Latenz) sowie +40 % für den HIP Graph (HIP stellt Portierungswerkzeuge zur Verfügung, die einen Teil der Konvertierung von CUDA-Code in portablen C++-Code übernehmen, der dann wiederum von den HIP-APIs verwendet wird).

Llama 2 mit 70 Milliarden Parametern liefert mit einer Instinct MI300X und ROCm 6 um den Faktor acht geringerer Latenzen als eine Instinct MI250X mit ROCm 5. Die 2,6-fache Verbesserung durch ROCm 6 sollte man hier aber im Hinterkopf haben, um die geringere Latenz an dieser Stelle besser bewerten zu können.

Der Instinct MI300A wird für El Capitan, den geplanten Supercomputer mit einer Rechenleistung von 2 EFLOPS, verwendet werden. Die Installation von El Capitan hatbereits gestartet, im kommenden Jahr soll dieser in den Betrieb gehen.

Die beiden Beschleunigervarianten Instinct MI300X und Instinct MI300A sollen in Kürze von den führenden OEMs in deren Servern angeboten werden. AMDs Ziel dürfte es aber auch sein, die Beschleuniger zu den Cloud-Anbietern zu bringen.

Aus technischer Sicht und rein über die nackten Zahlen zur Hardware ist AMD seinem Konkurrenten NVIDIA überlegen. Ob man dies aber auch schnell und längerfristig in einen Erfolg am Markt wird ummünzen können, steht auf einem anderen Blatt. NVIDIA liefert Monat für Monat tausende H100-Beschleuniger aus. Anfang 2024 hinzukommen sollen die aktualisierten H200-Beschleuniger sowie mit GH200 die Chips mit CPU und GPU, von denen man ebenfalls bereits hunderttausende einplant.

Der Markt ist allerdings auch noch auf absehbare Zeit hungrig nach KI-Hardware und warum sollte AMD nicht bereitstehen, um Kunden, die von NVIDIA nicht beliefert werden können, abzufangen. Oberstes Ziel aber wird sicherlich sein die erste Wahl zu werden. Dazu gehört aber auch das entsprechende Software-Ökosystem und auch hier hat AMD ein paar Neuigkeiten.