Werbung

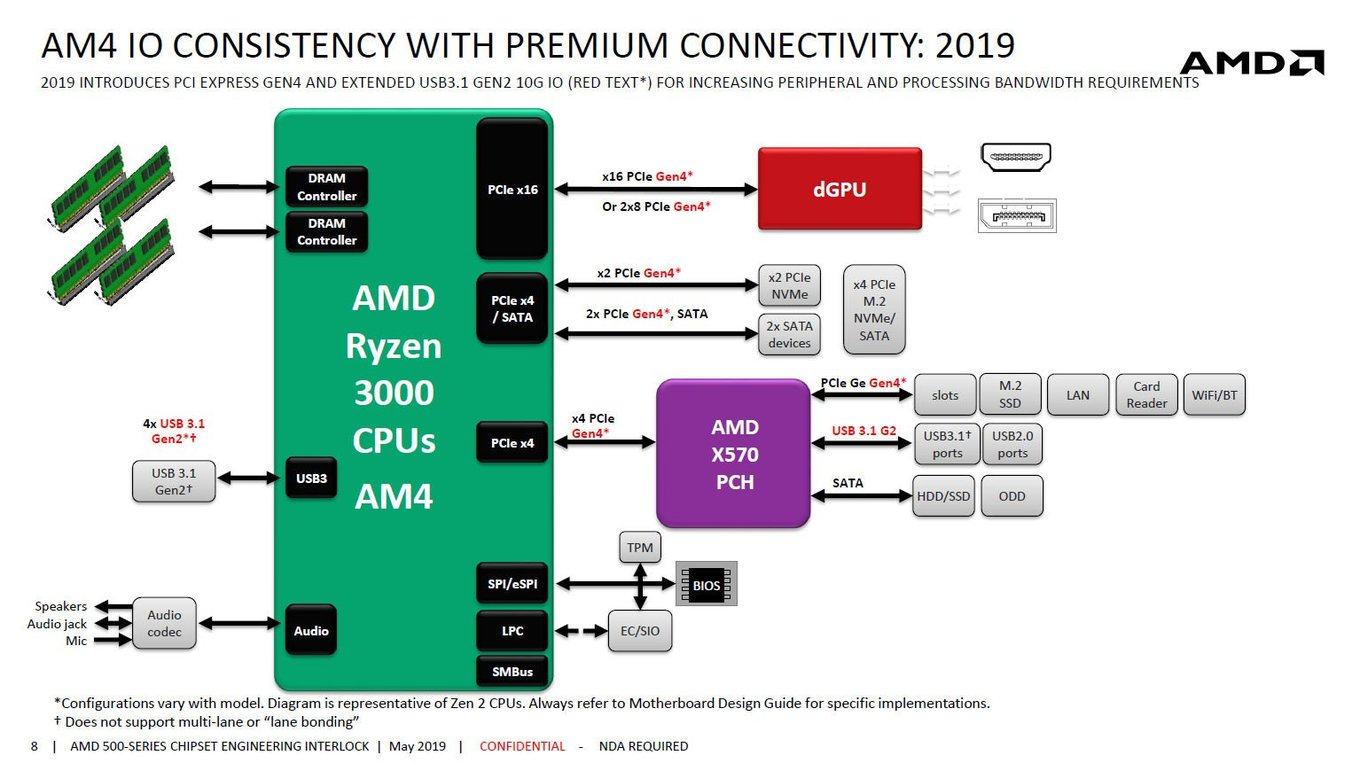

In den vergangenen Tagen gab es viele Details zu den kommenden X570-Mainboards, die zur Computex erwartet werden. Aus einer internen Präsentation stammend ist nun ein Bild des Blockdiagramms aufgetaucht, welches die einzelnen Verbindungen zwischen dem Ryzen-Prozessor, dem Chipsatz und den weiteren Anschlussmöglichkeiten aufzeigt.

Die größte Neuerung der Ryzen-Prozessoren der dritten Generation ist die Tatsache, dass es sich um ein Chiplet-Design handelt. Ein I/O-Die kümmert sich um die internen und externen Datenverbindungen und ein oder zwei CPU-Dies (je nach Modell) auf Basis der Zen-2-Architektur beinhalten die CPU-Kerne. Im Blockdiagramm wird allerdings nur das komplette Package dargestellt. Die gezeigten Anschlüsse werden aber wohl allesamt über den I/O-Die realisiert werden.

Aus technischer Sicht interessant ist die Tatsache, dass alle AMD-Prozessoren auf Basis der Zen-2-Architektur PCI-Express 4.0 unterstützen werden. Das Blockdiagramm zeigt nun die Aufteilung der Lanes, bzw. Anschlüsse. Die Gesamtanzahl an Lanes bleibt mit 1x 16 + 1x 4 plus vier weitere für die Anbindung des Chipsatzes zu den ersten beiden Ryzen-Generationen identisch.

Wie zu erwarten, wird die Grafikkarte, bzw. diskrete GPU über 16 Lanes angebunden. Auch eine Aufteilung in zweimal acht Lanes ist möglich. Für NVMe- und SATA-Laufwerke stehen vier Lanes zur Verfügung, die ebenfalls je nach Bestückung aufgeteilt werden. Zwischen Ryzen-Prozessor und Chipsatz werden ebenfalls vier PCI-Express-Lanes verwendet.

Der Chipsatz wiederum stellt weitere Anschlüsse zur Verfügung, die sich letztendlich immer die vier PCI-Express-Lanes zwischen CPU und Chipsatz teilen müssen. Das Blockdiagramm spricht von weiteren PCI-Express-4.0-Anschlüssen, die vom Chipsatz abgehen. Hinzu kommen USB 3.1 Gen 2 und SATA. Über deren Anzahl macht das Schaubild keine Informationen.

Neben den PCI-Express-Lanes sind am Ryzen-Prozessor auch noch viermal USB 3.1 Gen 2 angebunden. Hinzu kommen das Dual-Channel-Speicherinterface sowie Protokolle wie SPI, LPC und SMBus für die Kommunikation zwischen dem Prozessor und dem BIOS.

Die Präsentation stammt offenbar vom Mai 2019 und stellt eine Art Referenzimplementation dar. Je nach Mainboard können die Lanes und Anschlüsse auch anders aufgeteilt werden. Zur Computex werden wir zahlreiche Interpretationen dessen sehen, was oben im Blockdiagramm schematisch dargestellt ist.