Werbung

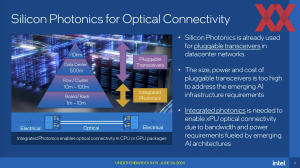

Schon seit Jahrzehnten spricht Intel über die Entwicklung einer optischen Übertragung von Daten im Nah- und Fernbereich. Tatsächlich ist Silicon Photonics in Netzwerkumgebungen bereits im Einsatz und das schon seit Jahren. Doch bisher gab es noch kein entscheidendes Unterscheidungsmerkmal zu anderen Übertragungen auf Basis von Lichtwellenleitern – zumindest keine besonders prominenten.

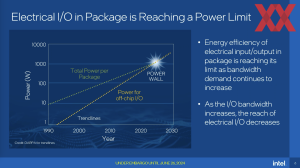

Mit der Integration einer optischen Verbindung direkt in die Chips, bzw. das Package will Intel viele der aktuellen Beschränkungen im Bereich der Netzwerkverbindungen umgehen: Bandbreite und Leistungsaufnahme. Ein wichtiger Vorteil in der Kommunikation via Lichtwellenleiter ist die Effizienz im Hinblick auf den Energieverbrauch. Schaut man sich den Anteil der Leistungsaufnahme im Datentransfer, bzw. der I/O-Leistung in aktuellen Prozessoren, GPU-Beschleunigern, AI-Systemen und Supercomputern an, dann erreicht diese bereits einen Anteil von 30 bis 40 %. Auf der anderen Seite bedeutet dies, dass nur noch 60 % für die eigentlichen Recheneinheiten zur Verfügung stehen.

Aktuell wird eine hohe Bandbreite im Nahbereich noch immer über Kupferleitungen und damit über die Übertragung von elektrischen Signalen realisiert. Die Zukunft sollen optoelektronische Verbindungen sein – so wie eben Silicon Photonics. Wie weit man mit einfachen elektrischen Interconnects kommt, zeigt NVIDIA mit dem GB200 NVL72. Hier werden insgesamt 36 Grace-CPUs und 72 Blackwell-GPUs per NVLink mit jeweils 1,8 TB/s über einen Spine miteinander verbunden. Insgesamt sprechen wir also von einer Interconnect-Bandbreite von 130 TB/s auf Rackebene. Bereits 2020 verkündete NVIDIA, dass man ebenfalls an einem Co-Packaged Photonics für NVLink arbeite. AMD und einige Partner wollen schnelle Verbindungen mittels Accelerator Fabric Link (AFL) ermöglichen.

Allen beteiligten Unternehmen ist also klar, dass früher oder später eine direkte Übertragung von elektrischen Signalen unzureichend sein wird. Über technisch ausgereifte Optimierungsschritte konnte der Wechsel auf optoelektronische Verbindungen bisher hinausgezögert werden.

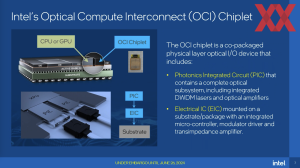

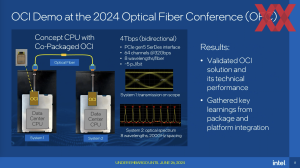

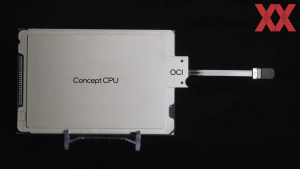

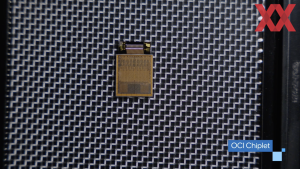

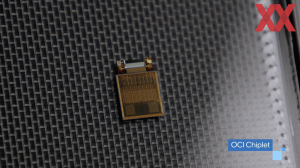

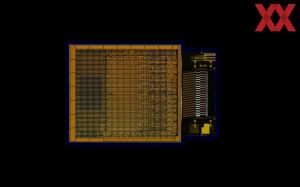

Ende Juni 2022 bereits detaillierte ausgeführt, verkündet Intel nun auf der Optical Fiber Conference (OFC) 2024: Das Chiplet für einen Optical Compute Interconnect (OCI) soll nun endlich Realität werden. Das Chiplet besteht wiederum aus zwei Einzelchips: Einem Photonic Integrated Circuit (PIC) und einem Electrical Integrated Circuit (EIC).

Der PIC enthält die optischen Subsysteme wie den SWDM-Laser und die optischen Verstärker. Der EIC wiederum sitzt direkt auf dem Substrat, bzw. verbindet das OCI mit dem restlichen Package. Im Falle der ersten Umsetzung wird diese Anbindung mittels PCI-Express 5.0 geschehen. Intel wird also das PCI-Express-Interface des Host-Chips nutzen, um den OCI anzubinden. Dies geschieht laut Intel aus einem einfachen Grund: Die meisten Prozessoren oder Beschleuniger verfügen bereits über ein PCI-Express-Interface und daher lässt sich der OCI daran am besten anbinden.

Allerdings hat diese Art der Anbindung ein paar Nachteile: So erreicht Intel "nur" 4 TBit/s bidirektional – sprich 256 GB/s in Sende- und Empfangsrichtung. Zur Anbindung des OCI wird wie gesagt das PCI-Express-Interface des Host-Prozessors verwendet und damit die 256 GB/s je Richtung erreicht werden können, müssen auch die vollen 64 PCIe-5.0-Lanes bzw. SerDes verwendet werden.

Eine einzelne NVLink-Verbindung, wie sie mit den Blackwell-Beschleunigern zum Einsatz kommen wird, erreicht 1,8 TB/s (18 Links mit jeweils vier Lanes bei 25 GB/s) und verfügt damit über eine dreimal so hohe Bandbreite. NVIDIA realisiert dies wie gesagt noch über viele parallele Kupferverbindungen. Den richtigen Punkt zu finden, an dem sich die Lichtwellenleiter lohnen, muss also sehr individuell gefunden werden. Intel geht aktuell davon aus, dass Silicon Photonics auf Board- und Rackebene zum Einsatz kommen wird und hier die elektrischen Verbindungen ersetzen kann. Darüber hinaus sind es ohnehin schon optoelektronische Verbindungen – sogenannte Silizium-Photonik-Transceiver bietet Intel schon seit geraumer Zeit an.

Die Effizienz ist der zweite wichtige Faktor und hier kommt Intel auf etwa 5 pJ/Bit. Für OCI angepeilte waren einmal 3 pJ/Bit, allerdings musste man diese Zielvorgabe etwas lockern, was auch damit zu tun hat, dass nun das PCI-Express-Interface als Schnittstelle hinzukommt. Zukünftig soll der OCI noch effizienter in der Übertragung werden.

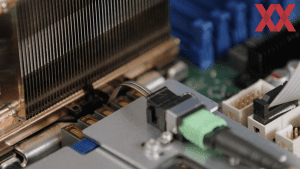

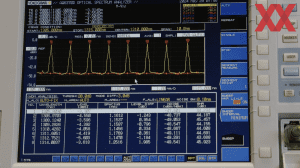

Auf der OFC 2024 demonstriert wurde eine optische Verbindung in Form einer Sender- und Empfänger-Verbindung zwischen zwei Prozessor-Plattformen über ein SMF-Patchkabel (Single-Mode-Fiber). Die Prozessoren generieren und messen die optische Bitfehlerrate (BER) und gezeigt wird das optische Spektrum des Senders mit acht Trägerwellen im Abstand von 200 GHz auf einer Faser. Über eine Strecke von bis zu 100 m soll dies in dieser Form möglich sein.

Es soll nur der Anfang sein

Die erste Umsetzung des Optical Compute Interconnect muss noch einige Kompromisse eingehen. Die Anbindung über das PCI-Express-Interface ist einer dieser. Die Bandbreite von 256 GB/s ist ein weiterer, denn im Nahbereich sind bereits 1 TB/s und mehr möglich.

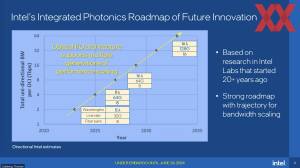

Laut Intel hat man eine langfristige Roadmap, die beide Punkte angehen soll. So kann die Anbindung des OCI zukünftig über ein natives Interface erfolgen und nicht mehr per PCI-Express.

Außerdem bietet die Übertragung über Lichtwellenleiter ein hohes Skalierungspotential. Aktuell verwendet Intel acht Trägerwelle, künftig sollen es dann 16 sein und selbst die Bandbreite pro Trägerwelle soll verdoppelt werden. So kann die Gesamtbandbreite dann beispielsweise recht einfach vervierfacht und weiter in die Höhe getrieben werden.

Hier reden wir jedoch von Entwicklungen in 2030 und 2035 – es ist also noch ein weiter Weg. Zunächst einmal sind wir gespannt, in welchen Chips oder Packages wir den Optical Compute Interconnect sehen werden. Intel zeigt das Chiplet meist auf Basis eines Xeon-Prozessors. Aber auch die Falcon-Shores-XPUs wären ein Kandidat.